Table of contents

1. Algorithm simulation effect

2. Algorithms involve an overview of theoretical knowledge

4. Complete algorithm code file

1. Algorithm simulation effect

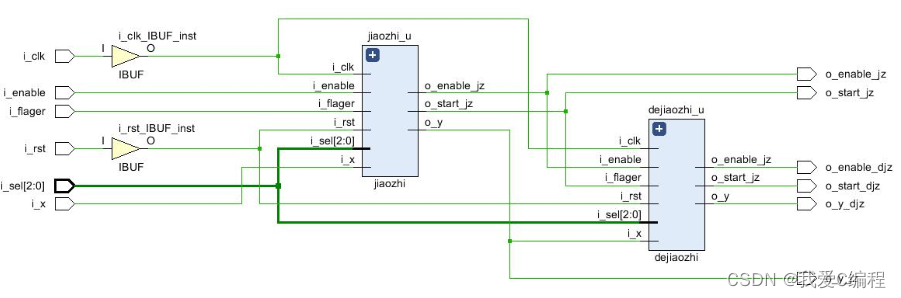

The Vivado2019.2 simulation results are as follows:

2. Algorithms involve an overview of theoretical knowledge

Interleaving and deinterleaving system is a data transmission technology widely used in communication systems to improve the reliability and anti-interference ability of data transmission. The system interleaves the data at the sending end, and then performs deinterleaving at the receiving end, so that each bit of the data is scattered to different positions, thereby reducing the influence of channel noise and interference and improving the reliability of data transmission.

Specifically, the working process of the interleaving and deinterleaving system is as follows:

Interleaving: Interleave the data at the sending end according to certain rules, and disperse each bit of the data to different positions.

Coding: Coding the interleaved data to improve the reliability of data transmission. Common encoding methods include convolutional codes, correction codes, etc.

Modulation: Modulate the coded data to adapt to the characteristics of channel transmission. Common modulation methods include ASK, FSK, PSK, etc.

Transmission: The modulated data is transmitted to the receiving end through the channel.

Demodulation: Demodulate the transmitted signal at the receiving end to obtain the digital signal at the receiving end.

Decoding: Decode the digital signal at the receiving end to restore the original data. The decoding process needs to consider the influence of channel noise and interference.

De-interleaving: The decoded data is de-interleaved according to the rule opposite to the interleaving rule, and the order of the original data is restored.

The above is the basic principle of the interleaving and deinterleaving system. Below we will introduce how to implement the interleaving and deinterleaving system in FPGA.

The general steps for FPGA to realize the interleaving and deinterleaving system are as follows:

Design interleaving rules: The interleaving rules are the core of interleaving processing, which determine the interleaving sequence and mode of data. In practical applications, appropriate interleaving rules need to be designed according to specific situations.

Design the interleaving module: the interleaving module is the core of the whole interleaving and deinterleaving system, which implements the interleaving rules. The interleaving module usually includes a buffer and an interleaver. The buffer area is used to store input data, and the interleaver is used to implement interleaving rules.

Design the de-interleaving module: The de-interleaving module is similar to the interleaving module, but it needs to implement the opposite rule to the interleaving rule to restore the order of the original data.

Design the encoding module: the encoding module is used to encode the interleaved data to improve the reliability of data transmission. Common encoding methods include convolutional codes, correction codes, etc.

Design the modulation module: the modulation module is used to modulate the coded data to adapt to the characteristics of channel transmission. Common modulation methods include ASK, FSK, PSK, etc.

Design the demodulation module: The demodulation module is used to demodulate the transmitted signal at the receiving end to obtain the digital signal at the receiving end.

Design the decoding module: the decoding module is used to decode the digital signal at the receiving end to restore the original data. The decoding process needs to consider the influence of channel noise and interference.

Design the de-interleaving module: The de-interleaving module is used to de-interleave the decoded data according to the opposite rule to the interleaving rule, and restore the order of the original data.

Design control module: The control module is used to control the workflow of the entire interleaving and deinterleaving system, including data input and output, start and stop of modules, etc.

The above is the general steps to realize the interleaving and deinterleaving system in FPGA. In practical applications, it needs to be adjusted and optimized according to the specific situation.

The interleaving and deinterleaving system is a data transmission technology that can improve the reliability and anti-interference ability of data transmission. Implementing interleaving and deinterleaving system in FPGA needs to design interleaving rules, interleaving module, deinterleaving module, encoding module, modulation module, demodulation module, decoding module, deinterleaving module and control module and other modules. FPGA has the advantages of programmability and high parallelism, and has certain advantages in realizing interleaving and deinterleaving systems. In practical applications, it needs to be adjusted and optimized according to the specific situation.

In this project, we mainly develop separate interleaving and deinterleaving modules.

3. Verilog core program

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/12 19:58:30

// Design Name:

// Module Name: tops

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops(

input i_clk,

input i_rst,

input [2:0]i_sel,//配置2*2交织和4*4交织

input i_flager,

input i_enable,

input i_x,

output o_y_jz,

output o_enable_jz,

output o_start_jz,

output o_y_djz,

output o_enable_djz,

output o_start_djz

);

//交织

jiaozhi jiaozhi_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//配置2*2交织和4*4交织

.i_flager (i_flager),

.i_enable (i_enable),

.i_x (i_x),

.o_y (o_y_jz),

.o_enable_jz (o_enable_jz),

.o_start_jz (o_start_jz)

);

//解交织

dejiaozhi dejiaozhi_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_sel (i_sel),//配置2*2交织和4*4交织

.i_flager (o_start_jz),

.i_enable (o_enable_jz),

.i_x (o_y_jz),

.o_y (o_y_djz),

.o_enable_jz (o_enable_djz),

.o_start_jz (o_start_djz)

);

endmodule

00_014m4. Complete algorithm code file

V