Table of contents

Three, verilog core simulation

Fourth, the simulation conclusion analysis

1. Theoretical basis

The whole program is divided into the following three parts:

·Clock control part, divided into adjustment minutes, seconds function, second reset function;

Pause function, clock counting stop function;

4-digit digital tube display function;

The system buttons are: quick adjustment button, reset, second reset button, system pause button (two functions of work and pause are available)

So four buttons are needed.

2. Case background

1. Problem description

The basic block diagram of the entire system is shown below:

2. Thought process

·Key debounce is mainly realized by the function of delay, and it often takes a long time to delay the actual loading of the board, so our code provides you with two versions of the code, one version is the simulation version, without cancelling Jitter, one version is the hardware version, with the function of debounce.

·The simulation version mainly considers the function of the system, so we directly control the clock system; in the hardware version, we need to divide the system clock frequency in order to get the clock corresponding to 1 second.

Three, verilog core simulation

The top program is as follows:

module time_module(

i_clk, //系统时钟

//这里假设按键的初始状态为0,按下后为1

i_rst, //系统复位

i_min_fast,//调整分

i_sec_fast,//调整秒

i_stop_run,//暂停或者继续工作

o_min, //显示分

o_sec //显示秒

);

input i_clk;

input i_rst;

input i_min_fast;

input i_sec_fast;

input i_stop_run;

output[7:0]o_min;

output[7:0]o_sec;

reg[7:0]o_min = 8'd0;

reg[7:0]o_sec = 8'd0;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_min <= 8'd0;//59

o_sec <= 8'd0;//59

end

else begin

if(i_stop_run == 0)//不按下时为0,时钟正常工作

begin

//正常计时间

if(o_sec[3:0] == 4'd9)

begin

o_sec[3:0] <= 4'd0;

if(o_sec[7:4] == 4'd5)

begin

o_sec[7:4] <= 4'd0;

//分计数

if(o_min[3:0] == 4'd9)

begin

o_min[3:0] <= 4'd0;

if(o_min[7:4] == 4'd5)

begin

o_min[7:4] <= 4'd0;

end

else begin

o_min[7:4] <= o_min[7:4] + 4'd1;

end

end

else begin

o_min[3:0] <= o_min[3:0] + 4'd1;

end

end

else begin

o_sec[7:4] <= o_sec[7:4] + 4'd1;

end

end

else begin

o_sec[3:0] <= o_sec[3:0] + 4'd1;

end

//调整时间

if(i_min_fast == 1'b1)

begin

if(o_min[3:0] == 4'd9)

begin

o_min[3:0] <= 4'd0;

if(o_min[7:4] == 4'd5)

begin

o_min[7:4] <= 4'd0;

end

else begin

o_min[7:4] <= o_min[7:4] + 4'd1;

end

end

else begin

o_min[3:0] <= o_min[3:0] + 4'd1;

end

end

if(i_sec_fast == 1'b1)

begin

o_sec <= 8'd0;

end

end

else begin//按下时为1,时钟停止

o_min <= o_min;

o_sec <= o_sec;

end

end

end

endmodule

Fourth, the simulation conclusion analysis

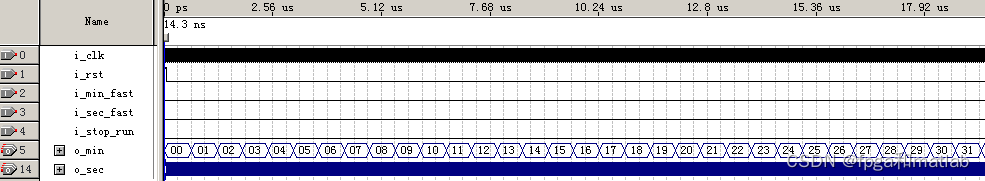

The simulation results are as follows:

normal operation:

As you can see in the figure above, when the second count reaches 59, it becomes 0, and then the minute number increases by 1;

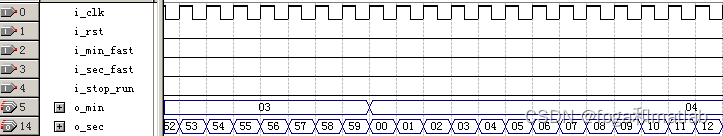

Adjustment:

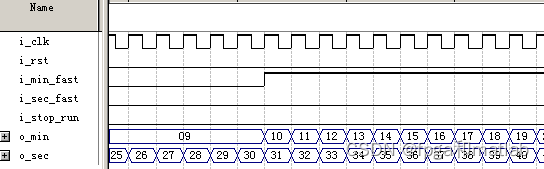

Point adjustment:

When the minute adjustment button is pressed, the minute starts to count quickly, which is the same as the actual electronic watch.

Second adjustment:

When the second adjustment button is pressed, the second changes to 0.

pause:

Stop walking when pause is pressed.

Reset:

After reset, the system becomes 0; A02-36