Senior original link:

https://blog.csdn.net/kuan__/article/details/126184692

https://blog.csdn.net/kuan__/article/details/124392567

foreword

Why avoid latches in digital IC design?

When I was in school, the teacher said that the judgment statement should write all the conditions, otherwise the latch will be generated. When doing the project, he also said that the assignment of the multi-bit register signal must add an if condition to prevent the assignment of the else. It is very contradictory. This article mainly talks about what is a latch, under what circumstances will a latch appear, and the hazards of a latch.

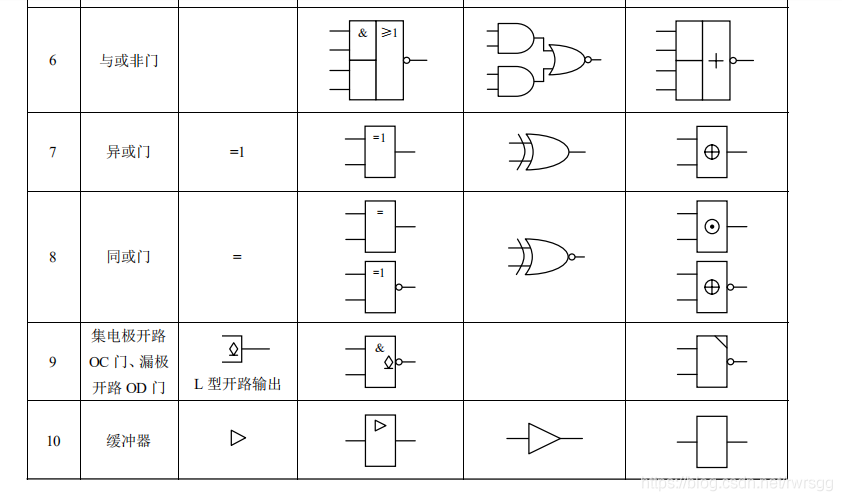

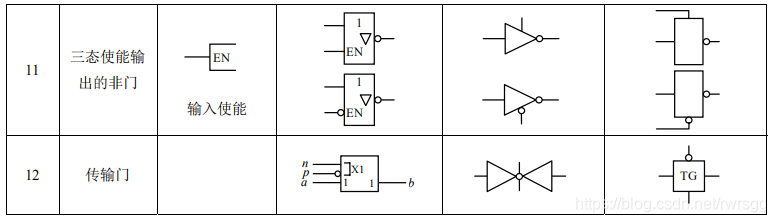

Basic logic gate circuit graphic symbols

The relationship and difference between zero, latch, D flip-flop and register

foreword

In digital IC design, there are often latches, D flip-flops and registers. Many people (such as me) can't tell the difference and don't understand the difference between them. This blog mainly explains the working principle of latches, D flip-flops and registers as well as their relationship and differences.

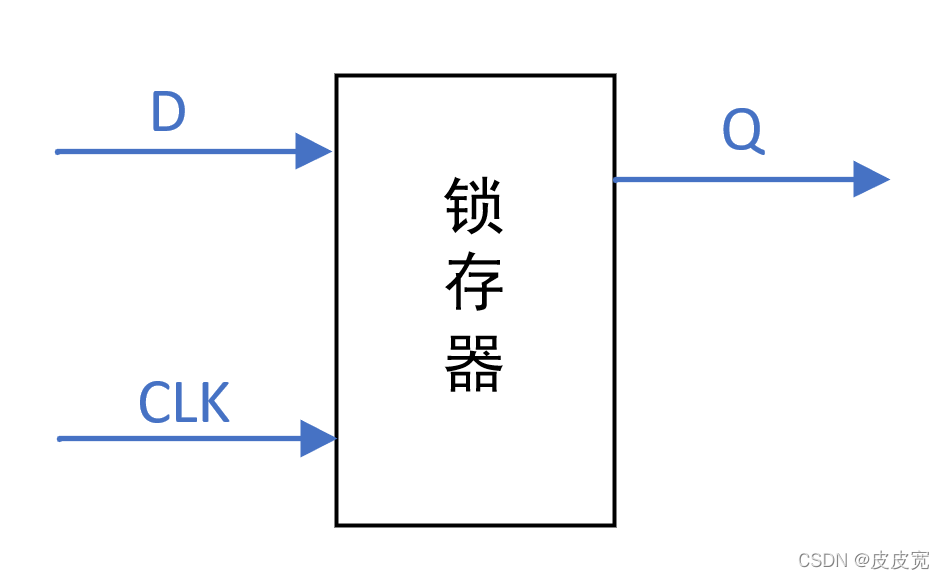

1. Latches

A latch (Latch) is a memory cell circuit that is sensitive to pulse levels, and they can change states under the action of a specific input pulse level [1]. In other words, if a module's input information is updated to its output pins only under the action of a certain level, otherwise the output of the module will remain unchanged, then this module can be regarded as a Latches.

for example:

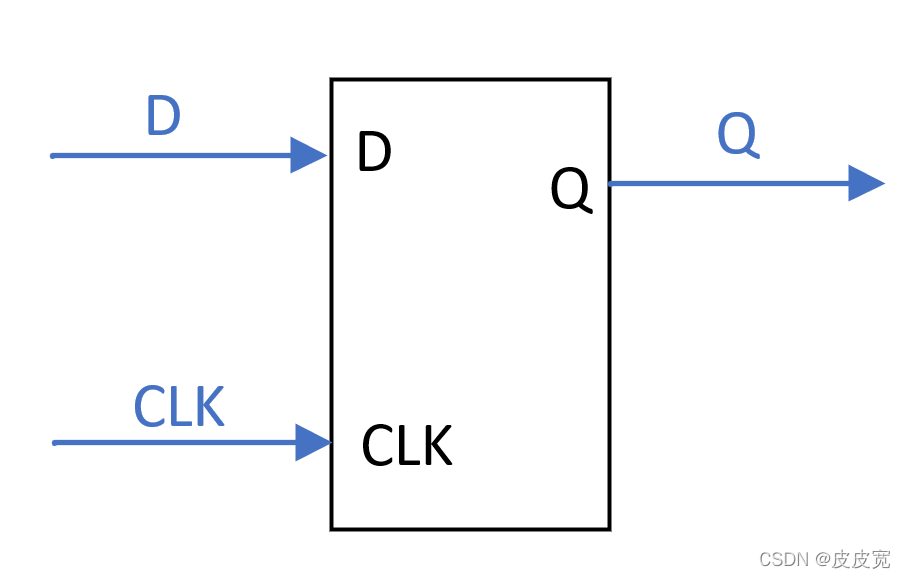

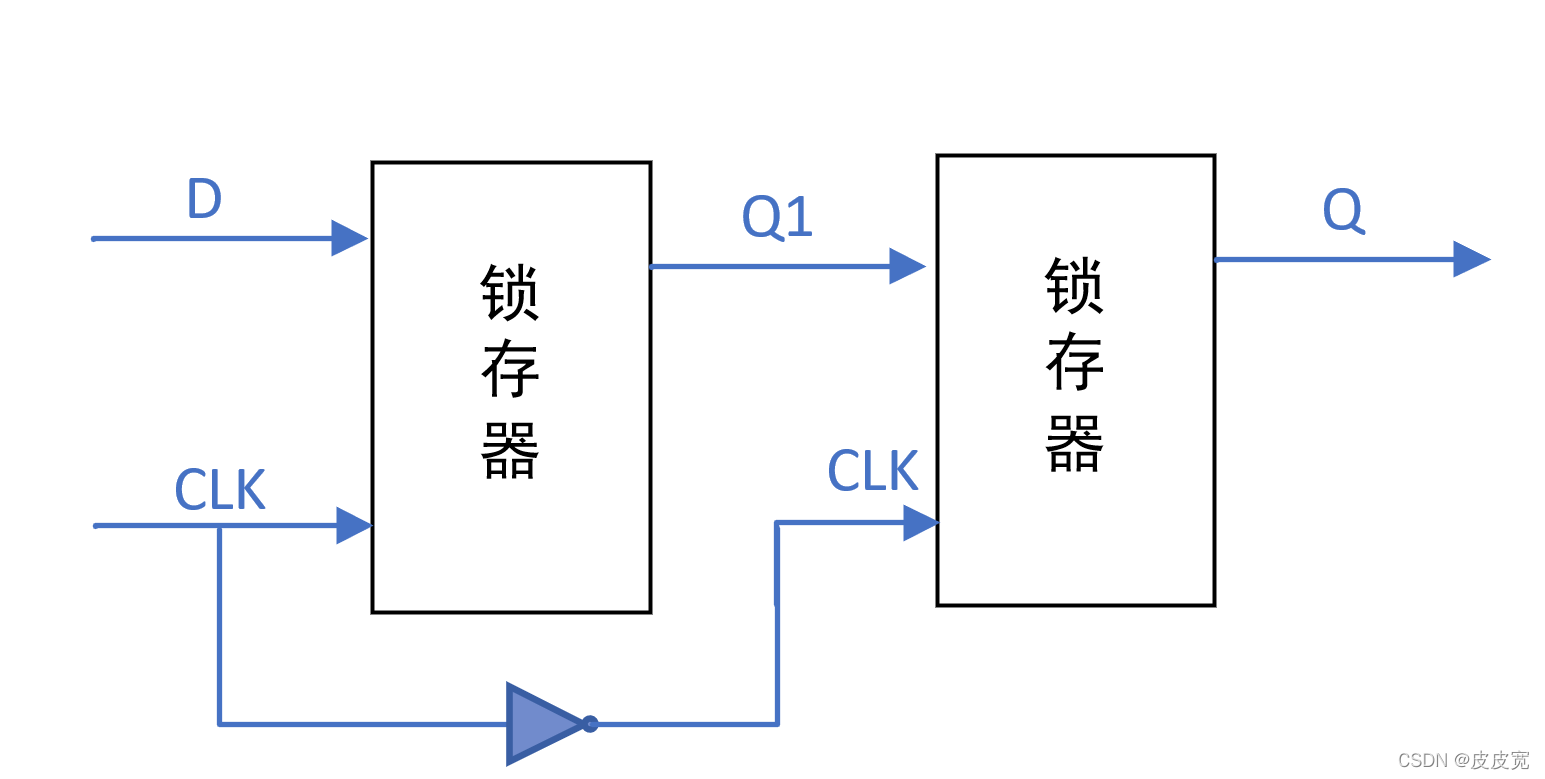

Second, the latch builds a D flip-flop

The figure is a schematic diagram of a D flip-flop. When CLK inputs a rising edge, the input at the D terminal is transferred to Q. When CLK does not input a rising edge, Q remains unchanged.

As shown in the figure, when CLK = 0, Q1=D; when CLK=1, Q=Q1; that is, when the rising edge of CLK comes, the D signal is transmitted to the Q terminal, so the two latches The device constitutes a D flip-flop;

3. What is a register?

Register is a very important storage unit in integrated circuits, usually composed of flip-flops , registers are high-speed storage components with limited storage capacity , they can be used to temporarily store instructions, data and addresses [2]. In other words, those with the function of caching data can be called registers , and registers are often used in CPUs, so they are edge-sensitive devices.

The D flip-flop has the function of caching data . When the rising edge of CLK is input, D is transferred to Q, and then Q will remain unchanged until the next rising edge of CLK arrives. Therefore, the D flip-flop can be used as a register, that is (D flip-flop ∈ register), the change of the latch state is related to a specific level (high level and low level), and the state change of the register often requires an edge signal (rising edge and falling edges), so the latch ∉ \notin∈/Registers, since two latches can build an edge-sensitive flip-flop (as shown in the previous section), latches can build registers.

Four. Summary

- Latches are level-sensitive devices, while D flip-flops and registers are edge-sensitive devices;

- Two latches can build a D flip-flop;

- D flip-flops belong to registers;

1. What is a latch?

A latch (Latch) is a memory cell circuit that is sensitive to pulse levels , and they can change states under the action of a specific input pulse level [1].

In other words, if a module's input information is updated to its output pins only under the action of a certain level, otherwise the output of the module will remain unchanged, then this module can be regarded as a Latches.

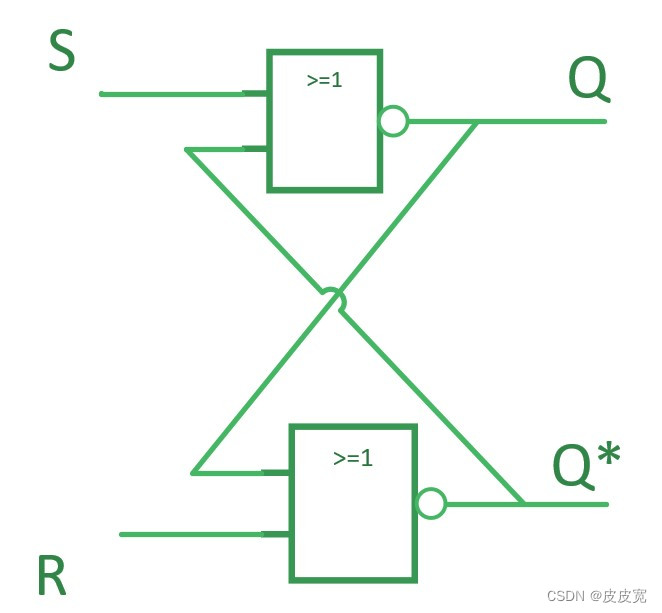

The structure of a common SR register is as follows:

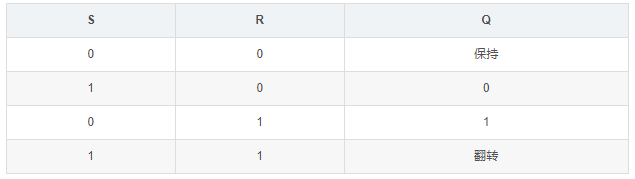

The truth table is

Since S and R are 00, the output Q can be kept unchanged, so as to achieve the purpose of using combinational logic to realize storage;

2. Under what circumstances will a latch appear?

Due to the existence of registers , sequential logic does not need latches to store data; while the conditions of combinational logic are not given full time, latches will appear ;

always@(*)

if(vld)

a = b;

At this time, since there is no case where vld is written to 0, it will not be instantiated into a selector for choosing one of two, but will be instantiated into a latch to achieve the storage function of keeping the data unchanged when vld is 0;

3. Why avoid latches?

Latches have the following disadvantages:

- Cannot be reset asynchronously and is in an indeterminate state after power-on.

- Latches can make static timing analysis very complicated;

- If it is to build a circuit on FPGA, since the basic unit in FPGA is composed of look-up table and flip-flop, generating a latch requires more resources;

- The latch is sensitive to burrs, which will cause circuit instability (I didn't want to understand this, can instantiation into a selector solve this problem??)

—————————————————