STM32F1xx official information:

"STM32 Chinese Reference Manual V10" - Chapter 17 Independent Watchdog

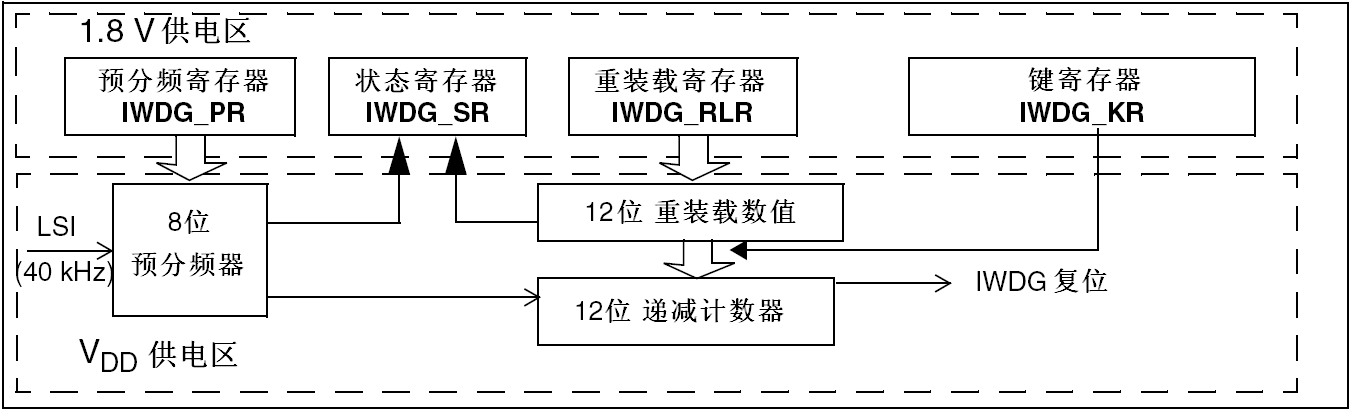

Standalone Watchdog Overview

Definition of watchdog

In a microcomputer system composed of a single-chip microcomputer, the work of the single-chip microcomputer is often disturbed by the external electromagnetic field, causing the program to run away and fall into an infinite loop; or the normal operation of the program is interrupted, and the system controlled by the single-chip microcomputer cannot continue. Work will cause the entire system to fall into a stagnant state and have unforeseen consequences. Therefore , for the consideration of real-time monitoring of the running state of the single-chip microcomputer, a module or chip specially used to monitor the running state of the single-chip microcomputer program is produced, commonly known as "watchdog".

To put it simply: the function of the watchdog is to realize the automatic reset restart of the processor (send a reset signal) if it does not receive the dog feeding signal within a certain period of time (implemented by a timer counter) (indicating that the MCU has hung up).

The role and requirements of the watchdog:

- In the case of the system running away (the program is executed abnormally), the system is reset and the program is re-executed;

- During normal operation, the system cannot be reset.

STM32's built-in watchdog

STM32 has two built-in watchdogs, providing higher security, time accuracy and flexibility of use. Two watchdog devices (independent watchdog, windowed watchdog) can be used to detect and resolve faults caused by software errors. When the counter reaches the given timeout value, trigger an interrupt (window watchdog only) or generate a system reset.

- The independent watchdog (IWDG) is driven by a dedicated low-speed clock (LSI) (40kHz), and it remains active even if the main clock fails. The independent watchdog is suitable for applications where the watchdog is required to work completely independently outside the main program, and the time precision is low.

- The window watchdog is driven by a clock divided from the APB1 clock (36MHz). Detect abnormally late or premature application operation through a configurable time window. Windowed watchdogs are best suited for programs that require the watchdog to function in a precisely timed window.

Function of independent watchdog

- Write 0xCCCC in the key value register (IWDG_KR) to start enabling the independent watchdog . At this time, the counter starts to decrement from its reset value 0xFFF , and a reset signal (IWDG_RESET) is generated when the counter value counts to the last value 0x000.

- Whenever 0xAAAA (usually said to feed the dog) is written in the key-value register IWDG_KR, the value of the auto-reload register IWDG_RLR will be reloaded to the counter, thus avoiding the watchdog reset.

- If the program is abnormal, the dog cannot be fed normally, and the system is reset.

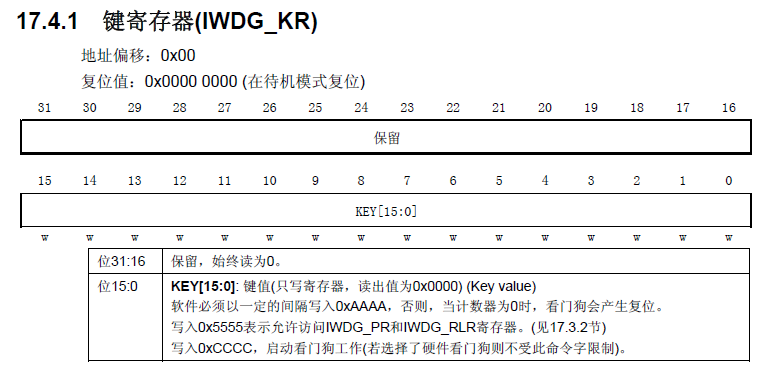

Note: The IWDG_PR and IWDG_RLR registers are write protected. To modify the value of these two registers, you must first write 0x5555 to the IWDG_KR register. Writing to this register with a different value will shuffle the sequence of operations and the register will be reprotected. A reload operation (ie, writing 0xAAAA) also enables write protection.

Independent watchdog related configuration registers

Key Register (IWDG_KR)

Function: write 0xAAAA, keep feeding the dog to avoid reset; write 0x5555 to allow access to the IWDG_PR and IWDG_RLR registers; write 0xCCCC to start the watchdog work (if the hardware watchdog is selected, it is not restricted by this command word ). The initial reset value is decremented from 0xFFF, and then decremented from the value of the reload register after feeding the dog.

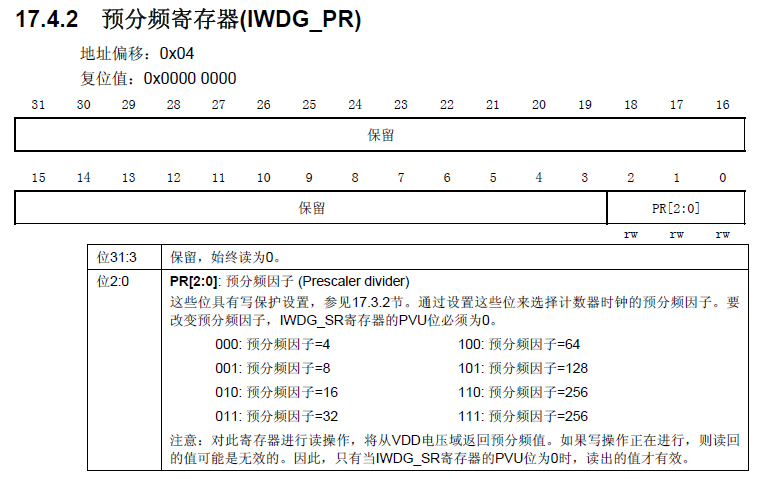

Prescaler Register (IWDG_PR)

Function: divide the clock frequency.

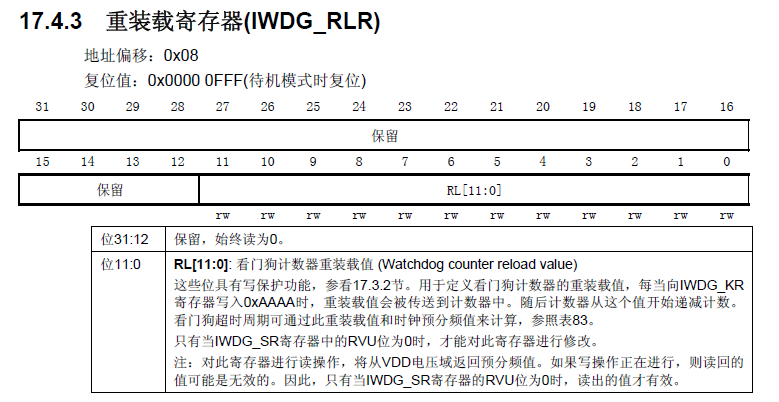

Reload Register (IWDG_RLR)

Function: used to define the reload value of the watchdog counter. Whenever 0xAAAA is written to the IWDG_KR register, the reload value will be transferred to the counter. The counter then counts down from this value.

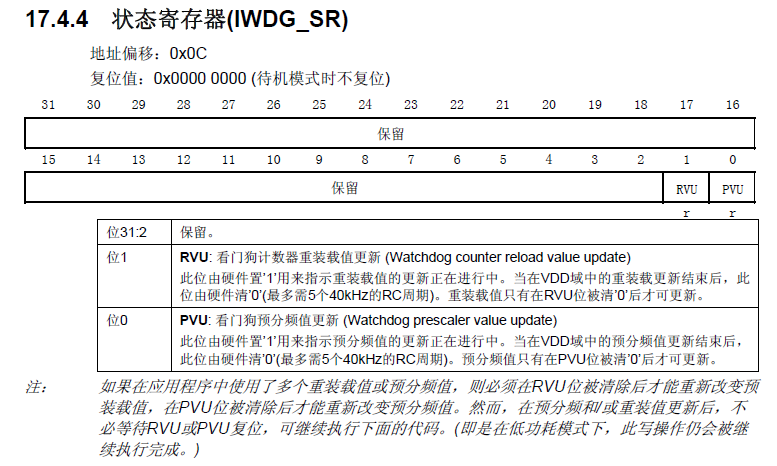

Status Register (IWDG_SR)

Function: Monitor the status of preload value update and prescaler value update.

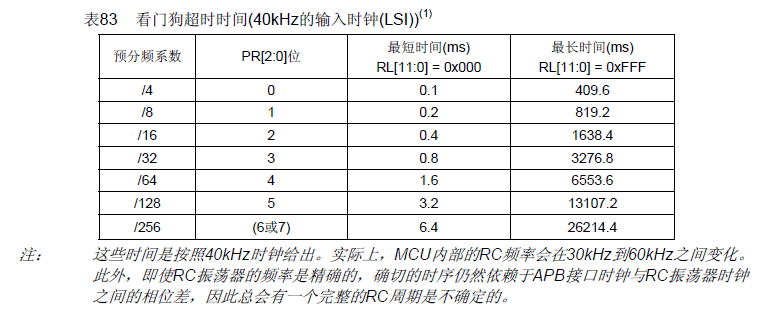

Independent watchdog timeout

Exceeded (overflow) time calculation:

All=((4×2^PR)×RLR)/40

Where: Tout is in milliseconds.

Clock frequency LSI=40K, one watchdog clock cycle is the shortest timeout time. Maximum timeout = (IWDG_RLR register maximum value) X watchdog clock cycles.

For example, if you want to set the overtime to 1s (that is, if the dog is not fed within 1s, it will be reset directly), set the prescale factor to 64 (that is, the PR bit is 4, that is, [2:0] bit is 100), from which the RLR can be calculated to be 625.

That is to say, when the clock signal is 40kHz and the prescale factor is 64, the event of decrementing from 625 to 0 is 1s.

Independent watchdog related configuration library functions

- 2 initialization functions

void IWDG_WriteAccessCmd(uint16_t IWDG_WriteAccess); void IWDG_Enable(void);

Function: The former cancels the write protection function of the IWDG_PR and IWDG_RLR registers (0x5555 is enabled), and the latter enables the watchdog (write 0xCCCC to KR) .

One thing to note here: Once IWDG is started, it cannot be turned off! If you want to close it, you can only restart it, and you cannot open it again after restarting.

- 2 parameter setting functions

void IWDG_SetPrescaler(uint8_t IWDG_Prescaler); void IWDG_SetReload(uint16_t Reload);

Function: The former sets the prescaler coefficient, the latter sets the reload value.

- 1 feeding dog function

void IWDG_ReloadCounter(void);

Function: keep feeding the dog and avoid reset (write 0xAAAA to KR).

Independent watchdog general steps

- Cancel register write protection. Call function: IWDG_WriteAccessCmd();

- Set the prescale factor of the independent watchdog to determine the clock. Call function: IWDG_SetPrescaler();

- Set watchdog reload value (determined by overflow time). Call function: IWDG_SetReload();

- Enable watchdog. Call function: IWDG_Enable();

- App to feed the dog. Call function: IWDG_ReloadCounter().

The following general steps are followed for a simple stand-alone watchdog program:

//Initialize independent watchdog

//prer: Frequency division: 0~7 (only the lower 3 bits are valid!)

//Frequency division factor=4*2^prer. But the maximum value can only be 256!

//rlr: reload register value: the lower 11 bits are valid.

//Time calculation (approximately): Tout=((4*2^prer)*rlr)/40 (ms).

void IWDG_Init(u8 prer,u16 rlr)

{

IWDG_WriteAccessCmd(IWDG_WriteAccess_Enable); //Enable write operations to registers IWDG_PR and IWDG_RLR

IWDG_SetPrescaler(prer); //Set the IWDG prescaler value: set the IWDG prescaler value to 64

IWDG_SetReload(rlr); //Set IWDG reload value

IWDG_ReloadCounter(); //Reload the IWDG counter according to the value of the IWDG reload register

IWDG_Enable(); //Enable IWDG

}

// feed the independent watchdog

void IWDG_Feed(void)

{

IWDG_ReloadCounter();//reload

}

int main(void)

{

delay_init(); //Delay function initialization

LED_Init(); //Initialize the hardware interface connected to the LED

KEY_Init(); //Key initialization

delay_ms(500); // let people see it off

IWDG_Init(4,625); //And the frequency division is 64, the reload value is 625, and the overflow time is 1s

LED0=0; //Light up LED0

while(1)

{

if(KEY_Scan(0)==WKUP_PRES)

{

IWDG_Feed();//If WK_UP is pressed, feed the dog

}

delay_ms(10);

};

}