参考教材:数字电路与逻辑设计(第2版)邬春明

目录

1. 组合逻辑电路分析

组合逻辑电路分析:给一张电路图,逆推出其逻辑表达式,列出真值表,然后分析出其功能

2. 组合逻辑电路设计( 重点,设计视角,以练题为主)

根据功能描述,直接写出逻辑表达式(通过逻辑思维),或者先写出真值表(简单粗暴)再写出逻辑表达式随后通过卡诺图化简。直接写出的逻辑表达式也可以通过卡诺图看看是否是最简。最后画出逻辑图。

以三人多数表决器且一人带否决权为例:

逻辑思维法:Y=1必须有A为1,B和C任意为1即可,随即得出Y=AB+AC;

真值表法:如下,写出真值表,写出令Y=1的所有组合相加,随后画卡诺图化简;

3. 竞争冒险

竞争现象:当一个门级电路有两个输入信号,正好是反逻辑的时候,就有可能产生竞争现象如Y=A+A非,Y=A·A非。这是因为A非比A要多经过一个非门,可能由于到达时间的延迟导致逻辑输出出错。所以竞争说的是反逻辑的两个输入信号先后到达门级电路的现象

冒险现象: 由于两个互为反逻辑的信号在朝着相反电平跳变的时候会产生“毛刺”,这称为冒险现象。

如何判断是否存在竞争与冒险?

通过化简如果产生Y=A+A非,Y=A·A非的形式,那么就可能出现竞争冒险;在卡诺图中出现卡诺圈相切的情况也有可能出现竞争冒险。

如何消除竞争冒险?

1. 修改逻辑设计

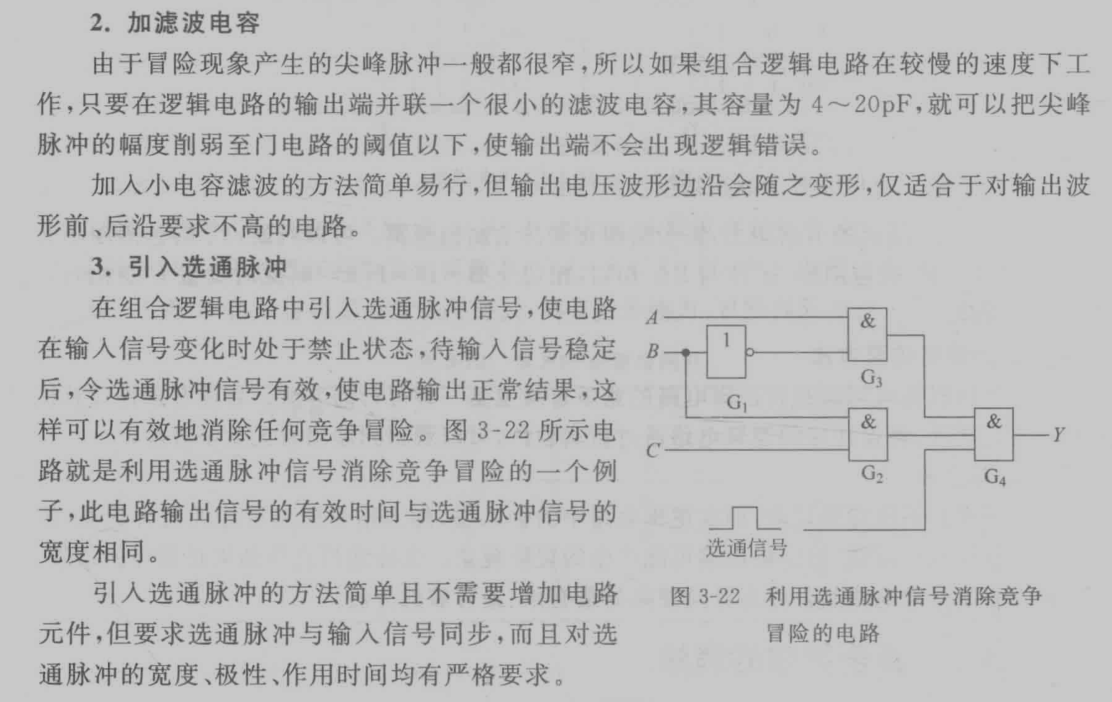

2. 加滤波电容

3. 引入选通脉冲

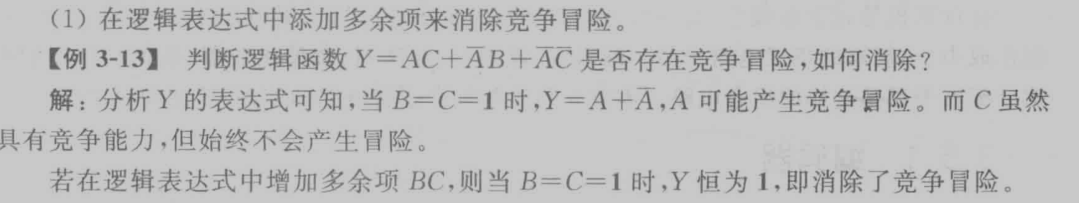

1.修改逻辑设计

4. 组合逻辑电路

这里主要是了解对应概念,重点应该放到verilog中的对应部分,掌握具体的代码实现。

4.1. 编码器

在数字电路中,用二进制数来代表有关信号称为二进制编码,实现编码功能的称为编码器。编码器输入端一般是一个高电平(或低电平)的信号,输出端是代表该信号的二进制码。因为2^3=8,所以3个输出端的编码器可以表示8个输入信号端,这是8-3线编码器。还有BCD编码器(10输入,4输出)。

编码器一般应对出现一个信号有效(高有效或低有效)的情况,而当出现多个信号有效时,则需要引入优先编码器,优先编码器从最高位依次看到最低位,依第一个有效的信号编码。

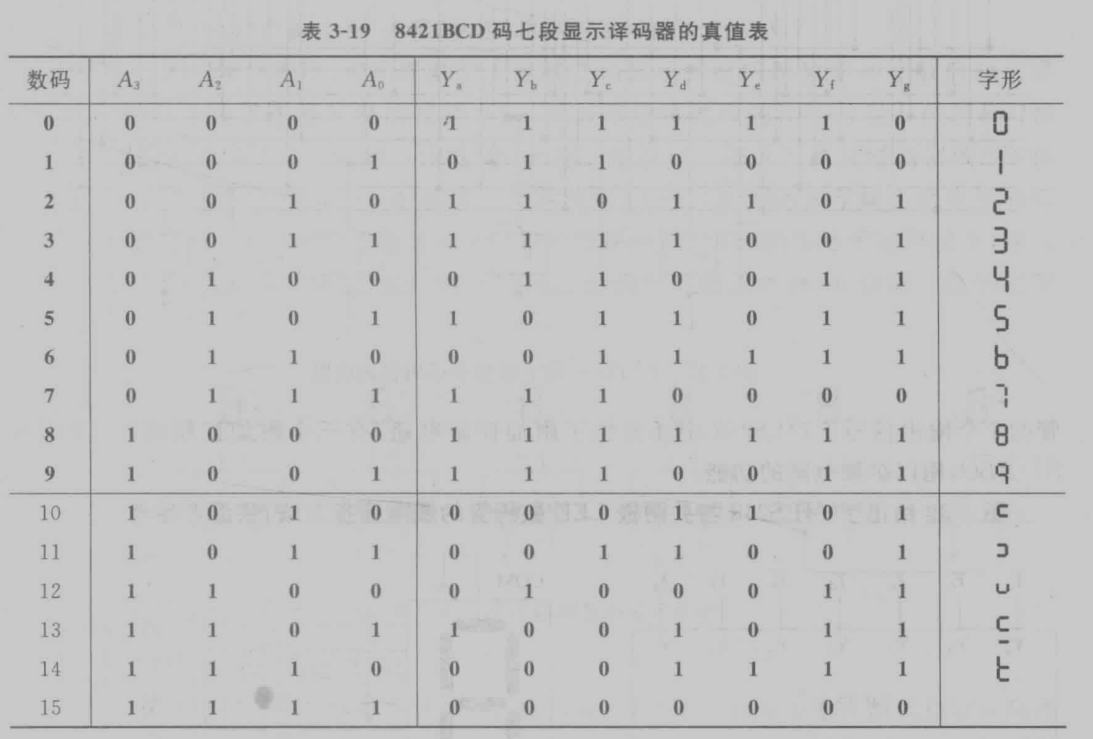

4.2. 译码器

与编码器的功能相反。生活中常见的一个译码器就是计算器。以一个数字为例。当输入0~9的时候,译码器会将通过译码表点亮对应信号。

4.3. 加法器

半加器:不考虑低位的进位

记住一位二进制半加器的逻辑表达式

S(和sum)是单1为1(A和B中出现一个1),那么S的逻辑表达式就为A和B的异或

CO(进位向上carry bit on)是同1为1,所以CO的逻辑表达式是A与B。

全加器:考虑进位

一位二进制全加器的逻辑表达式根据上述思路同理可推

4.4. 数据选择器

数据选择器是两输入一输出的器件。两个输入分别是数据输入信号和地址输入信号,数据输入信号是2^n个,地址输入信号是n位二进制,一一对应。

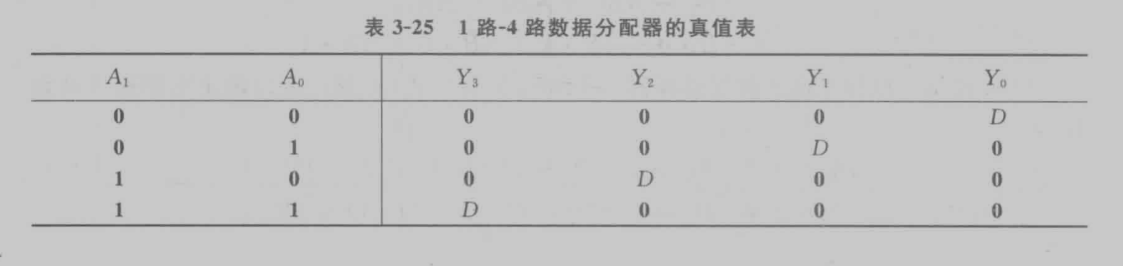

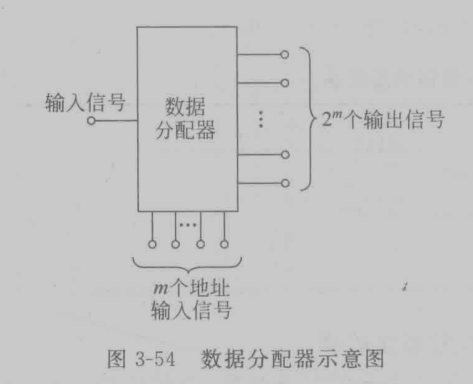

4.5. 数据分配器

数据分配器是两输入一输出,其中D是输入信号,数据分配器根据输入地址,将输入信号分配到对应的输出端上。可以发现如果将D变换为1,则变成了译码器。可以这样理解,数据分配器和译码器都是分配信号到对应地址的,一个分配的是信号D,一个分配的是信号1。

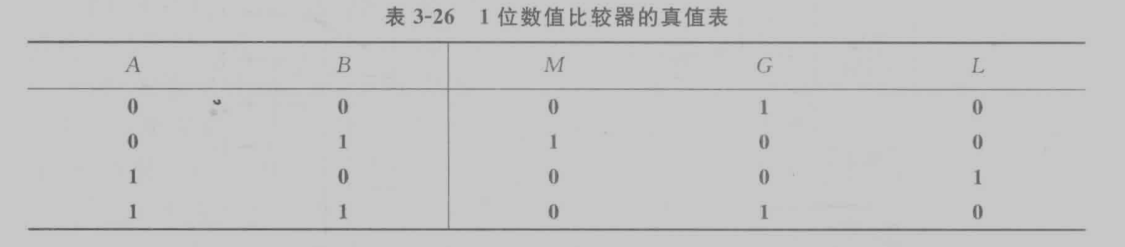

4.6. 数值比较器

数值比较器是两输入三输出,G表示good,相等,M和L分别表示一方大