逻辑门对应布尔运算,逻辑门组合对应布尔表达式,逻辑门组合的相互转换对应布尔表达式的相互转换。但无论逻辑门或者表达式如何改变,真值表永远不变。用逻辑门进行组合的电路就叫做组合逻辑电路。

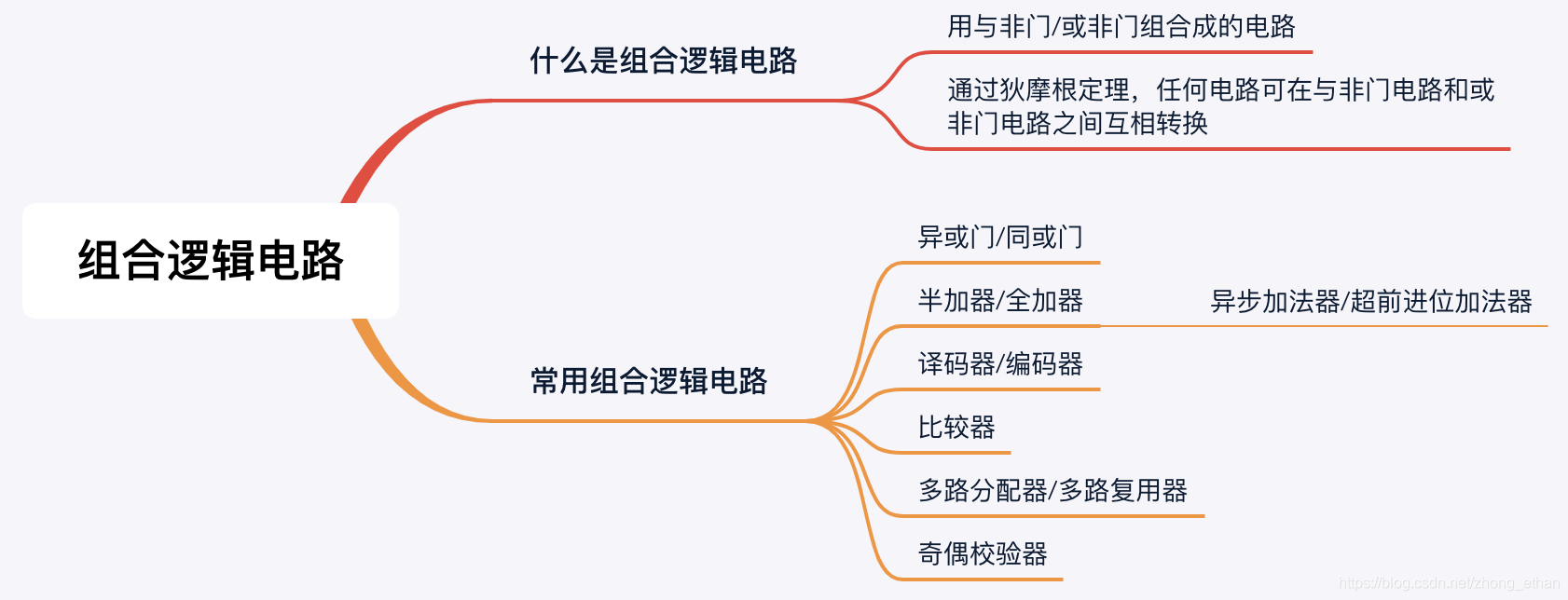

思维导图

逻辑门

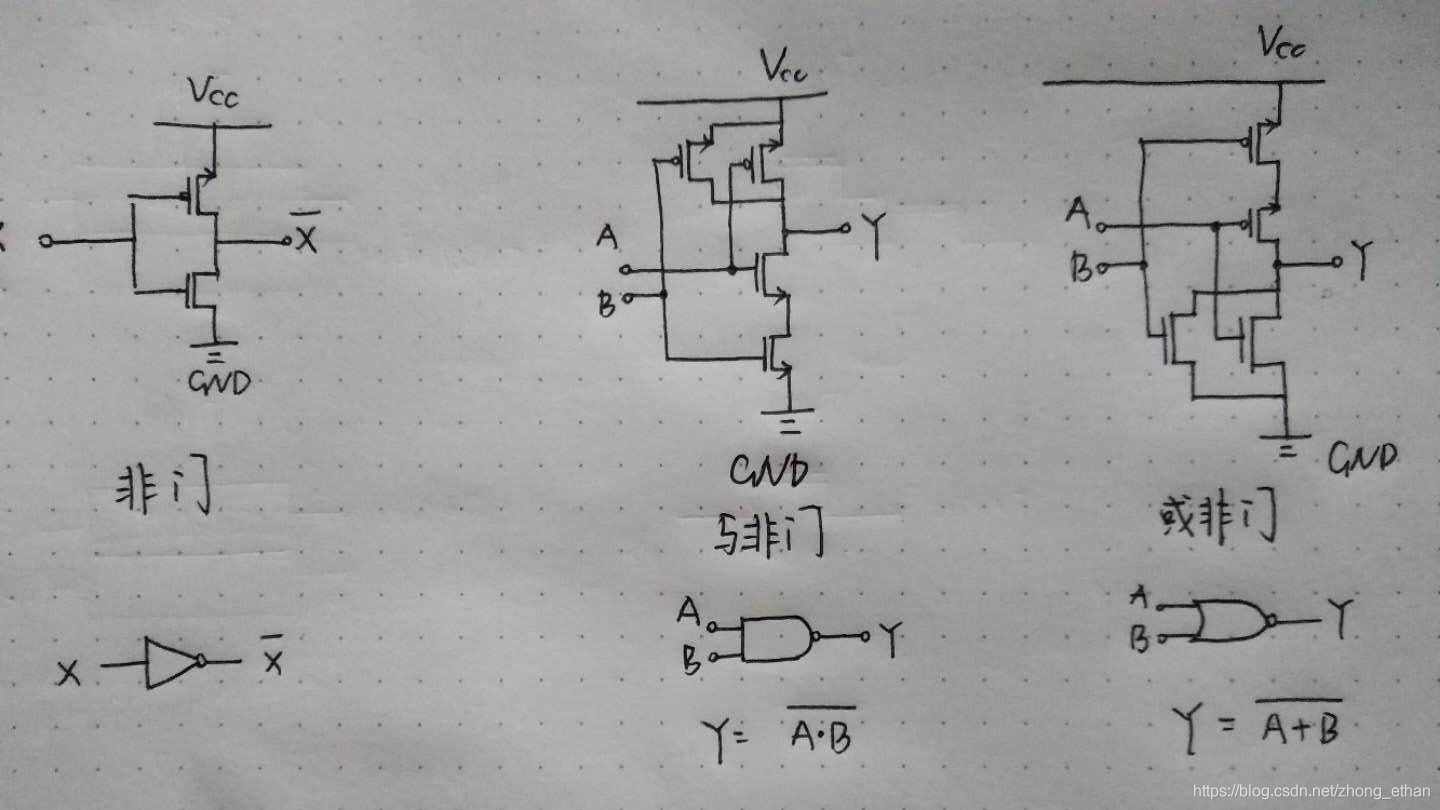

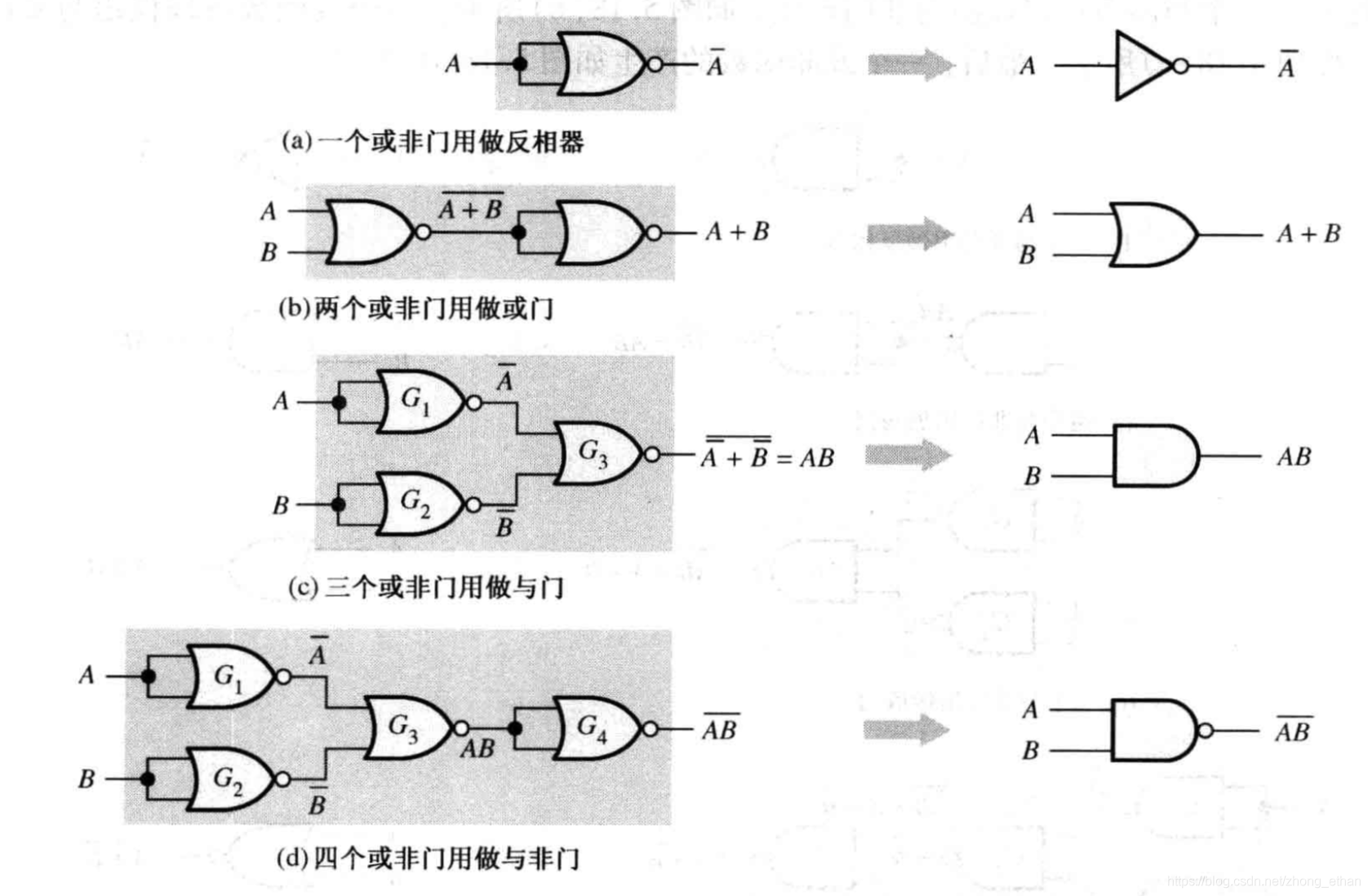

知识点一: 在之前的文章数字电路之布尔代数和逻辑化简中提到,数字电路的基础知识是布尔运算,布尔代数的定律和狄摩根定理。与门对应布尔乘法,或门对应布尔加法,非门对应布尔非运算。在实际电路中,用PMOS和NMOS组合更容易实现一个与非门或者或非门。所以逻辑电路通常是由与非门或者或非门构成,而不是与门或门。

图片来源

知识点二 :简单的逻辑门组合有异或门和同或门,异或逻辑为 Y = A B ˉ + A ˉ B Y=A\bar{B}+\bar{A}B Y=ABˉ+AˉB,同或逻辑为 Y = A ˉ B ˉ + A B Y=\bar{A}\bar{B}+AB Y=AˉBˉ+AB。同或逻辑类似一个比较器,相同为1,异同为0,异或逻辑则相反,相同为0,异同为1。

知识点三:逻辑电路的构成有两个最基本的原则:

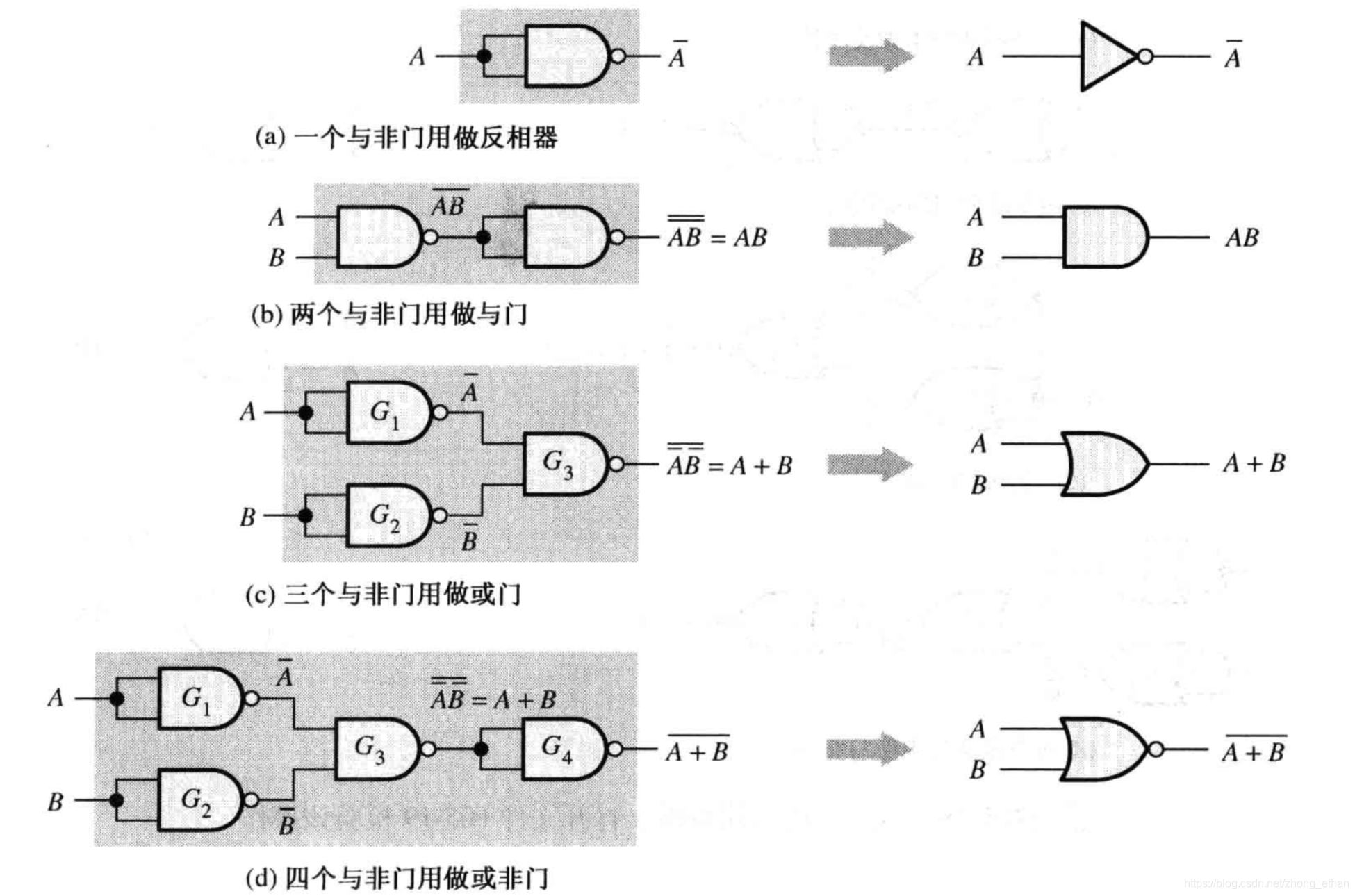

与非门可以用来产生任何逻辑电路

或非门可以用来产生任何逻辑电路

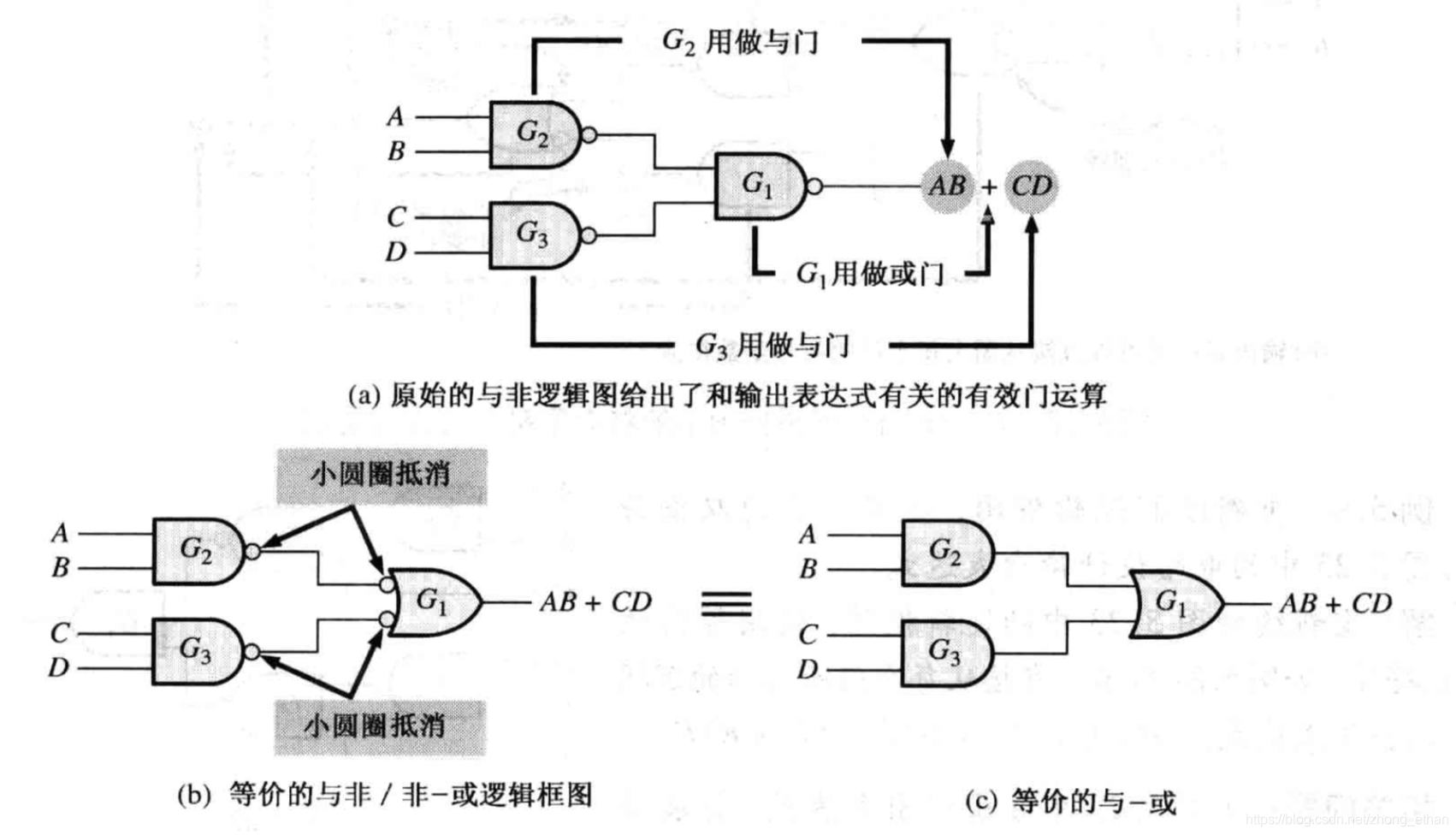

这两个原则的本质就是布尔运算,以下两张图片展示了与非门和或非门构成非门,与门,或门的例子。

知识点四:推小球背后的原理其实就是狄摩根定理。推小球的一个重要作用就是可以很快的从逻辑电路图中写出真值表。

加法器

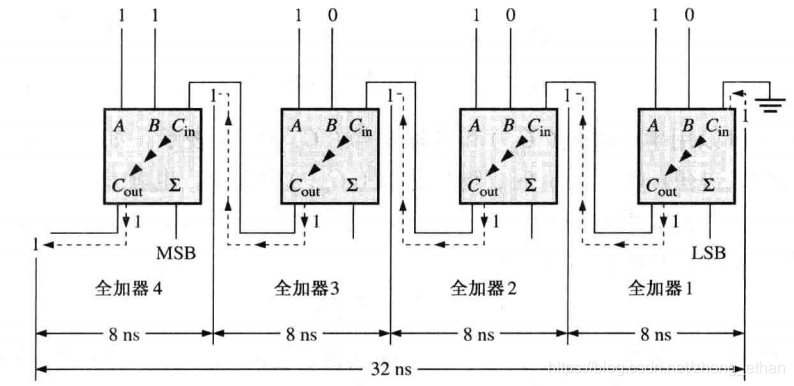

知识点一:两个输入位,产生一个和以及一个进位是半加器;两个输入位再加上一个进位输入,产生一个和以及一个进位是全加器。将一个全加器的进位输出作为下一个全加器的进位输入,可以组成多位异步进位加法器。异步进位加法器的缺点是输出延时高,上一级的进位输出完成后,下一级全加器才开始计算。

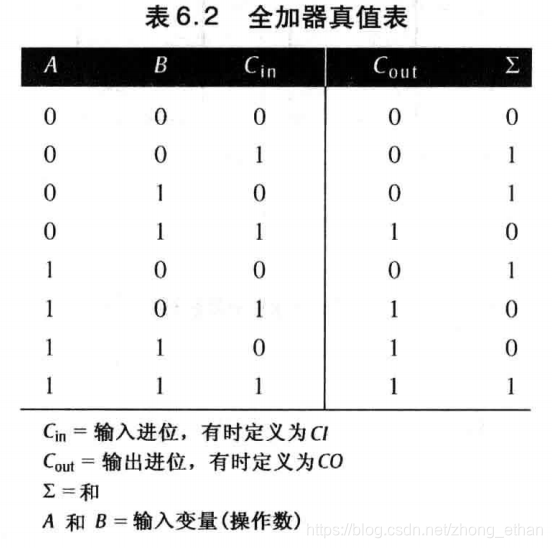

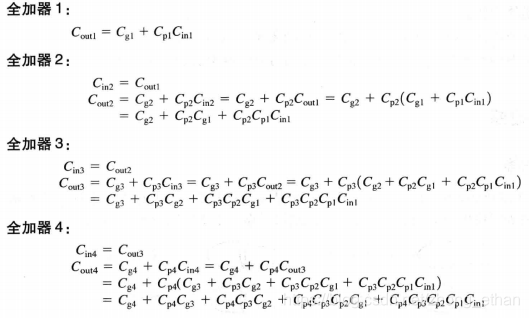

知识点二:为了解决异步加法器输出延时问题,提前得到每个全加器的输入进位,可得到超前进位加法器。一个全加器能出现的所有情况如下图所示:

由真值表可以得到 C o u t C_{out} Cout的关系式为:

C o u t = A B + ( A + B ) C i n C_{out}=AB+(A+B)C_{in} Cout=AB+(A+B)Cin,其中 A B AB AB称为进位生成 C g C_{g} Cg, A + B A+B A+B称为进位传输 C p C_{p} Cp

和的关系式为:

Σ = ( A ⨁ B ) ⨁ C i n \Sigma=(A\bigoplus B)\bigoplus C_{in} Σ=(A⨁B)⨁Cin

因此,只要知道每一级全加器的输入,就可以立即知道每个全加器的进位生成与进位输出函数。这样,每个全加器的计算结果可同时生成。

比较器

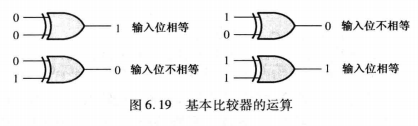

比较器用来判断两个二进制数是否相等,用一个同或逻辑就可以。结果只有三种情况:

a) A=1, B=0 。结果不相等,且A大

b)A=0, B=1,结果不相等,且B大

c) A=B=1, A=B=0,结果相等

若多位数字进行判断,先从最高位开始,若高位相等,则判断下一位,若不相等,则直接得出结果

代码转换器

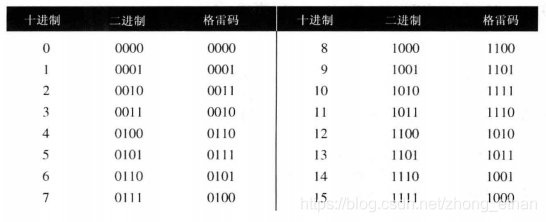

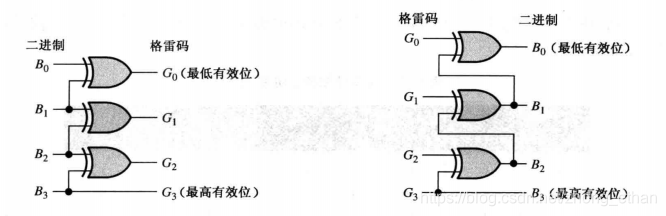

格雷码与二进制数的互转在跨时钟设计中经常用到。格雷码的特点是相邻码之间只有一位发生了变化,其目的是为了减少数据传输中的出错概率。四位格雷码与二进制,十进制数的关系如下:

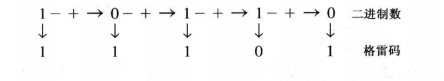

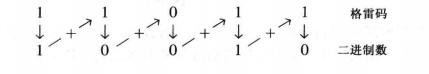

二进制转格雷码最高有效位不变,从左到右,将每一对相邻的二进制码相加,舍去进位,得到下一个格雷码位。

格雷码转二进制最高有效位不变,将得到的二进制码与下一位的格雷码相加,舍去进位,得到下一位二进制码。

一位不产生进位的加法电路用异或门就可以实现,下图左边为一个二进制-格雷码转换器器,右边为一个格雷码-二进制码转换器。

译码器与编码器

译码器是一个非常重要的组合逻辑。在计算机中,程序指令以机器码的形式存在,为了使计算机执行指令,需要对指令译码。指令译码时指令流水线中的一步,过程如下:从存储器中取出指令,指令译码,从存储器读取操作数,执行指令,将结果写回存储器。

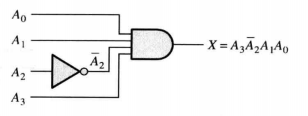

基本的译码逻辑电路如下所示,图中电路对二进制1011进行译码。

常见的译码器还有BCD-十进制译码器,BCD-7段译码器。

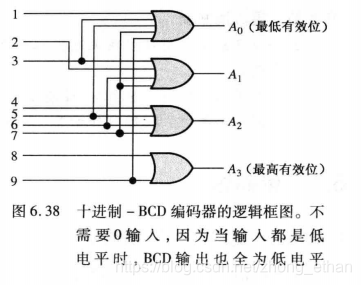

常见编码器有十进制-BCD编码器,其逻辑框图如下所示。实现起来很简单,只要把相对应的十进制数输入线相或,形成每个BCD输出。编码器的应用有键盘。

数据选择器(多路复用器)

Verilog中的if…else 语句通常会综合一个数据选择器。如下为一个四选一数据选择电路。

数据输出的总的表达式为:

Y = D 0 S 1 ˉ S 0 ˉ + D 1 S 1 ˉ S 0 + D 2 S 1 S 0 ˉ + D 3 S 1 S 0 Y=D_{0}\bar{S_{1}}\bar{S_{0}}+D_{1}\bar{S_{1}}S_{0}+D_{2}S_{1}\bar{S_{0}}+D_{3}S_{1}S_{0} Y=D0S1ˉS0ˉ+D1S1ˉS0+D2S1S0ˉ+D3S1S0

数据选择器在电路中应用非常广泛。在计算机网络中,一条共享总线就是连接系统中所有的计算机且用于交换数据的通路。一条共享总线可以连接存储器和输入/输出设备,这样这些设备就可以由系统中所有的计算机共享。对共享总线的访问是由总线判优器控制的,每次只允许一台计算机共享系统的总线。

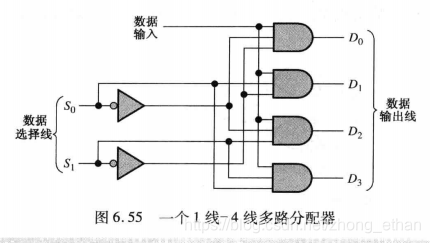

多路分配器

在一个多路分配器中,数据从一条线路中被分配到几条线路上。如下面一个一线-四线多路分配器。数据输入线与所有的门连接,每一次,两条数据选择线只开通一个逻辑门,然后数据输入线上的数据通过这个选中的门,传送到相应的数据输出线上。

奇偶校验器

基本奇偶校验器检测一个代码中,1的个数是偶数还是奇数。奇偶校验器用到的基本原理是:

偶数个1相加的结果始终是0,奇数个1相加的结果始终是1。

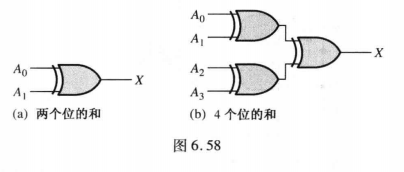

用一个异或逻辑就可以实现上面的功能: