文章目录

组合电路的输出只与电路的输入有关,与电路的前一时刻的状态无关,组合逻辑电路只包含门电路。而时序逻辑电路是组合逻辑电路+存储电路结合;输出状态必须反馈到组合电路的输入端,与输入信号共同决定组合逻辑的输出。

关于触发器的分类。阎石版本的《数字电子技术基础》将触发器触发类型分为三种,分别是:电平触发,脉冲触发,边沿触发。然而书中脉冲触发和边沿触发举的例子实际上是一种,即边沿触发器。在本文边沿触发的SR触发器的例子中,脉冲转换检测器可看成是阎石书中的脉冲触发类型。实际上,如果从时钟的角度来看,只有两种触发类型,即电平触发和边沿触发,本文按照这种思路对触发器类型进行分类,并把电平触发器称作门控锁存器。因此,本文的思路就是先介绍锁存器,其次门控锁存器,最后边沿触发器。

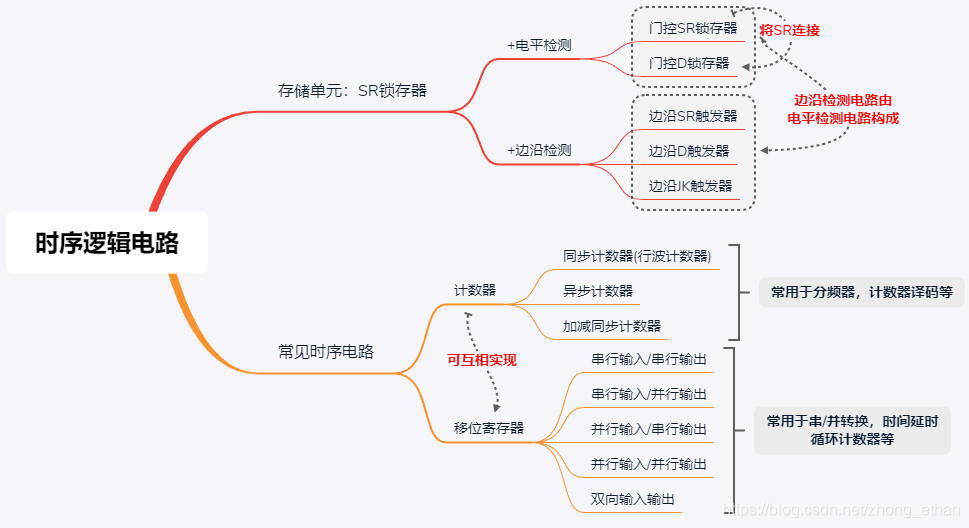

思维导图

锁存器

置位的意思是Q输出为高电平,复位的意思是Q输出为低电平

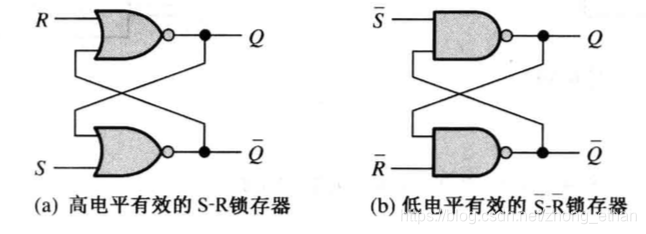

S-R锁存器

注意图中SR的信号位置不一样,左图中S信号在下面,右图中S信号在上面

| 高电平有效的SR锁存器 | 低电平有效的SR锁存器 | 输出 | 说明 |

|---|---|---|---|

| S = 1 , R = 1 S=1, R=1 S=1,R=1 | S ˉ = 0 , R ˉ = 0 \bar{S} = 0, \bar{R}=0 Sˉ=0,Rˉ=0 | Q = 1 , Q ˉ = 1 Q=1, \bar{Q}=1 Q=1,Qˉ=1 | 无效情况 |

| S = 1 , R = 0 S=1, R=0 S=1,R=0 | S ˉ = 0 , R ˉ = 1 \bar{S} = 0, \bar{R}=1 Sˉ=0,Rˉ=1 | Q = 1 , Q ˉ = 0 Q=1, \bar{Q}=0 Q=1,Qˉ=0 | 锁存器置位 |

| S = 0 , R = 1 S=0, R=1 S=0,R=1 | S ˉ = 1 , R ˉ = 0 \bar{S} = 1, \bar{R}=0 Sˉ=1,Rˉ=0 | Q = 0 , Q ˉ = 1 Q=0, \bar{Q}=1 Q=0,Qˉ=1 | 锁存器复位 |

| S = 0 , R = 0 S=0, R=0 S=0,R=0 | S ˉ = 1 , R ˉ = 1 \bar{S} = 1, \bar{R}=1 Sˉ=1,Rˉ=1 | Q = N C , Q ˉ = N C Q=NC, \bar{Q}=NC Q=NC,Qˉ=NC | 锁存器不变,维持当前状态 |

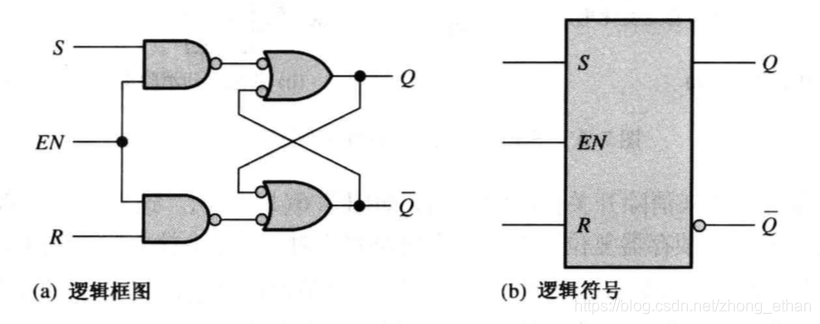

门控S-R锁存器

门控锁存器需要一个使能输入端EN,当EN有效时,SR输入影响Q端输出,当EN无效时,Q端输出保持不变,图中EN电平为高时有效。

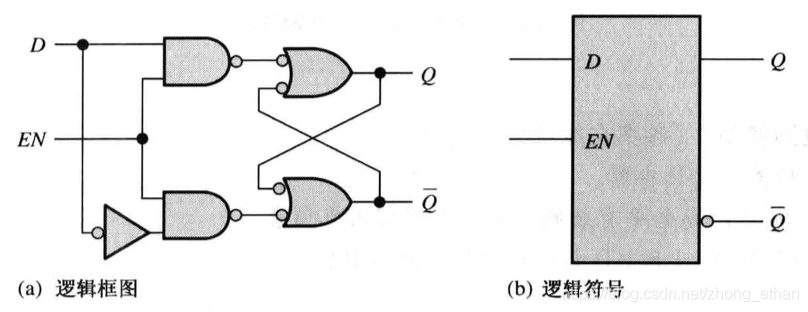

门控D锁存器

将SR锁存器的R端与S端的反向信号连接到一起就成了D锁存器。D锁存器消除了SR锁存器中无效情况,即上面表格中的第一种情况。

上图门控D锁存器的真值表为:

上图门控D锁存器的真值表为:

| D信号 | EN信号 | Q输出 | 说明 |

|---|---|---|---|

| 1 | 1 | 1 | 置位 |

| 0 | 1 | 0 | 复位 |

| 1 | 0 | NC | 输出信号不变 |

| 0 | 0 | NC | 输出信号不变 |

计算机中的共享数据总线经常用到门控D锁存器,也称为透明锁存器。透明锁存器处在共享数据总线与外部数据之间,锁存器关闭时,外部数据不会传到数据总线上,相当于锁存器从总线上断开。锁存器打开后,外部数据就会传输到总线上,就像直接连接一样。实际电路中应该避免使用透明锁存器,因为使能信号开启后,输入与输出是直接连通的,输入信号的毛刺也会传递给输出信号。另外,EDA工具也不能很好的处理锁存器,使得综合后的电路达不到设计者的要求。

边沿触发器

边沿触发器的状态变化只发生在时钟脉冲的边沿。触发器的基本应用是数据存储。

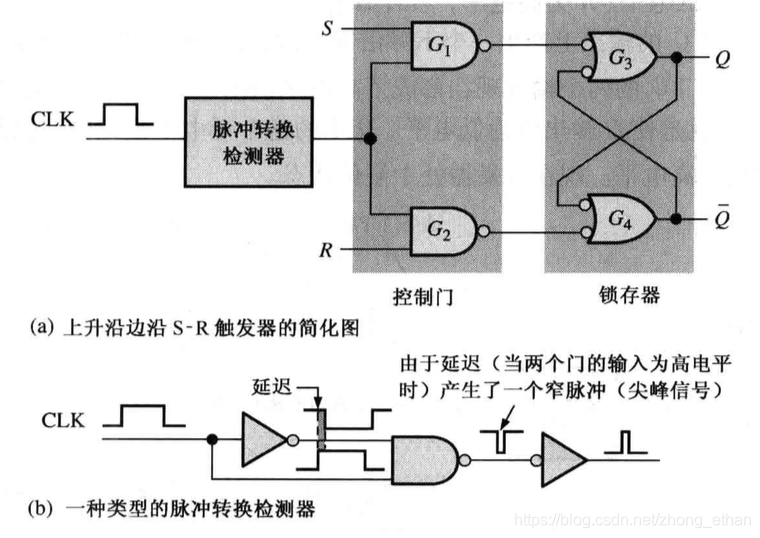

边沿触发的S-R触发器

上升边沿触发的SR触发器原理图如下所示,与门控SR锁存器的区别是,原EN输出端变成一个脉冲转换检测器。

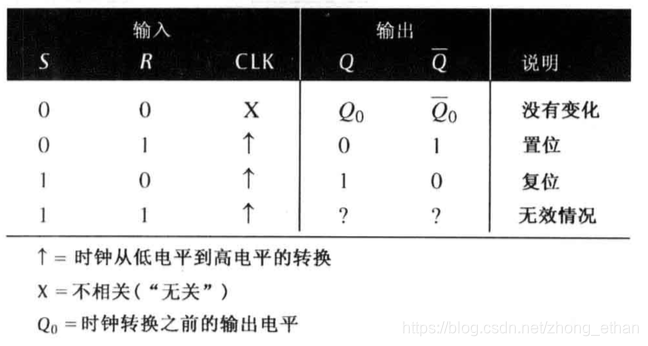

低电平有效的边沿SR触发器真值表如下所示:

低电平有效的边沿SR触发器真值表如下所示:

边沿触发的D触发器

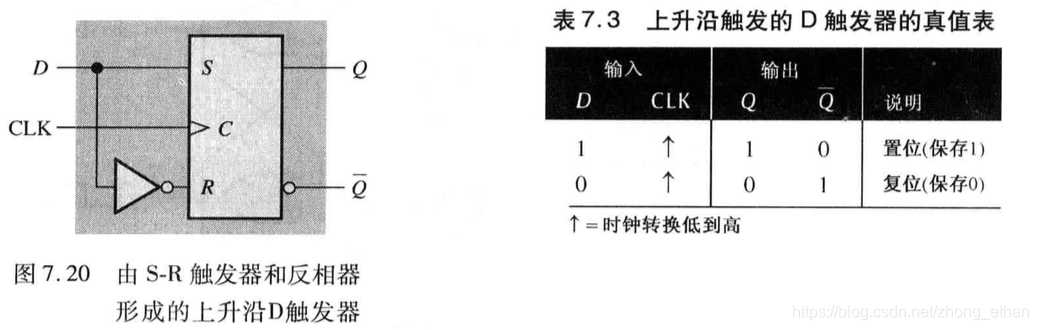

SR触发器加上一个反相器就构成了D触发器,上升沿有效的D触发器真值表如下所示:

边沿触发的J-K触发器

JK触发器名字是以Jack Kilby的名字命名的,Jack Kilby发明了集成电路。

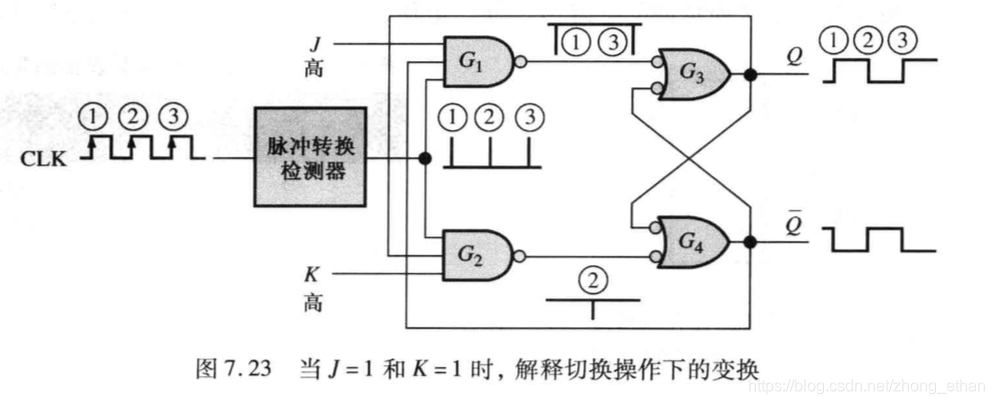

JK触发器与SR触发器的区别是没有无效状态,并新增一个切换状态。切换原理如下:

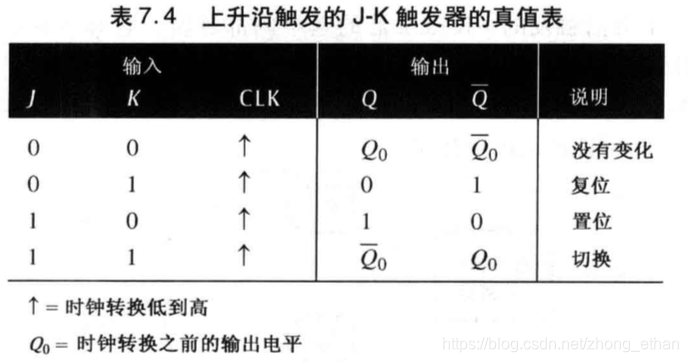

上升沿触发的JK触发器真值表

异步预置位输入和清零输入

有效预置位输入使Q端输出为高电平

有效清零输入使Q端输出为低电平

异步的意思是这些输入可以独立于时钟的变化而影响输出的状态。

具有异步预置位输入和清零输入的JK触发器原理如下所示:

触发器动态特性

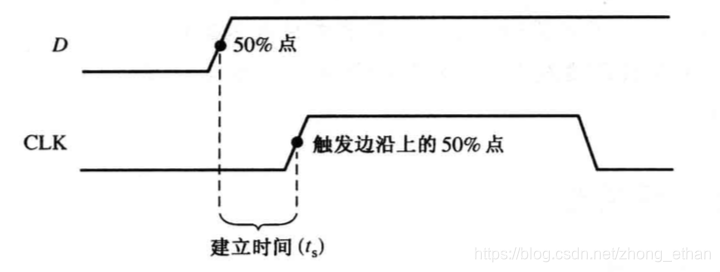

建立时间 是输入先于时钟触发边沿到达所需要的最小的时间。在此时间范围内输入信号的电平保持不变,这样就可以使输入电平可靠的按时序进入触发器。

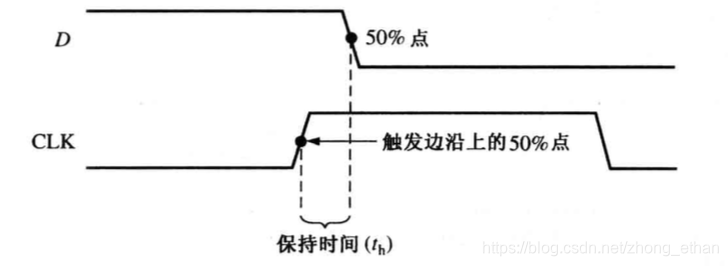

保持时间 是时钟触发边沿到达输入信号需要保持的最小时间。在此时间范围内输入信号的电平保持不变,这样就可以使输入电平可靠的按时序进入触发器。

保持时间 是时钟触发边沿到达输入信号需要保持的最小时间。在此时间范围内输入信号的电平保持不变,这样就可以使输入电平可靠的按时序进入触发器。

最大时钟频率是触发器可靠工作的最大工作频率。

最大时钟频率是触发器可靠工作的最大工作频率。

计数器

异步计数器

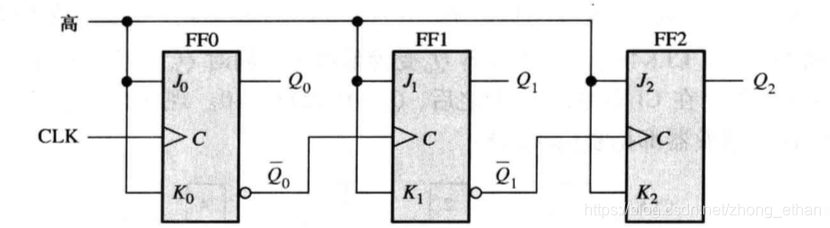

异步计数器又称为行波计数器,异步计数器的时钟总是只连接到最低有效位的触发器上,输入时钟脉冲的效应以行波的形式通过计数器。下图为一个三位异步计数器示意图。实际电路中应避免使用行波计数器,因为第一个触发器的输入时钟到Q输出存在延时使得第二个触发器的时钟输入产生偏移,如果延时累积比较大,甚至超过了时钟周期,就会出错。尽管使用行波计数器存在很多问题,但是在功耗较高的系统中很适合用这种计数器,因为这种电路实现起来简单,逻辑门少,能大量降低功耗。

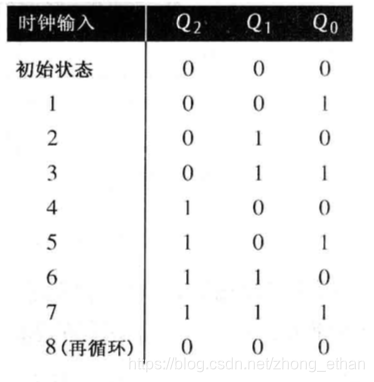

三位异步计数器真值表。

三位异步计数器真值表。

异步计数器的主要缺点是限制了计数器按时钟运行速度。计数器的最大累积延时必须小于时钟波形的周期。

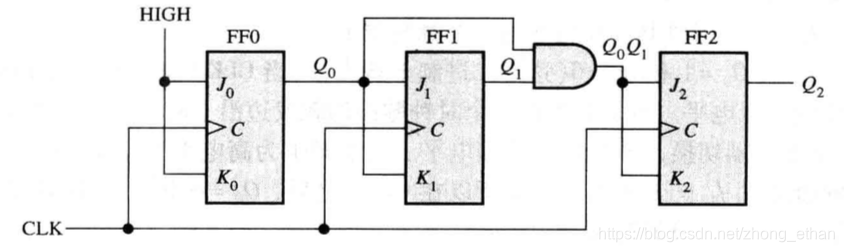

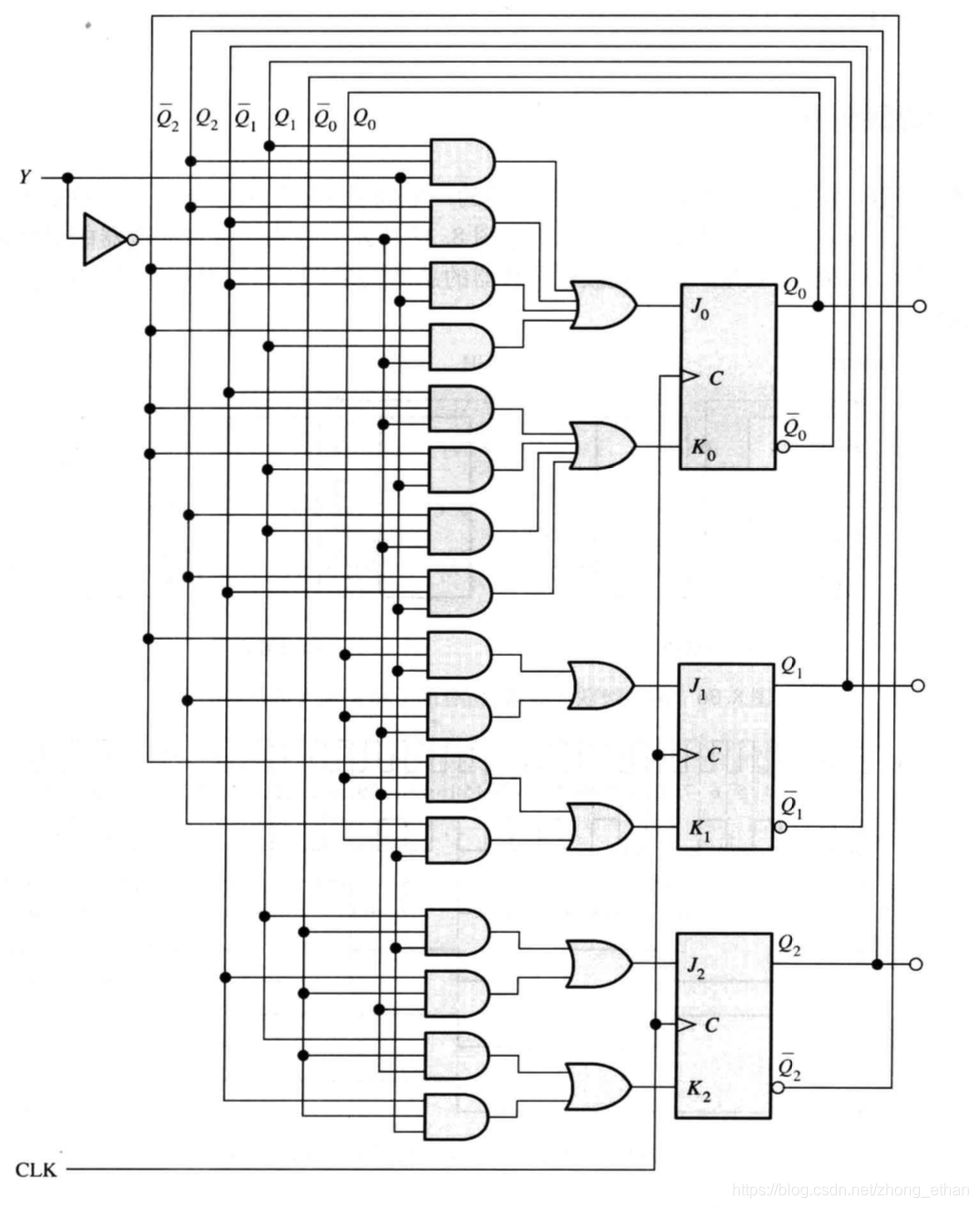

同步计数器

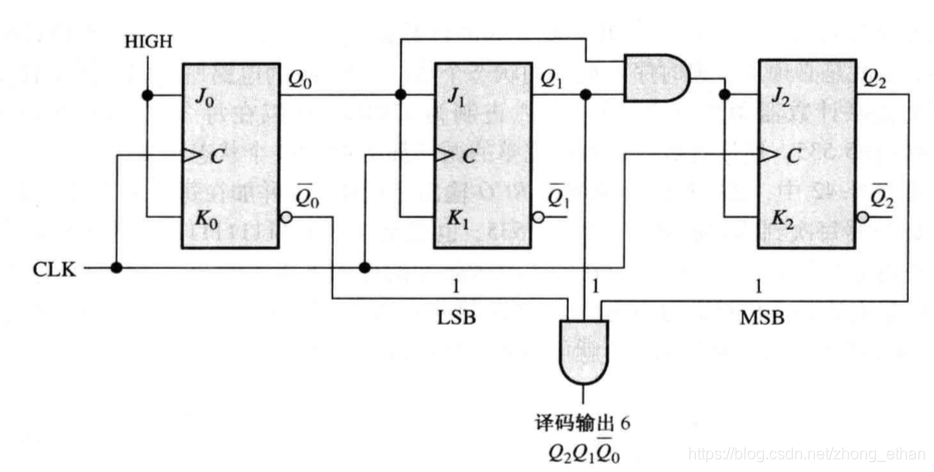

同步计数器的所有有效位触发器都连接在同一个时钟源上。三位同步计数器的真值表与三位异步计数器的真值表一致,结构示意图如下:

加减同步计数器

加减计数器可以在序列中的任何地方反转。例如可以做到如下的序列:

0-1-2-3-4-5-4-3-2-3-4-5-6-7-8-9-8-7-8-9-0-1

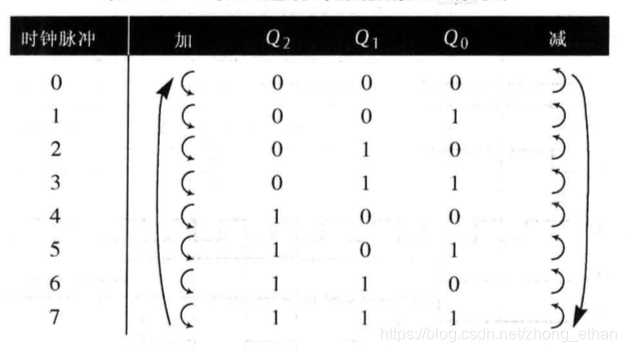

对于一个三位的加减同步计数器,真值表如下所示:

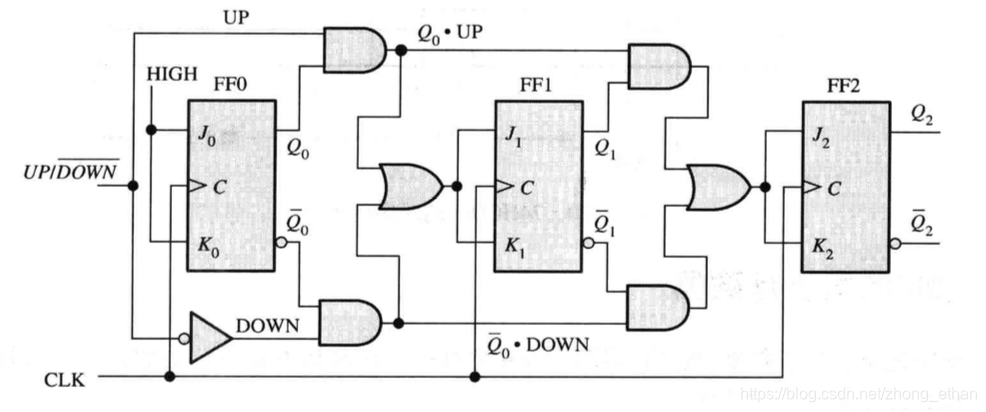

FFO在每个时钟到来时切换状态,因此 J 0 , K 0 J_{0},K_{0} J0,K0的输入仍然是: J 0 = K 0 = 1 J_{0}=K_{0}=1 J0=K0=1

对于加时序, Q 1 Q_{1} Q1在 Q 0 = 1 Q_{0}=1 Q0=1的下一个时钟翻转,对于减时序, Q 1 Q_{1} Q1在 Q 0 = 0 Q_{0}=0 Q0=0的下一个时钟翻转。因此 J 1 , K 1 J_{1},K_{1} J1,K1的输入为:

J 1 = K 1 = Q 0 . U P + Q ˉ 0 . D O W N J_{1}=K_{1}=Q_{0}.\bold{UP}+\bar{Q}_{0}.\bold{DOWN} J1=K1=Q0.UP+Qˉ0.DOWN

对于加时序, Q 2 Q_{2} Q2在 Q 1 = Q 0 = 1 Q_{1}=Q_{0}=1 Q1=Q0=1的下一个时钟翻转,对于减时序, Q 2 Q_{2} Q2在 Q 1 = Q 0 = 0 Q_{1}=Q_{0}=0 Q1=Q0=0的下一个时钟翻转。因此 J 2 , K 2 J_{2},K_{2} J2,K2的输入为:

J 2 = K 2 = Q 0 . Q 1 . U P + Q ˉ 0 . Q ˉ 1 . D O W N J_{2}=K_{2}=Q_{0}.Q_{1}.\bold{UP}+\bar{Q}_{0}.\bar{Q}_{1}.\bold{DOWN} J2=K2=Q0.Q1.UP+Qˉ0.Qˉ1.DOWN

三位同步加减计数器的结构示意图如下所示:

同步计数器设计的通用步骤

(1)画出状态图

(2)写出次态表

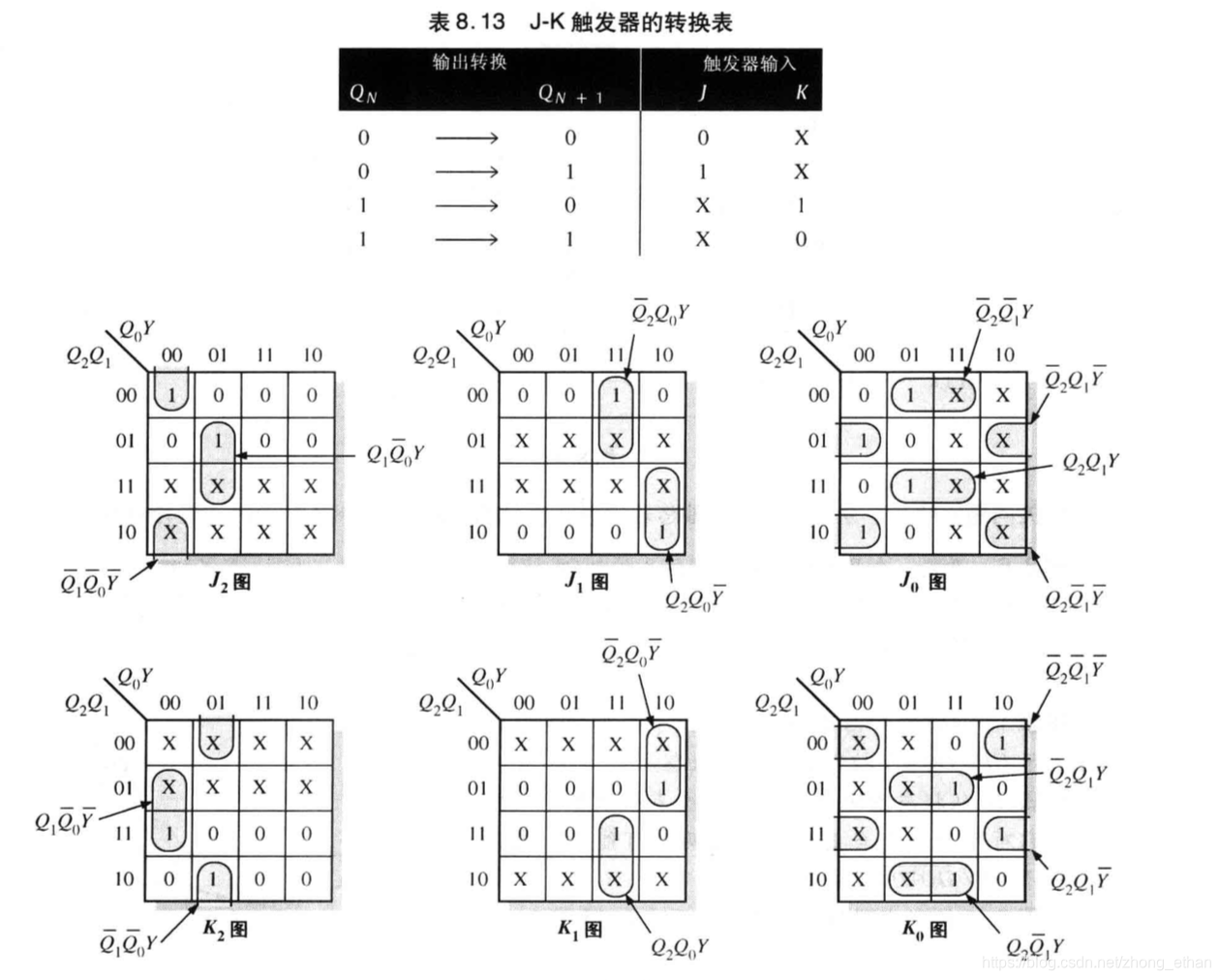

(3)结合触发器转换表,生成卡诺图

(4)卡诺图化简,写出每个触发器的输入逻辑表达式

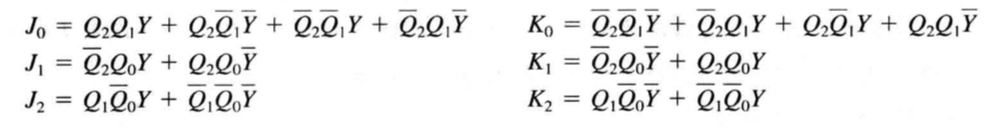

(5)画出电路图

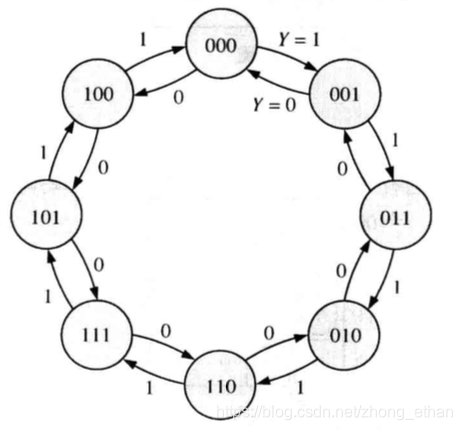

下面给出一个三位加减计数器的设计例子:

步骤一:画出状态图。Y=1表示加,Y=0表示减

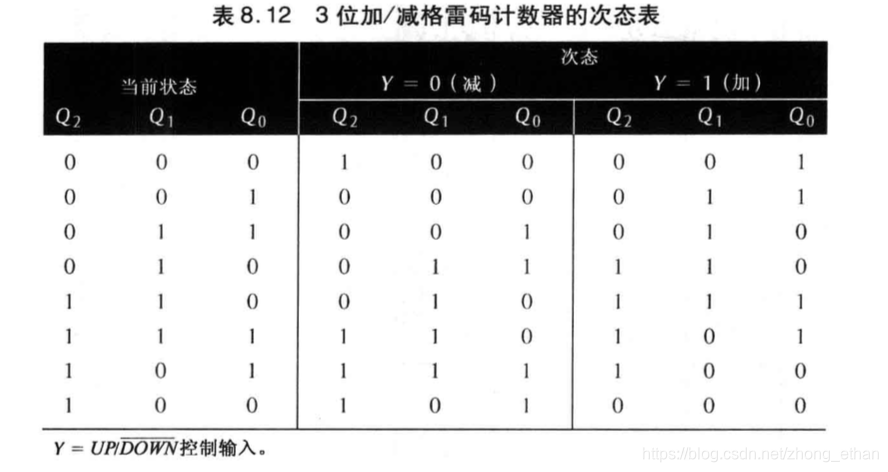

步骤二:写出次态表。

步骤三结合JK触发器转换表绘制卡诺图。

步骤四:卡诺图化简写出触发器输入逻辑表达式:

步骤五 画出电路图

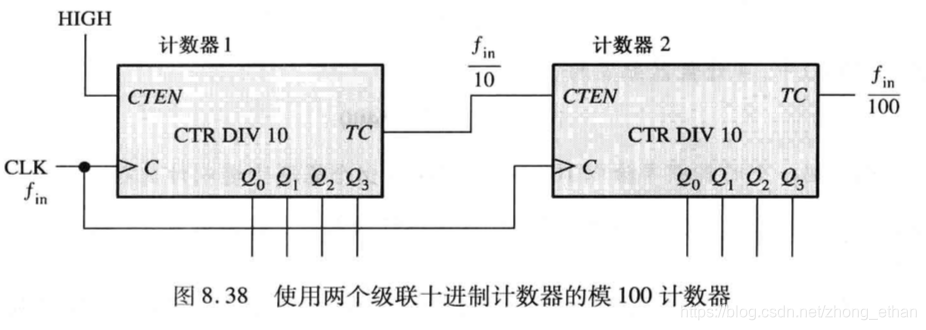

计数器的应用

(1)分频器

(2)计数译码器

例如实现一个三位二进制译码器状态为6的译码

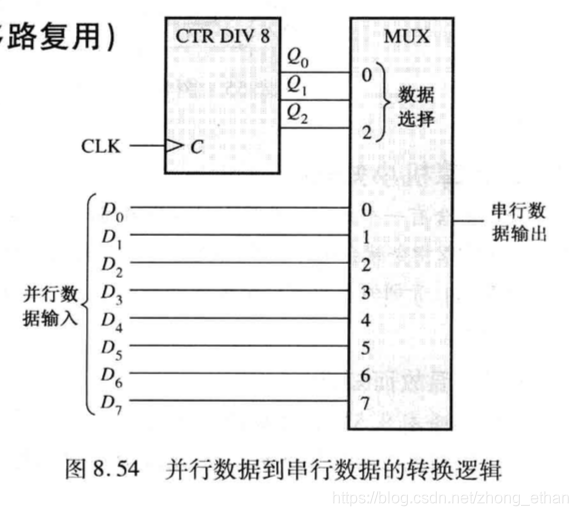

(3)并行/串行数据转换器

(3)并行/串行数据转换器

移位寄存器

JK触发器是构成计数器的基础,D触发器是构成移位寄存器的基础

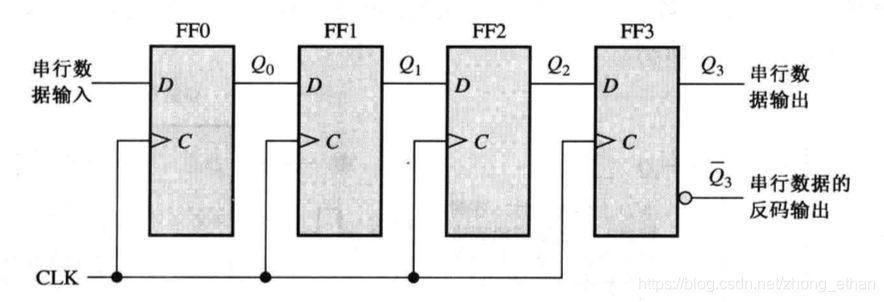

串行输入/串行输出寄存器

串行输入/并行输出寄存器

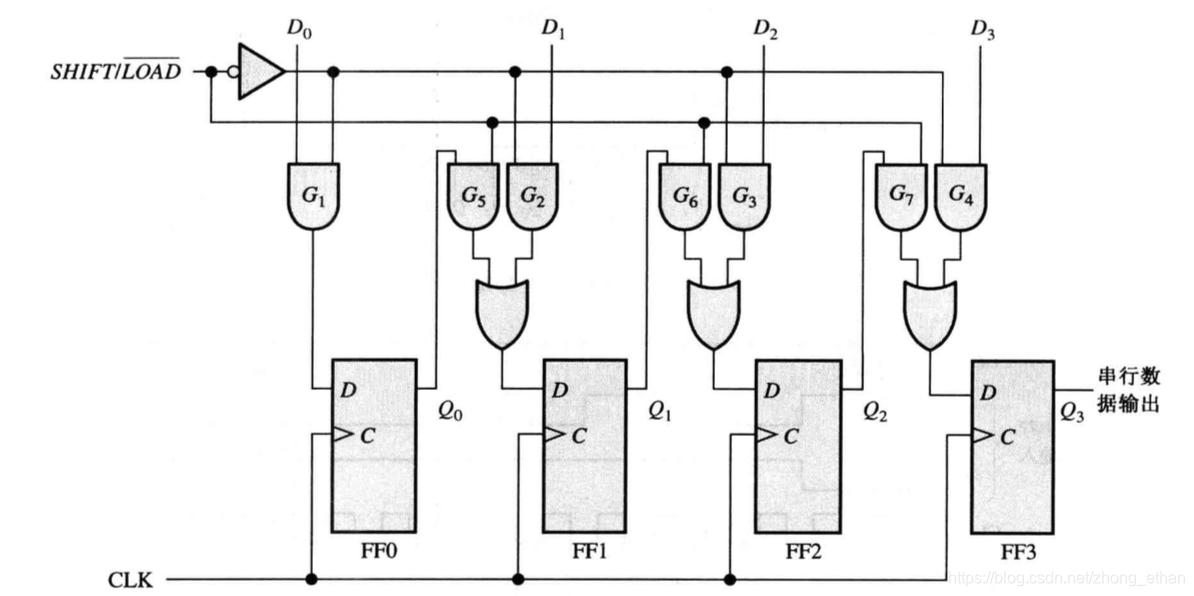

并行输入/串行输出寄存器

SHIFT信号为低时,LOAD信号有效,此时数据加载进入寄存器的D端。SHIFT信号为高时,每一级的D端信号传输到Q端,在时钟脉冲作用下,数据串行输出。

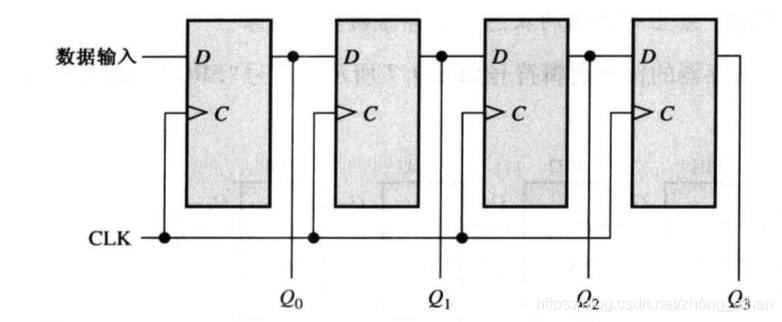

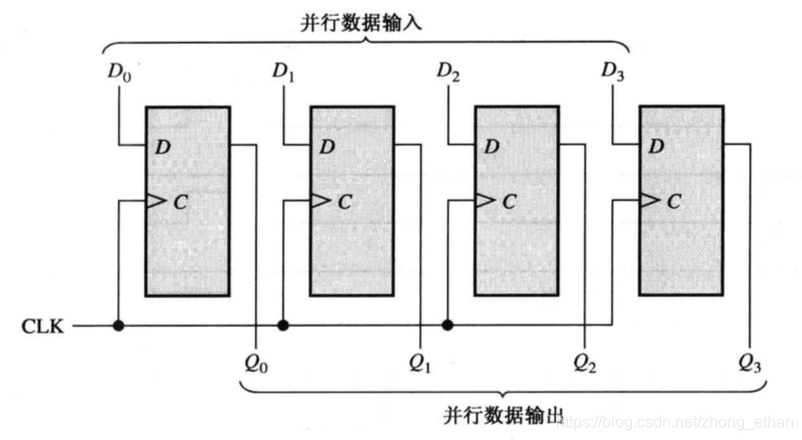

并行输入/并行输出寄存器

双向移位寄存器

当RIGHT信号为高时, G 1 − G 4 G_{1}-G_{4} G1−G4门开启,每个触发器的Q端传送到下一个触发器的输入端D,当时钟脉冲到来时,数据向右移动。当RIGTH信号为低时, G 5 − G 8 G_{5}-G_{8} G5−G8门开启,每个触发器的Q端传送到上一个触发器的输入端D,当时钟脉冲到来时,数据向左移动。

移位寄存器的应用

(1)时间延时

在电路的时序设计中,如果想要将数据传输时间延时一拍,通常在传输线上加一寄存器。延时时间是寄存器级数和时钟频率的函数

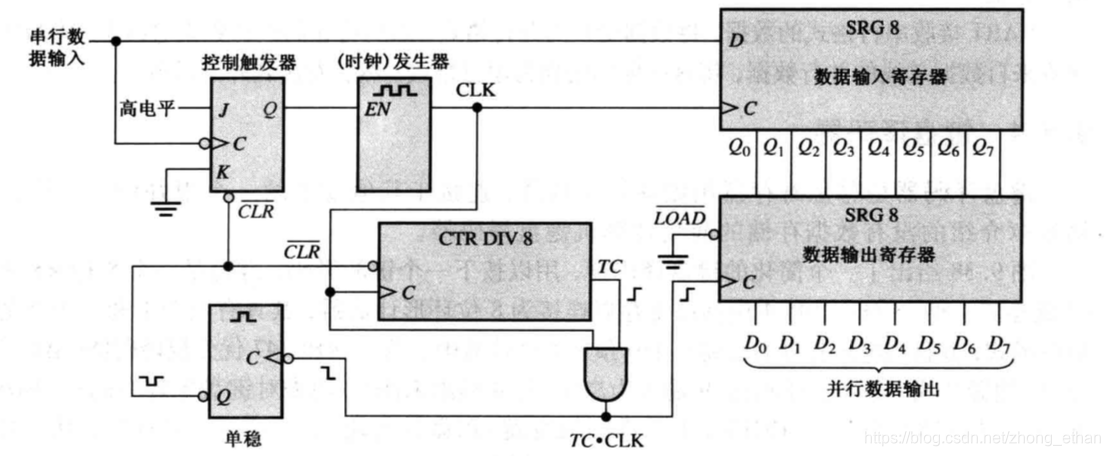

(2)串行到并行数据转换器

从一个数字系统到另一个数字系统,为了减少两者之间的传输线数量,通常使用串行传输,数字系统内部就需要一个串行/并行转换器。下图是一个简单的串行/并行转换器。UART(通用异步接收发送机)除了含有一个串行/并行转换器外,还有一个并行/串行转换器。

(3)计数器

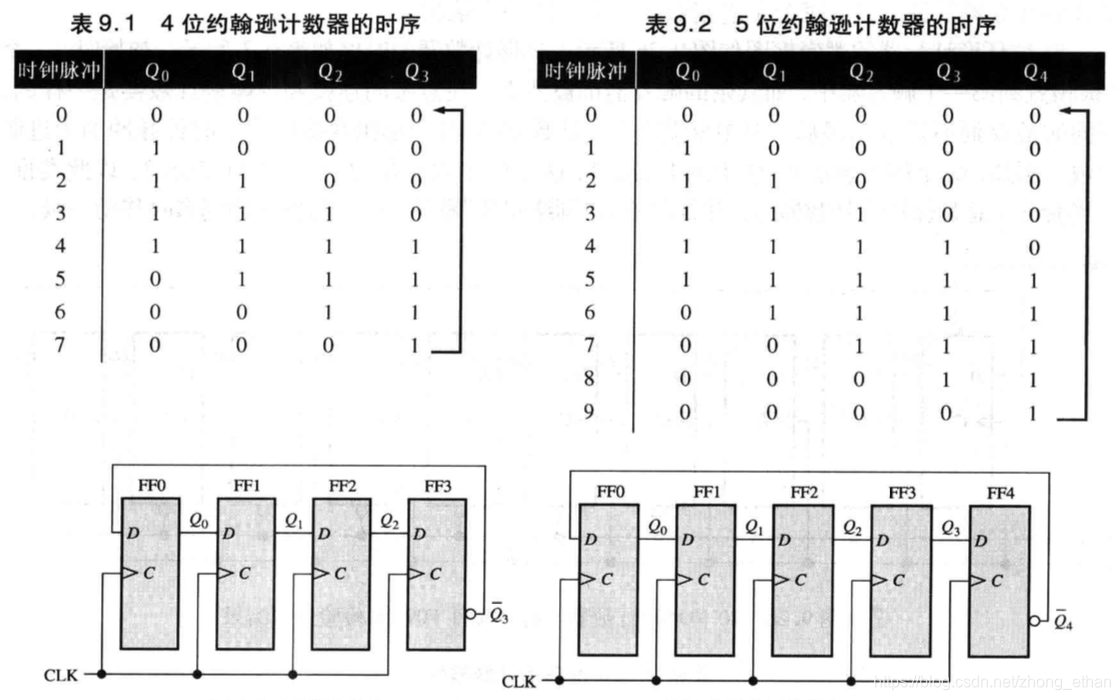

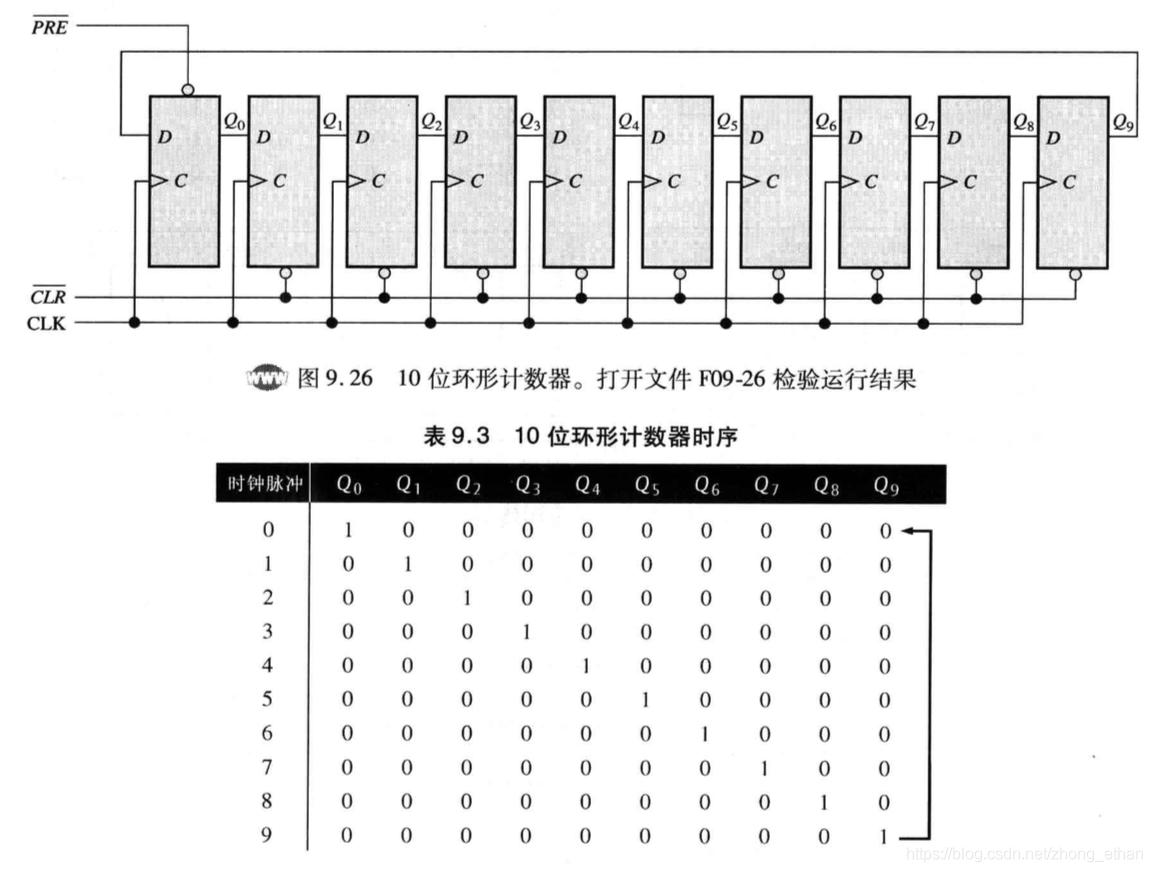

移位寄存器也通常用来设计计数器,常用的有约翰逊计数器和环形计数器。