文章目录

前言

环境:

1、Quartus18.0

2、vscode

3、基于Intel DE2-115的开发板

一、一位全加器

- 全加器简介:

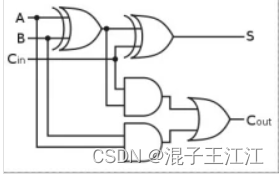

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

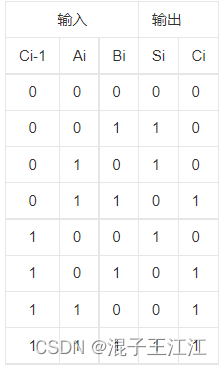

- 输入输出真值表:

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci

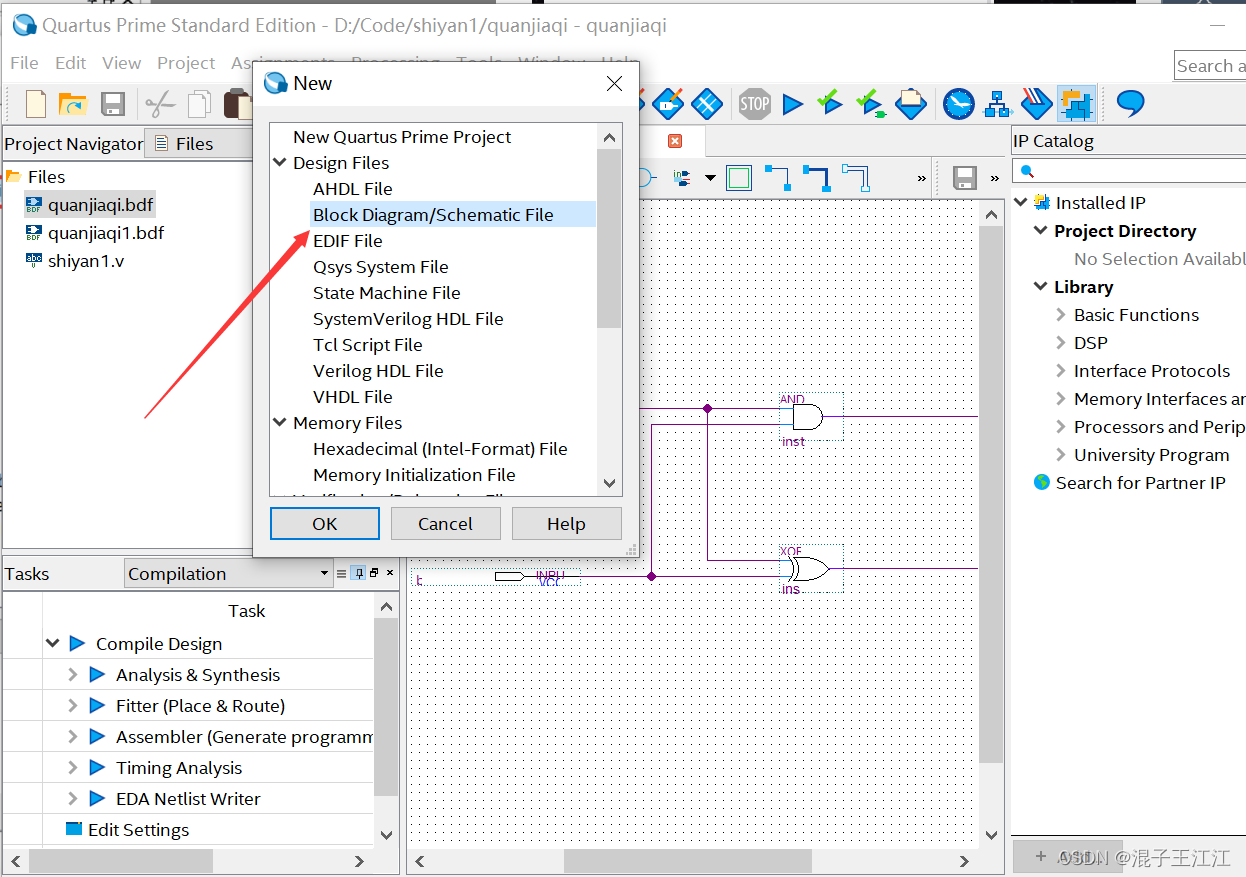

1、一位全加器的原理图设计

工程创建过程这里就不再赘述,之前已经仔细介绍过,芯片型号选为EP4CE115F29即可。具体操作看下面:

https://blog.csdn.net/qq_52215423/article/details/127832959

- 在实现一位全加器之前需要先设计一下半加器:

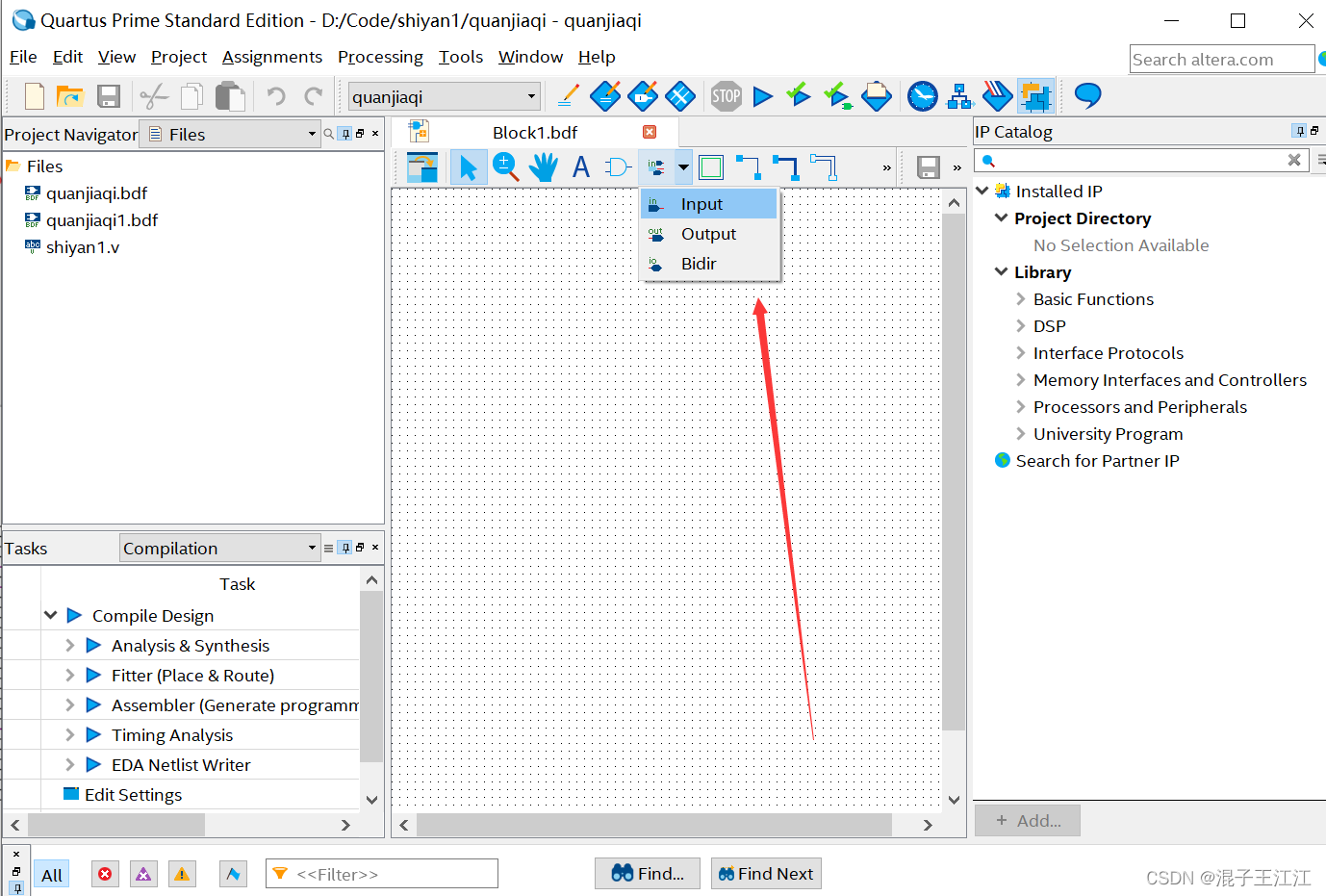

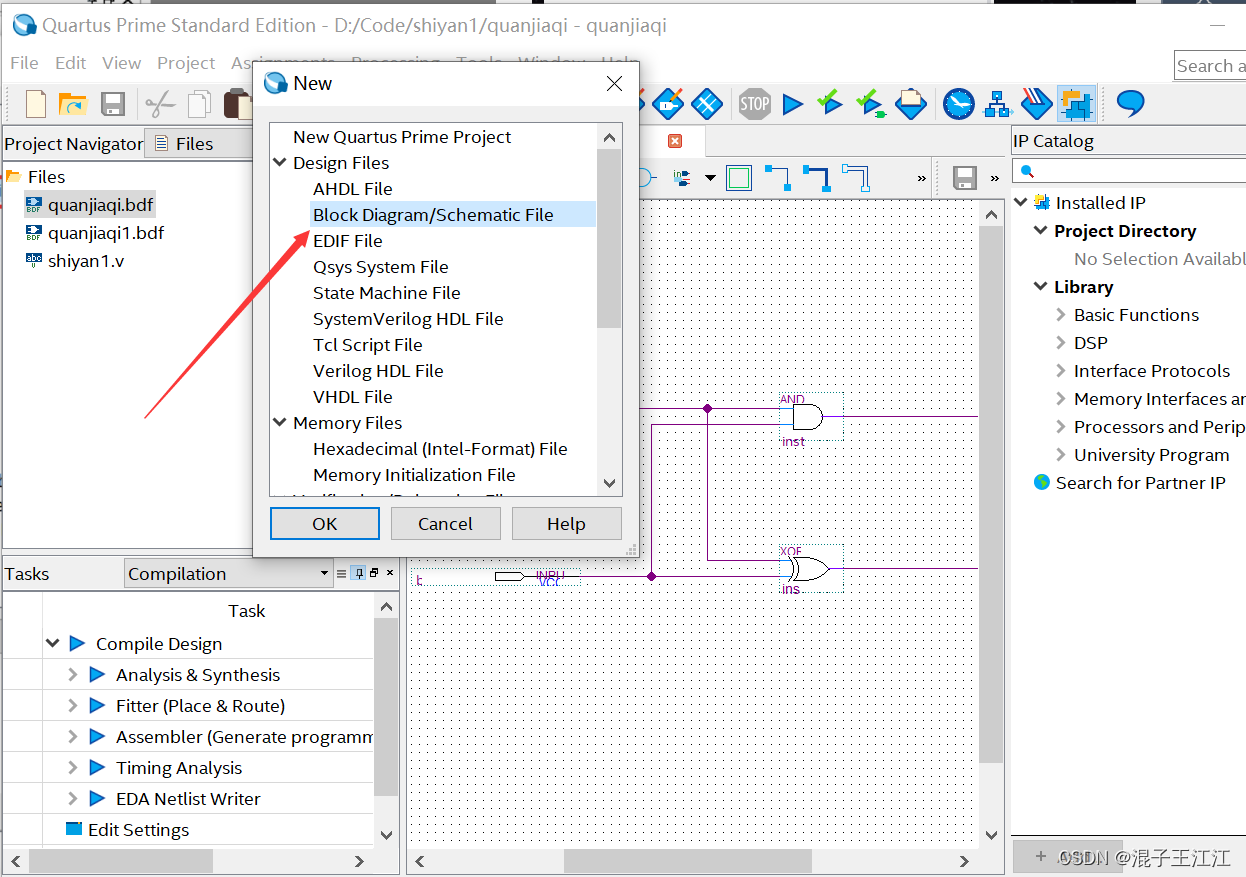

点击File->new:

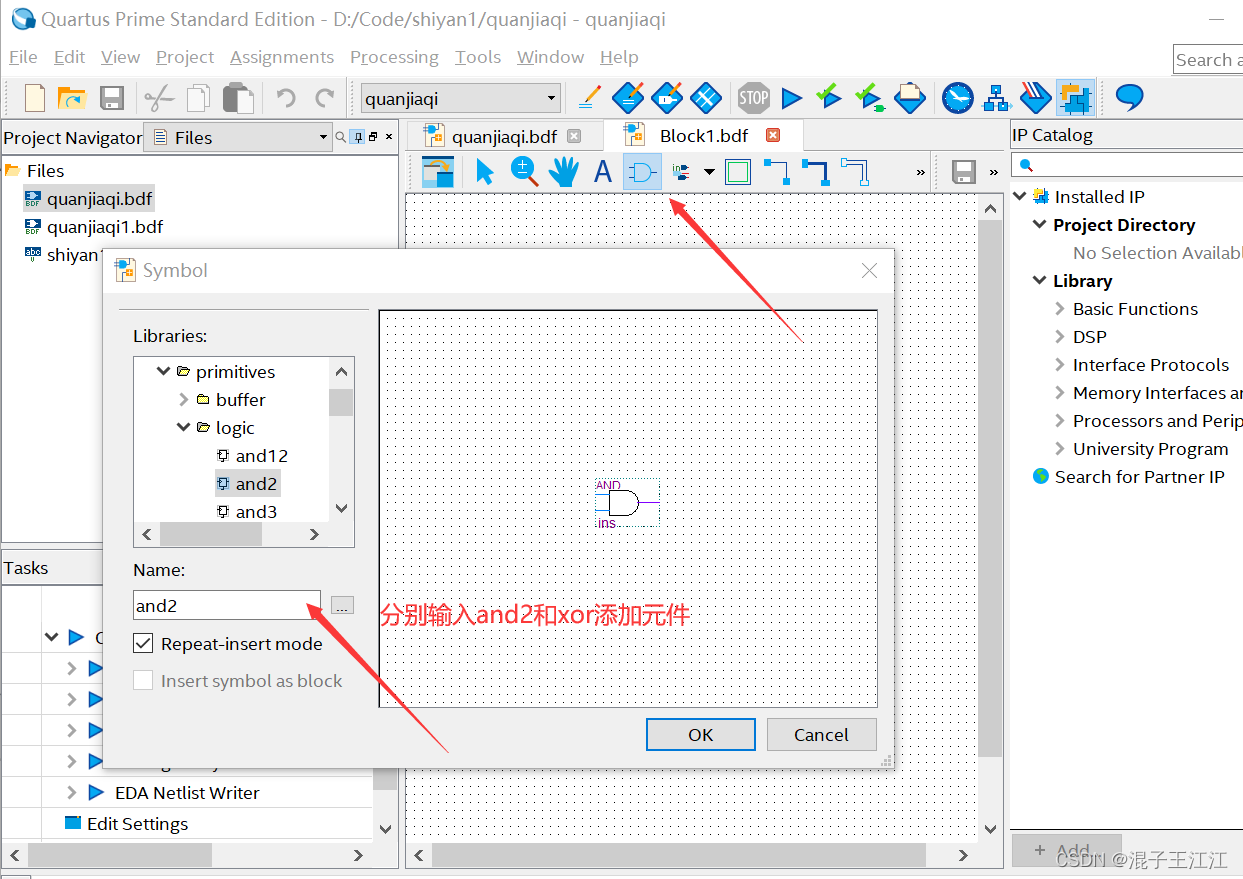

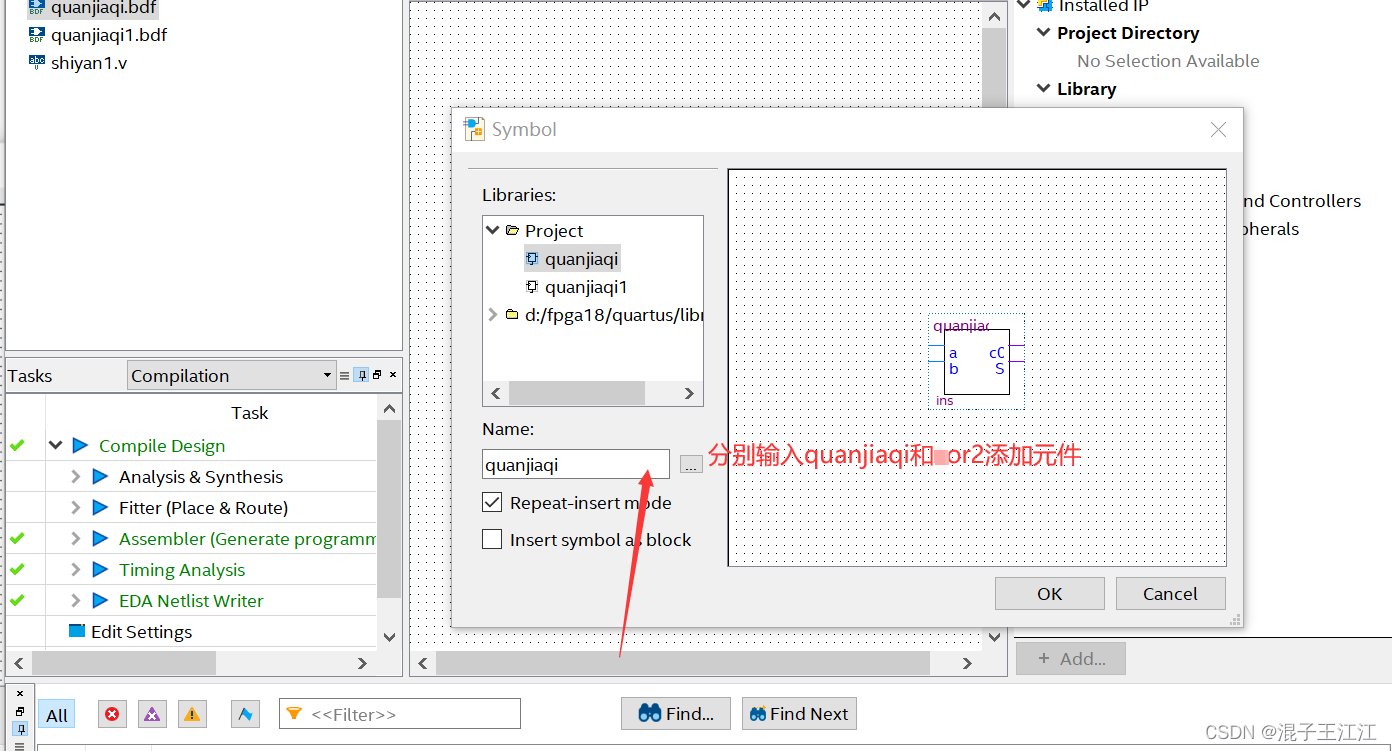

- 选择元件:

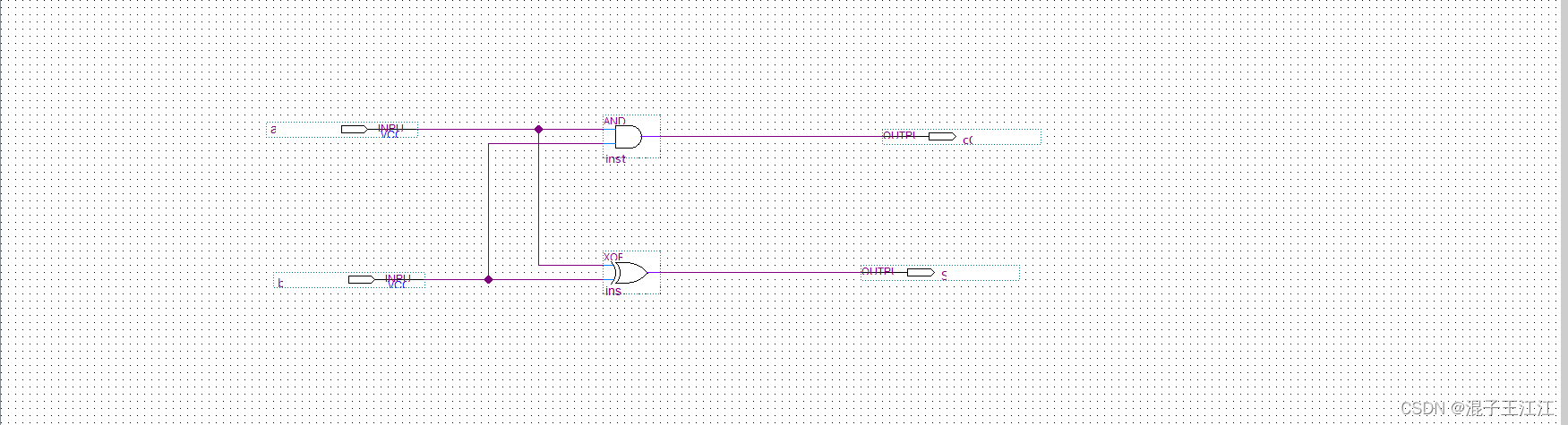

-添加输入输出通道完成设计:

- 效果:

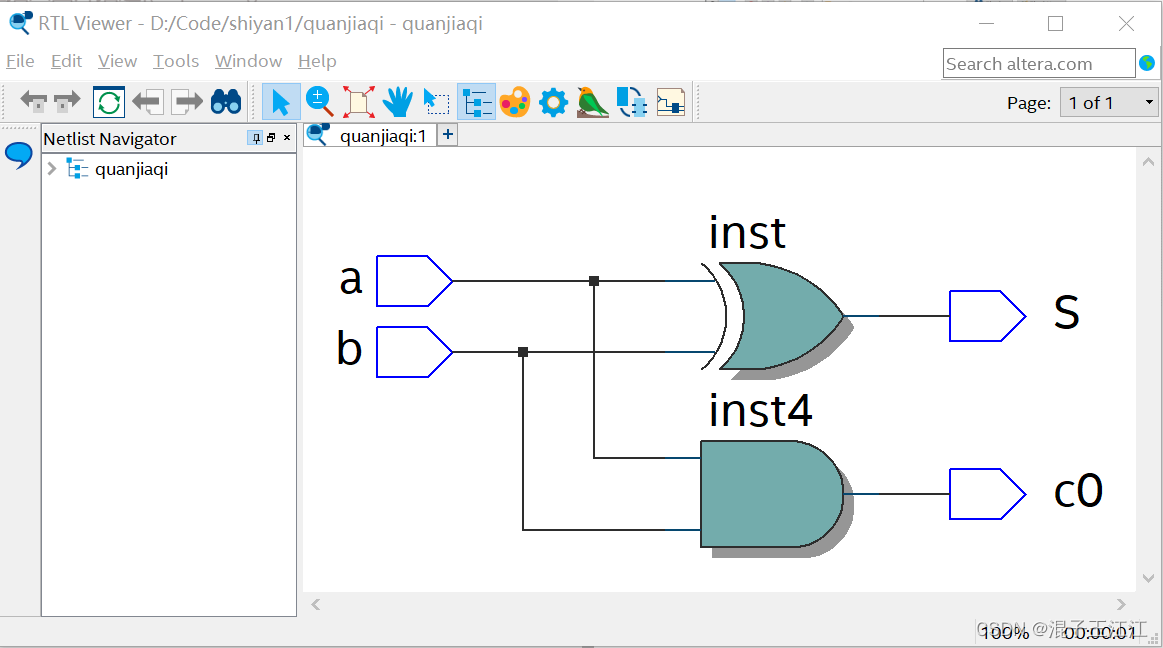

- 查看RTL图:

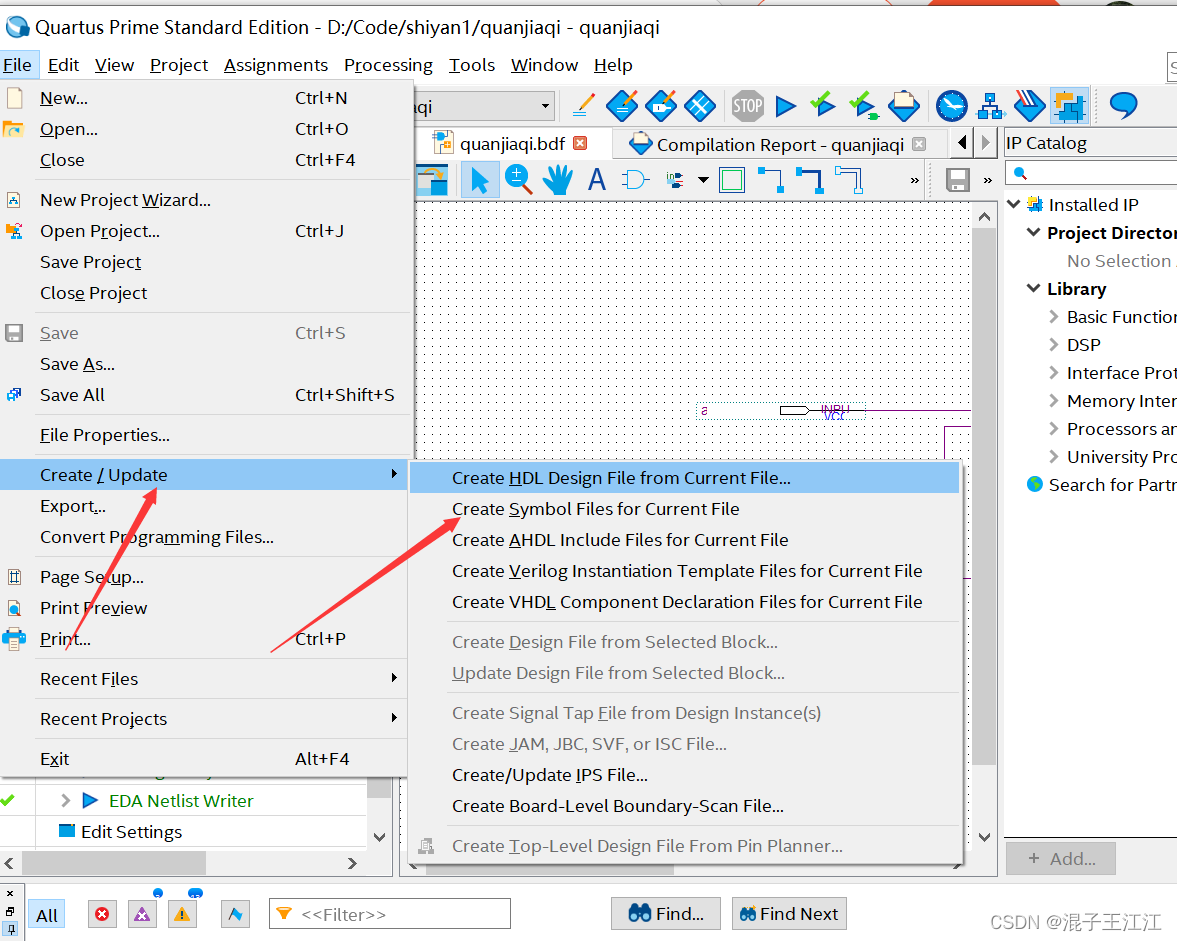

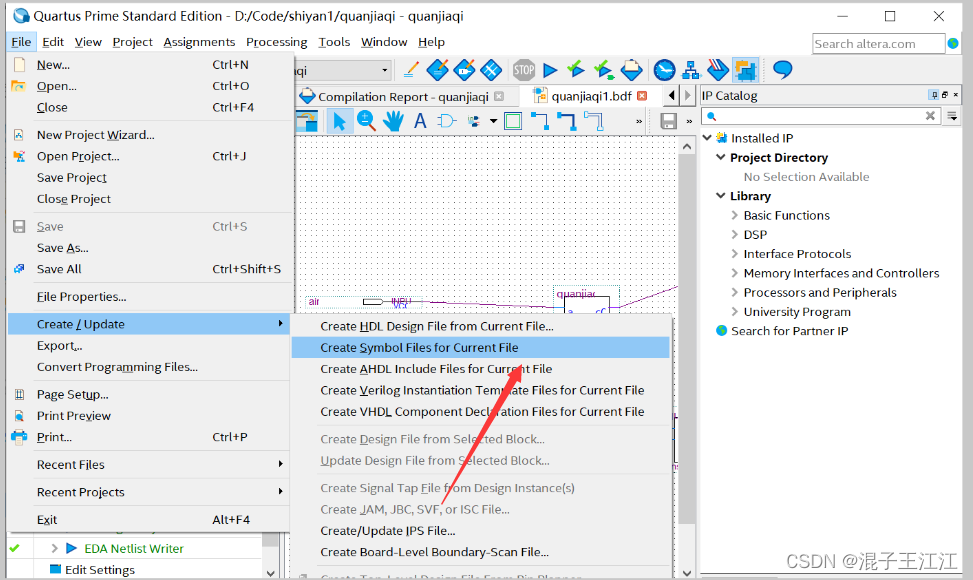

- 将设计的半加器设置为可调用的元件:

保存为half_adder,博主这里把半加器命名成了quanjiaqi

,全加器命名成了quanjiaqi1。

-

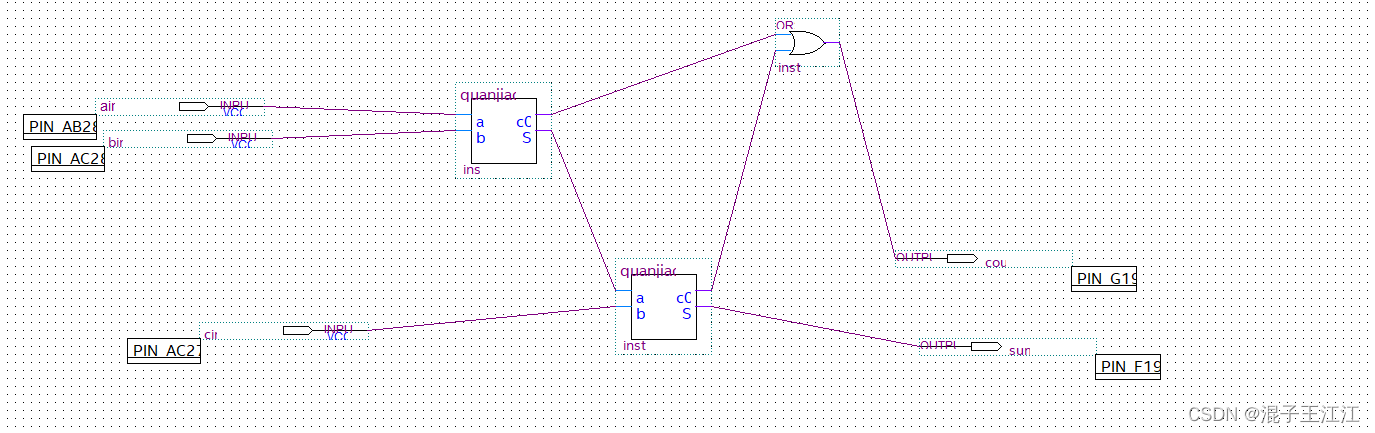

设计全加器的原理图:

-

新建文件:

-

添加元件:

扫描二维码关注公众号,回复: 15075179 查看本文章

- 效果:

- RTL图:

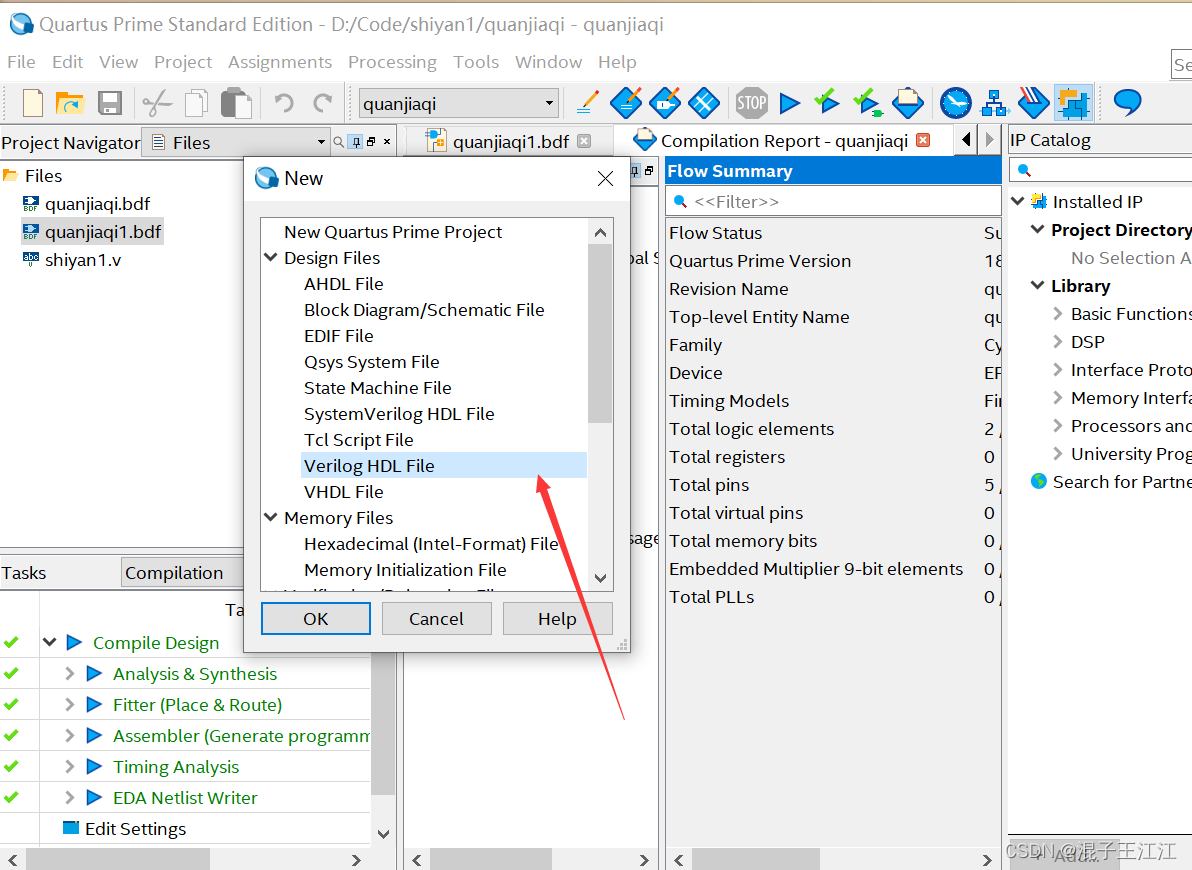

2、一位全加器的Verilog编程

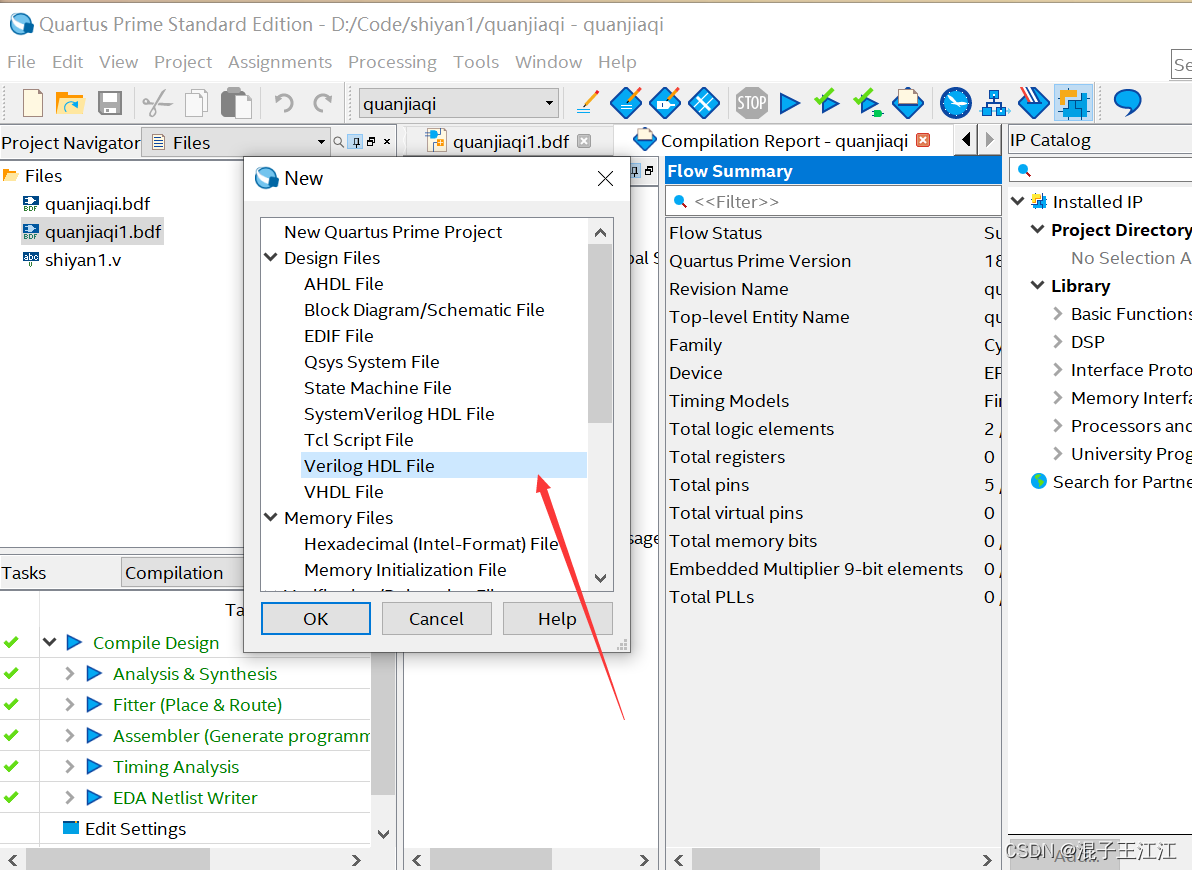

- 1、创建Verilog文件:

- 代码:

module shiyan1(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

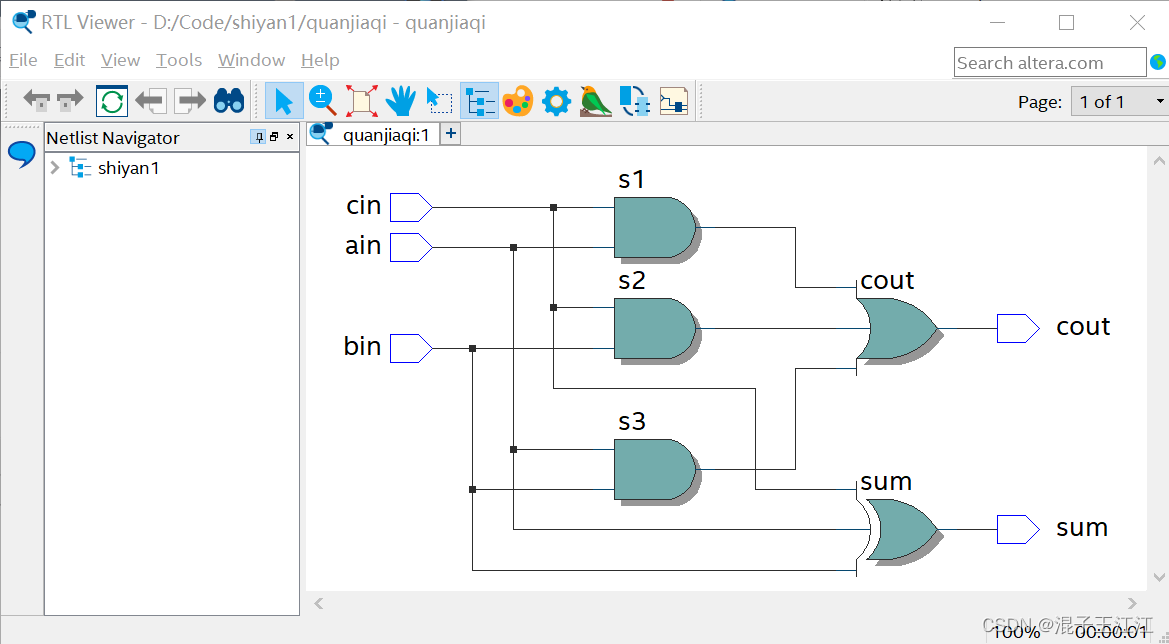

- RTL电路图:

3、上板效果

一位全加器

二、四位全加器

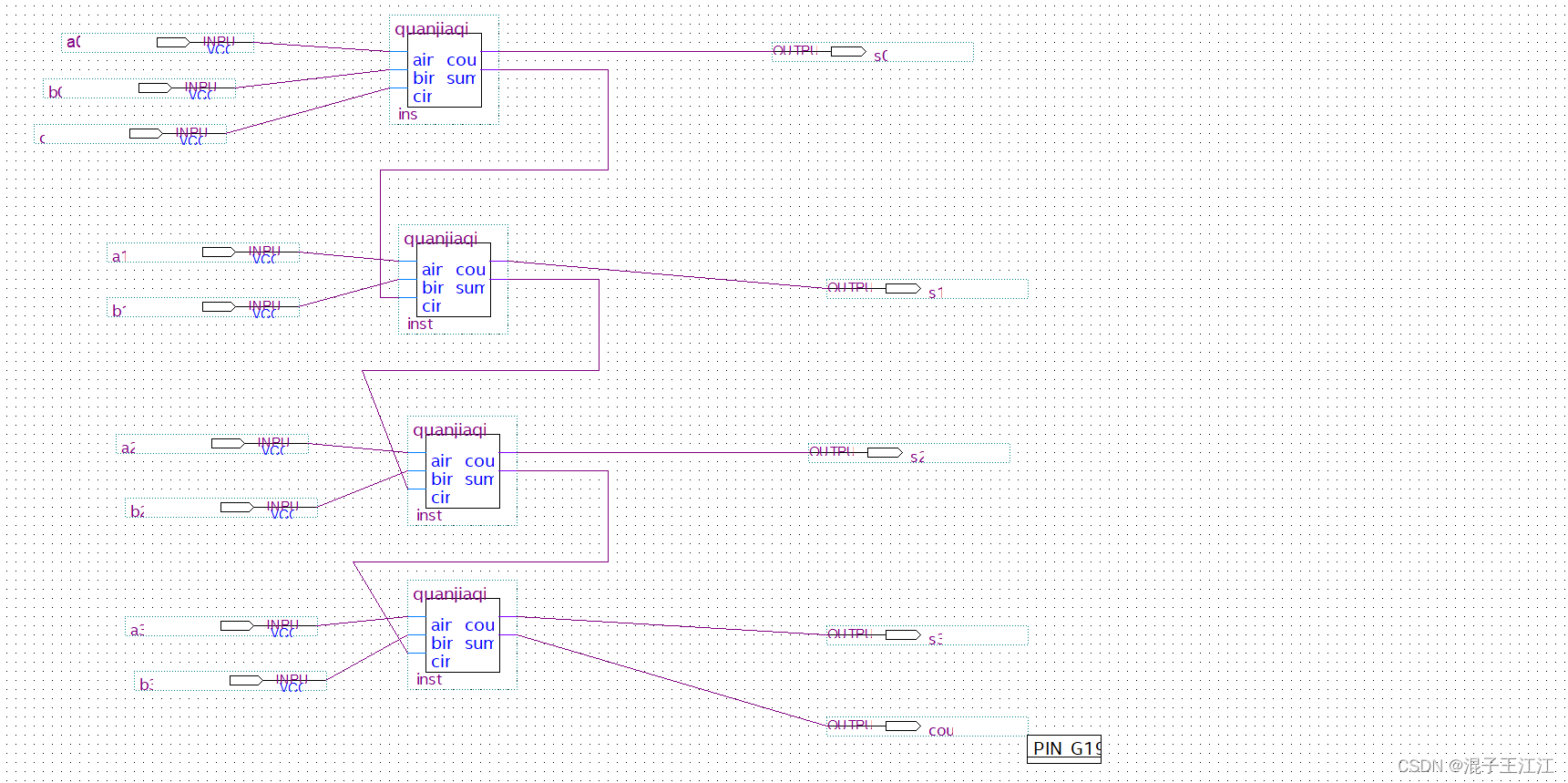

1、四位全加器的原理图设计

- 将一位全加器设置为可调用的元件:

- 原理图:

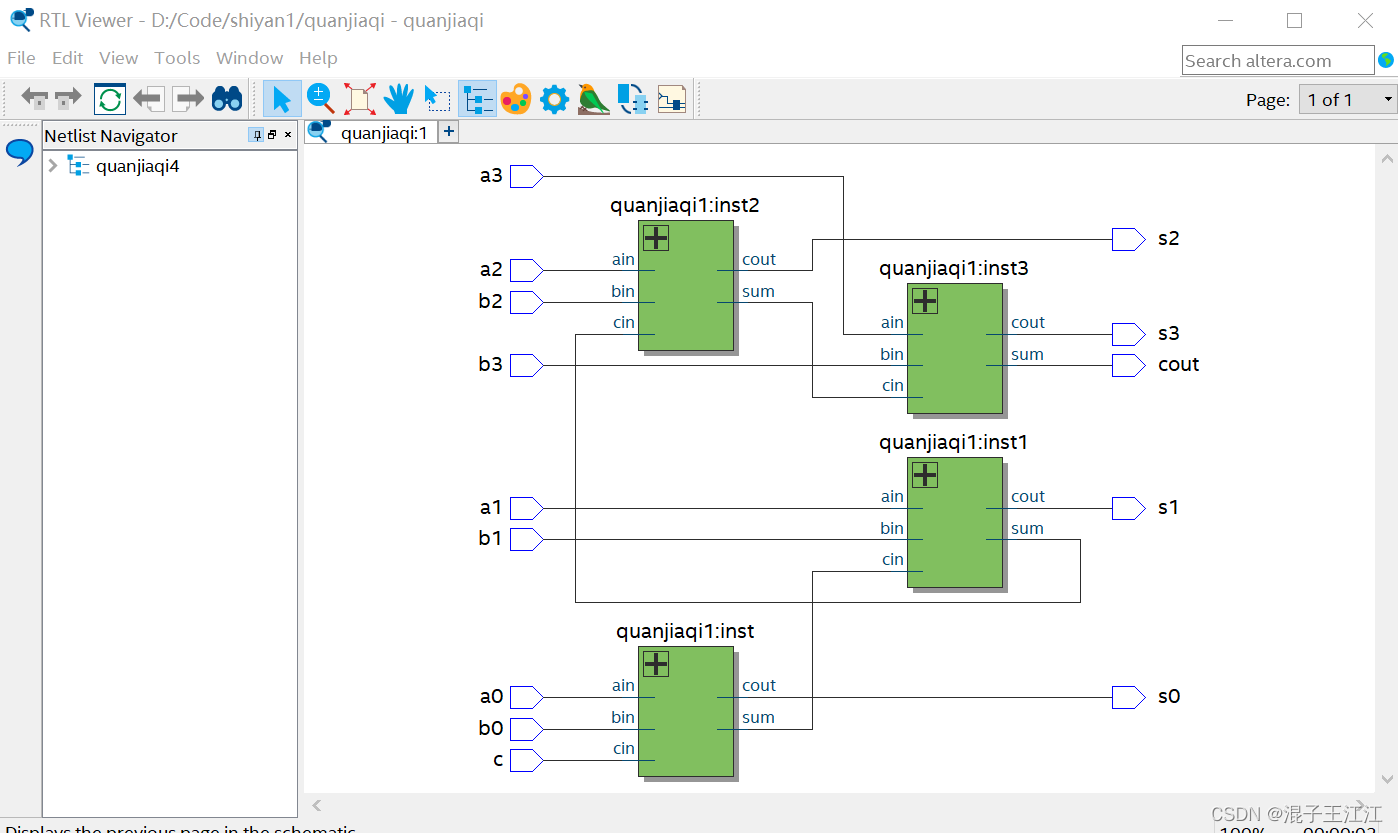

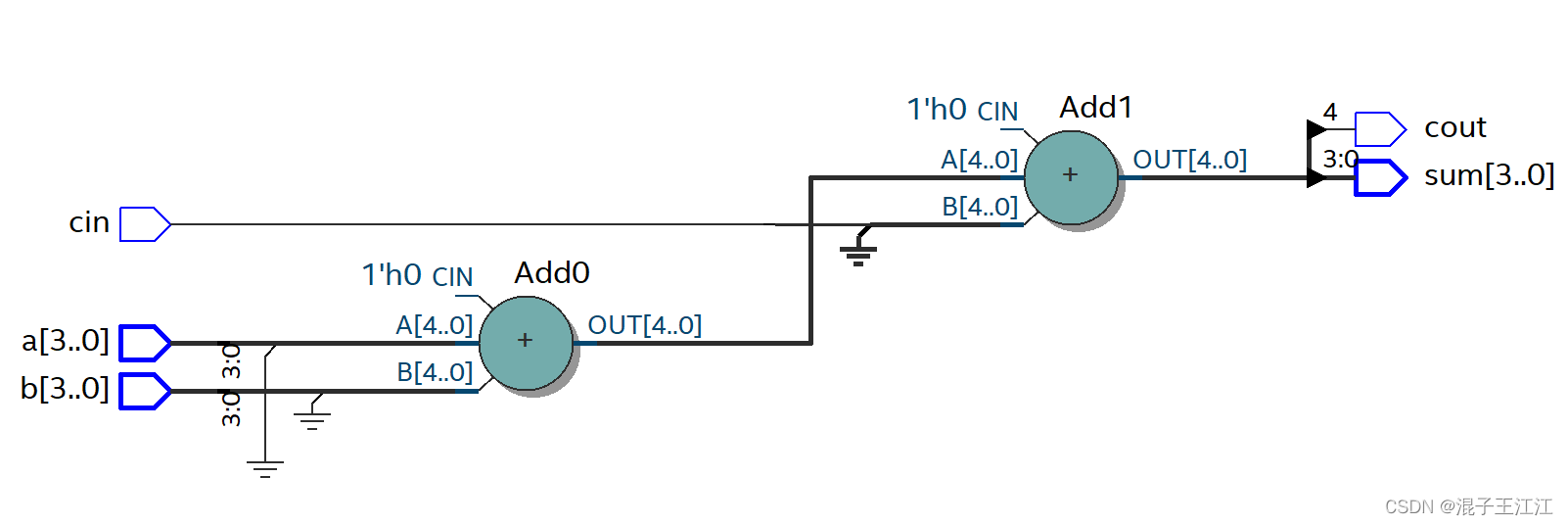

- RTL电路图:

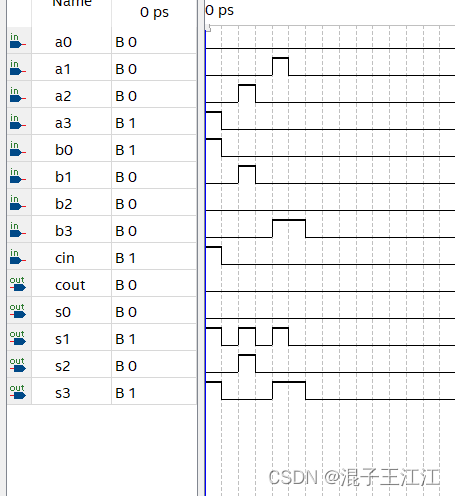

- 仿真:

2、四位全加器的Verilog 编程

- 创建文件:

- 代码:

module full_adder4(

input[3:0] a,b,

input cin,

output[3:0] sum,

output cout

);

assign{

cout,sum} = a+b+cin;

endmodule

- RTL电路图:

三、总结

由于在实验课上未完成四位加法器的操作,这里就没有了上板的效果视频。这次的实验主要就是通过全加器对FPGA知识进行入门操作,通过自己设计原理图可以更清楚的知道工程的内部连线,自由性更大,更为直观。但是,通过verilog编程能够通过编程而不去了解里面是有什么组成的而实现RTL电路图,并且工程会根据使用的资源、线路去生成相对较优的RTL电路图。