1.SPICE电路结构与网表

电路结构图:

SPICE网表:

*ADDER703

.GLOBAL vdd!

.OPTIONS LIST NODE POST

.OP

.TRAN 1N 8u

.subckt or3 a b c y

m0 net10 a 0 0 nch L=1U W=20U

m1 y net10 0 0 nch L=1U W=20U

m2 net10 c 0 0 nch L=1U W=20U

m3 net10 b 0 0 nch L=1U W=20U

m4 net14 b net033 net033 pch L=1U W=20U

m5 y net10 vdd! vdd! pch L=1U W=20U

m6 net10 c net14 net14 pch L=1U W=20U

m7 net033 a vdd! vdd! pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends or3

.subckt and2 a b y

m0 y net10 0 0 nch L=1U W=20U

m1 net10 a net3 net3 nch L=1U W=20U

m2 net3 b 0 0 nch L=1U W=20U

m3 y net10 vdd! vdd! pch L=1U W=20U

m4 net10 b vdd! vdd! pch L=1U W=20U

m5 net10 a vdd! vdd! pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends and2

.subckt xor2 a b y

m0 y a net27 net27 nch L=1U W=150U

m1 net27 b 0 0 nch L=1U W=150U

m2 y net11 0 0 nch L=1U W=150U

m3 net11 b 0 0 nch L=1U W=150U

m4 net11 a 0 0 nch L=1U W=150U

m5 net11 b net020 net020 pch L=1U W=5U

m6 net020 a vdd! vdd! pch L=1U W=5U

m7 net018 net11 vdd! vdd! pch L=1U W=5U

m8 net018 a y y pch L=1U W=5U

m9 net018 b y y pch L=1U W=5U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends xor2

xi3 net13 net10 net7 cout or3

xi5 b cin net7 and2

xi4 cin a net10 and2

xi2 a b net13 and2

xi1 net14a cin sum xor2

xi0 a b net14 xor2

VA a gnd PULSE 0 5 0N 1N 1N 1u 2u

VB b gnd PULSE 0 5 0N 1N 1N 2u 4u

VC cin gnd PULSE 0 5 0N 1N 1N 4u 8u

V1 vdd! 0 dc=5

.measure tran tpdr trig v(a) val=2.5 rise=2 targ v(sum) val=2.5 fall=2

.measure tran tpdf trig v(a) val=2.5 rise=2 targ v(cout) val=2.5 fall=2

.measure tpd param='(tpdr+tpdf)/2'

.END

电路结构图:

SPICE网表:

*ADDER703

.GLOBAL vdd!

.OPTIONS LIST NODE POST

.OP

.TRAN 1N 8u

.subckt or2 a b y

m0 y 2 0 0 nch L=1U W=20U

m1 2 a 0 0 nch L=1U W=20U

m2 2 b 0 0 nch L=1U W=20U

m3 y 2 vdd! vdd! pch L=1U W=20U

m4 1 a vdd! vdd! pch L=1U W=20U

m5 2 b 1 1 pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends or2

.subckt and2 a b y

m0 y net10 0 0 nch L=1U W=20U

m1 net10 a net3 net3 nch L=1U W=20U

m2 net3 b 0 0 nch L=1U W=20U

m3 y net10 vdd! vdd! pch L=1U W=20U

m4 net10 b vdd! vdd! pch L=1U W=20U

m5 net10 a vdd! vdd! pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends and2

.subckt nor2 a b y

m0 y a 0 0 nch L=1U W=20U

m1 y b 0 0 nch L=1U W=20U

m2 y a 1 1 pch L=1U W=20U

m3 1 b vdd! vdd! pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends nor2

.subckt or3 a b c y

m0 net10 a 0 0 nch L=1U W=20U

m1 y net10 0 0 nch L=1U W=20U

m2 net10 c 0 0 nch L=1U W=20U

m3 net10 b 0 0 nch L=1U W=20U

m4 net14 b net033 net033 pch L=1U W=20U

m5 y net10 vdd! vdd! pch L=1U W=20U

m6 net10 c net14 net14 pch L=1U W=20U

m7 net033 a vdd! vdd! pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends or3

.subckt and3 a b c y

m0 y 1 0 0 nch L=1U W=20U

m1 1 a 2 2 nch L=1U W=20U

m2 2 b 3 3 nch L=1U W=20U

m3 3 c 0 0 nch L=1U W=20U

m4 y 1 vdd! vdd! pch L=1U W=20U

m5 1 c vdd! vdd! pch L=1U W=20U

m6 1 b vdd! vdd! pch L=1U W=20U

m7 1 a vdd! vdd! pch L=1U W=20U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends and3

.subckt inv a y

m0 y a 0 0 nch L=1U W=150U

m1 y a vdd! vdd! pch L=1U W=150U

.MODEL NCH NMOS LEVEL=1

.MODEL PCH PMOS LEVEL=1

.ends inv

xi0 a b 1 or2

xi1 1 cin 2 and2

xi2 a b 3 and2

xi3 2 3 4 nor2

xi4 4 cout inv

xi5 a b cin 5 or3

xi6 4 5 6 and2

xi7 a b cin 7 and3

xi8 6 7 8 nor2

xi9 8 sum inv

VA a gnd PULSE 0 5 0N 1N 1N 1u 2u

VB b gnd PULSE 0 5 0N 1N 1N 2u 4u

VC cin gnd PULSE 0 5 0N 1N 1N 4u 8u

V1 vdd! 0 dc=5

.measure tran tpdr trig v(a) val=2.5 rise=2 targ v(sum) val=2.5 fall=2

.measure tran tpdf trig v(a) val=2.5 rise=2 targ v(cout) val=2.5 fall=2

.measure tpd param='(tpdr+tpdf)/2'

.END

2.电路仿真结果-基础部分

文件中:

修改后:

3.实验结果分析

一位全加器的真值表

实验结果与真值表吻合。

文件中-sum:

修改后-sum:

文件中-cout:

修改后-cout:

文件中&修改后-a:

文件中&修改后-b:

文件中&修改后-cin:

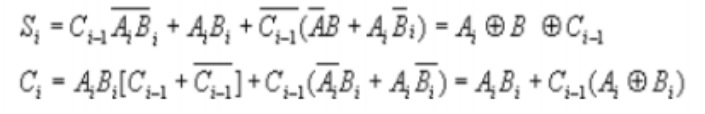

首先,根据真值表,可以写出如下的表达式:

然后分析两种电路:

两种电路均可实现全加器的功能

第一种已给的电路中,一共使用3个与门,2个异或门,1个或门,共使用6个门,一共46个晶体管

第二种电路中一共使用4个与门,2个或非门,2个或门,2个非门,共使用10个门

两电路图相比,第一个逻辑上更简单,容易理解,并且在实现上由于使用的门的个数更少,种类更少,并且每种门的输入数目相同,因此实现起来更方便;第二个电路逻辑上更复杂,虽然也能通过化简或真值表证明与第一种是相同的,但使用的门的种类和个数都更多,并且每种门有的是2输入的有的是3输入的,需要写成不一样的,晶体管就更多了,实现较麻烦

这一点可以从我们计算的延迟时间中看出来:

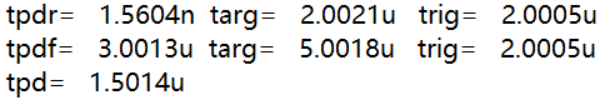

首先是文件中的电路和网表文件产生的延迟时间:

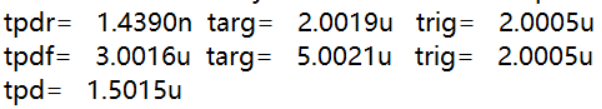

然后是我们修改后的电路得到的延迟时间:

可以看到,修改后的电路的延迟时间相对之前文件的延迟时间大了一点,这与我们的理论计算似乎有冲突。因为按照我们的计算,我们修改后的电路虽然所用的门比较多,但因为减少掉了一个xor门,所用的时间应该会比之前的短。这是因为,我们文件中的pmos和nmos的宽长比并不是固定的,而是有多组值,所以才导致了这样的结果。