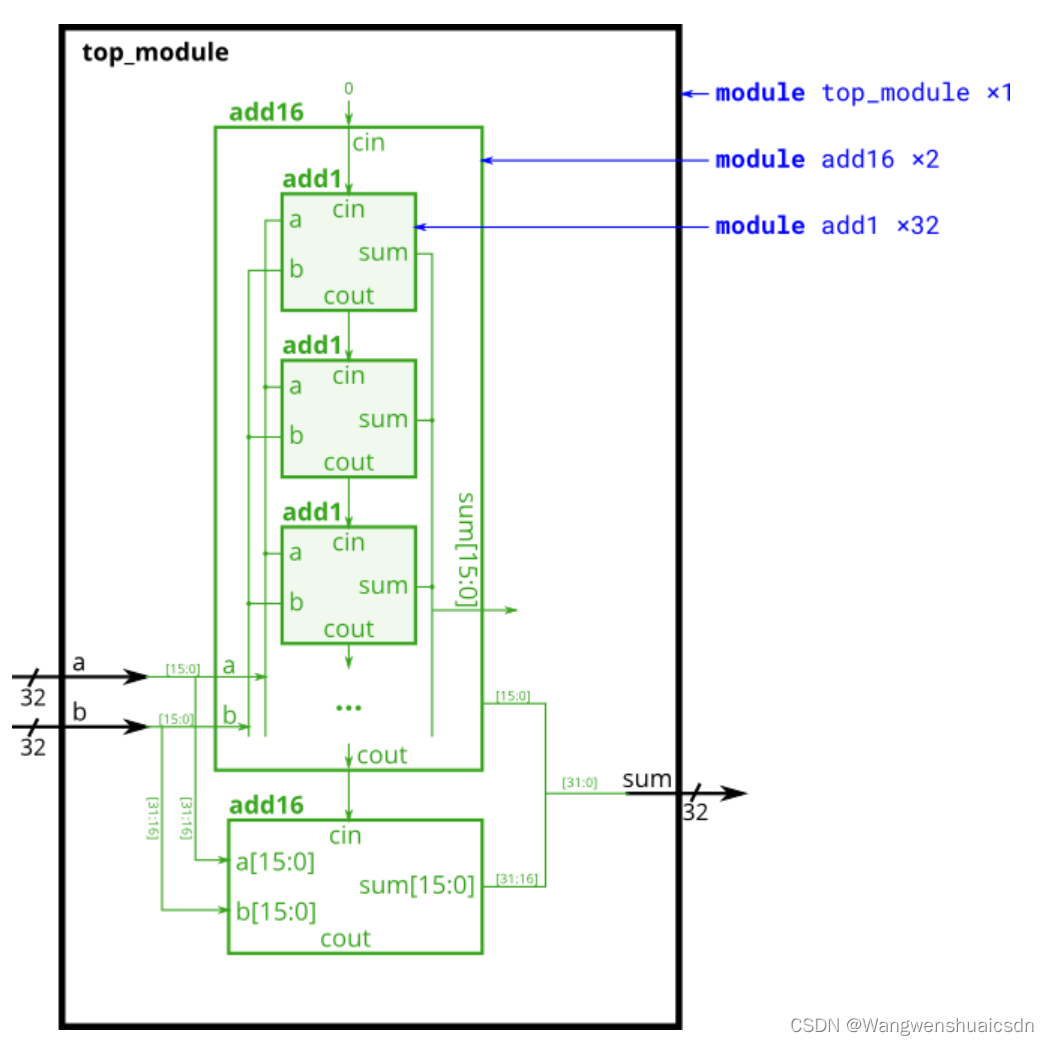

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0] low;

wire [15:0] heigh;

wire wire1;

add16 add16_low(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(low),

.cout(wire1)

);

add16 add16_heigh(

.a(a[31:16]),

.b(b[31:16]),

.cin(wire1),

.sum(heigh),

.cout()

);

assign sum = {

heigh,low};

endmodule

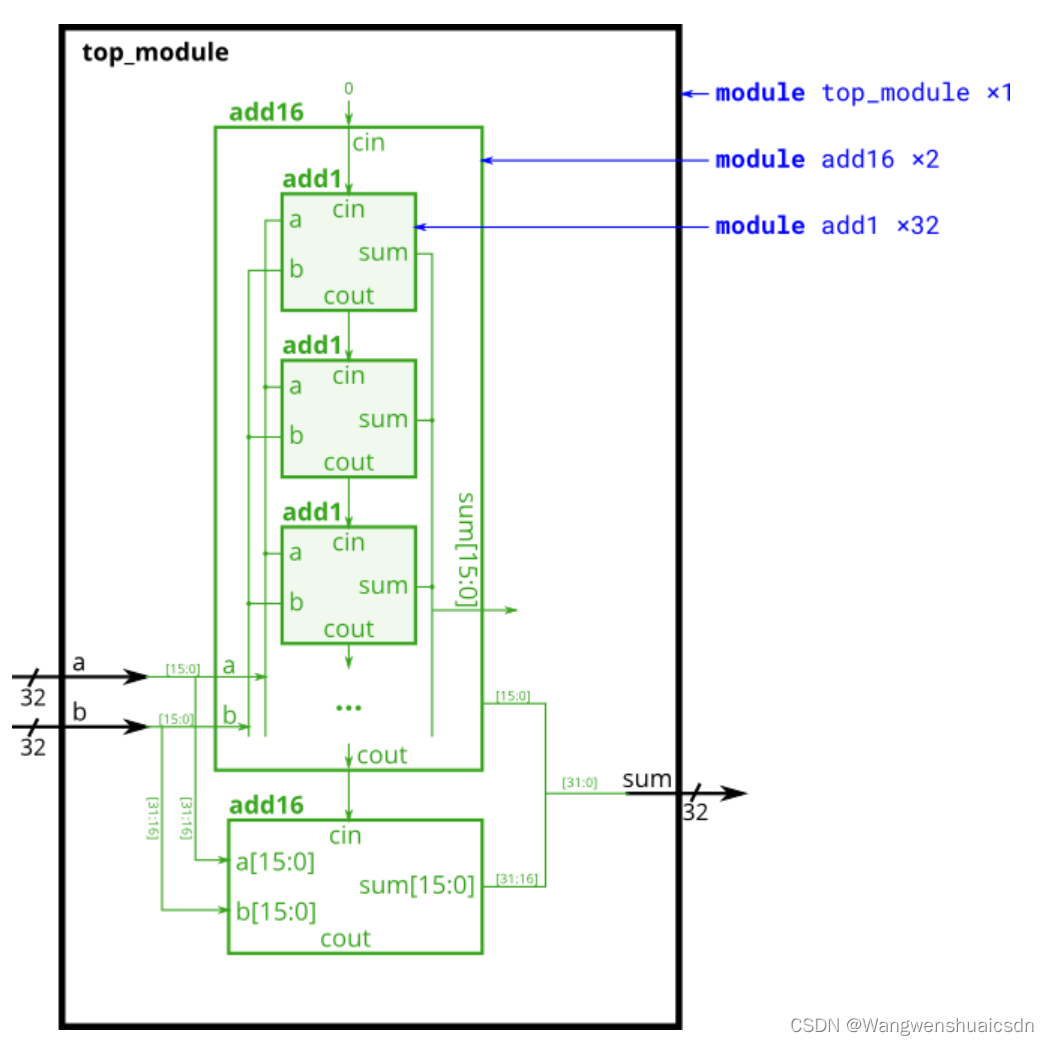

module add1 ( input a, input b, input cin, output sum, output cout );

reg sum1;

reg cout1;

always @( *) begin

case (a + b + cin)

1'b0:begin

cout1 <= 1'b0;

sum1 <= 1'b0;

end

1'b1:

begin

cout1 <= 1'b0;

sum1 <= 1'b1;

end

2'b10:

begin

cout1 <= 1'b1;

sum1 <= 1'b0;

end

2'b11:

begin

cout1 <= 1'b1;

sum1 <= 1'b1;

end

endcase

end

assign sum = sum1;

assign cout = cout1;

endmodule