前言

在上一篇文章中,已经实现了一位加法器,在此基础上,下文将用原理图与Verilog编程两种方式,完成四位加法器的设计。

下文步骤将不进行详细讲述,如有看不懂的地方,详见上一篇文章

1 原理图实现

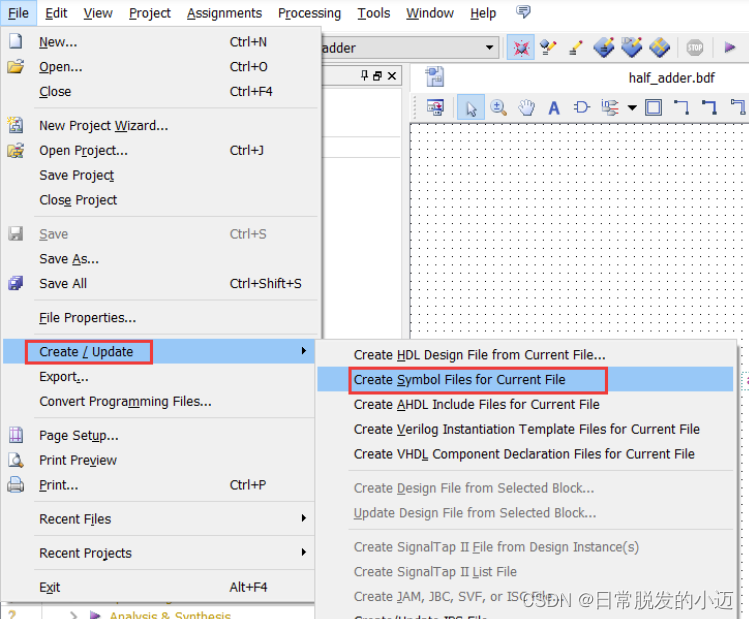

1.1 模块引入

将上一篇博客中所做的一位加法器作为引入模块使用

此处需要将引入的模块与下文新建文件在同一项目中

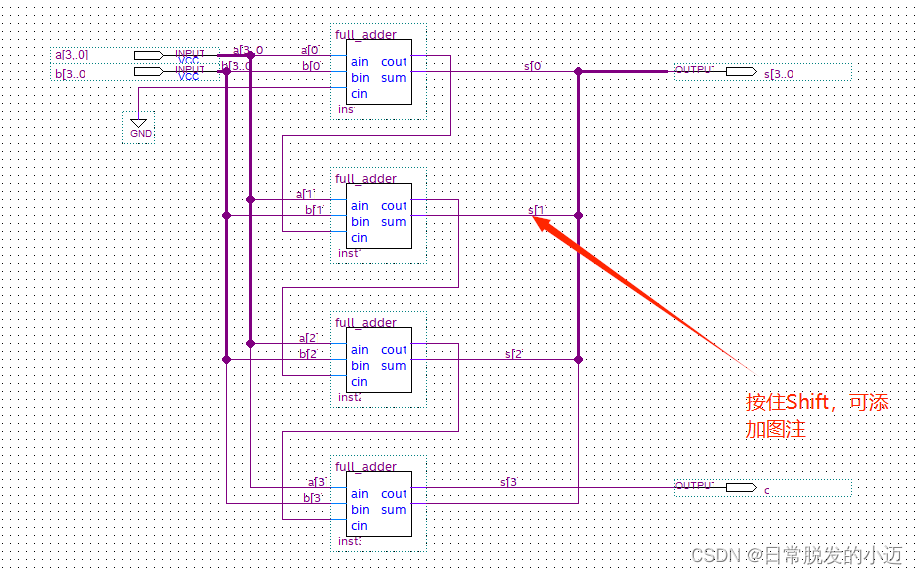

1.2 建原理图

新建原理图文件File->New->Block Diagram/Schematic File

选择元件(四个fulladder,两个input,两个output,两个gnd)

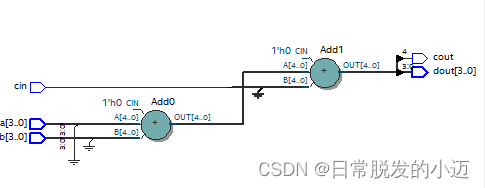

编辑原理图如下:

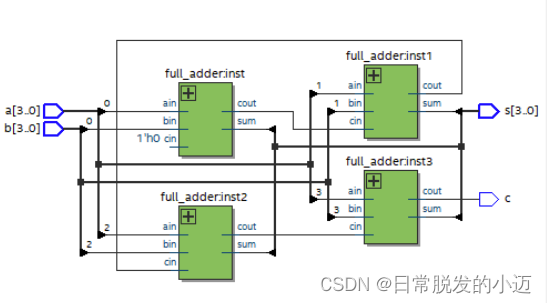

1.3 编译并仿真

保存编译后,查看原理图如下:

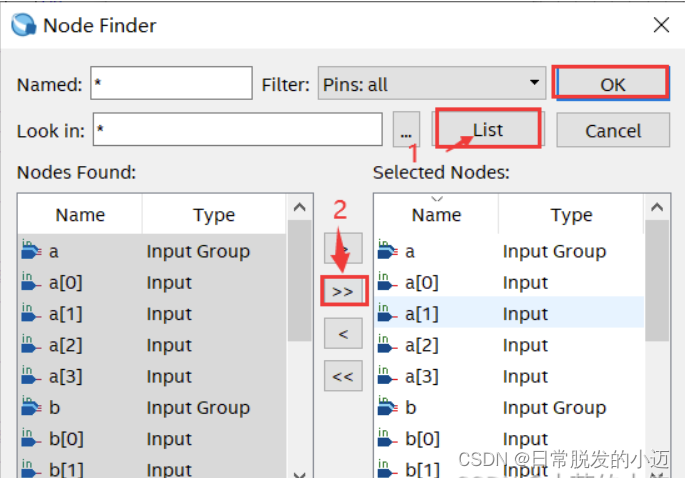

创建一个向量波形文件,选择菜单项 File→New->VWF,添加信号

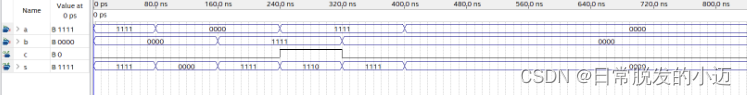

仿真结果如下:

2 Verilog实现

2.1 创建Verilog文件

不做赘述,上篇博客有讲解

添加代码如下:

module four_bit(a,b,cin,cout,dout);

//与保存的文件名相同,但尽量不与之前的原理图名相同

input [3:0] a,b; //a,b为4位输入

input cin;

output cout;

output [3:0] dout;

assign {

cout,dout} = a+b+cin; //a+b 加法操作

//使用拼接运算符将cout、dout拼接,dout取结果中的低四位

endmodule

2.2 编译并仿真

保存编译后,查看原理图,结果如下:

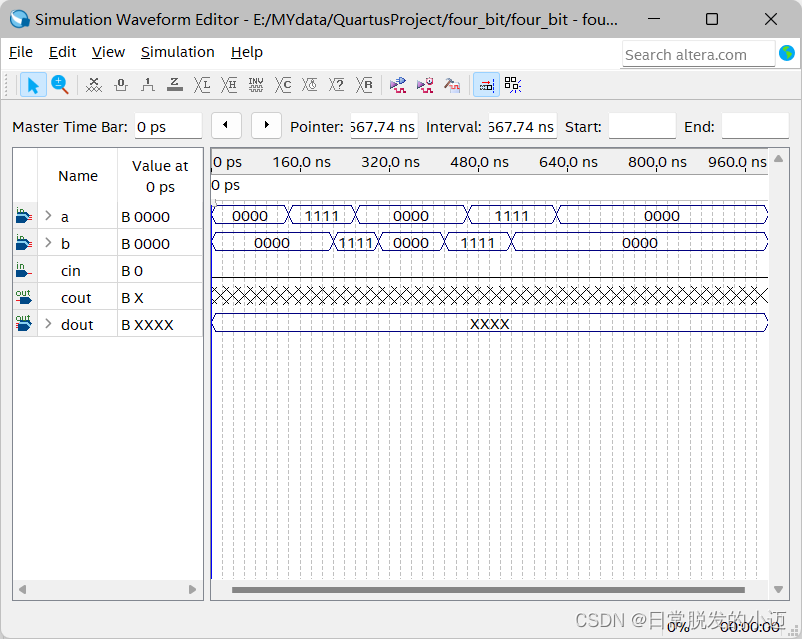

新建一个波形图仿真,还是file,new

添加并编辑信号

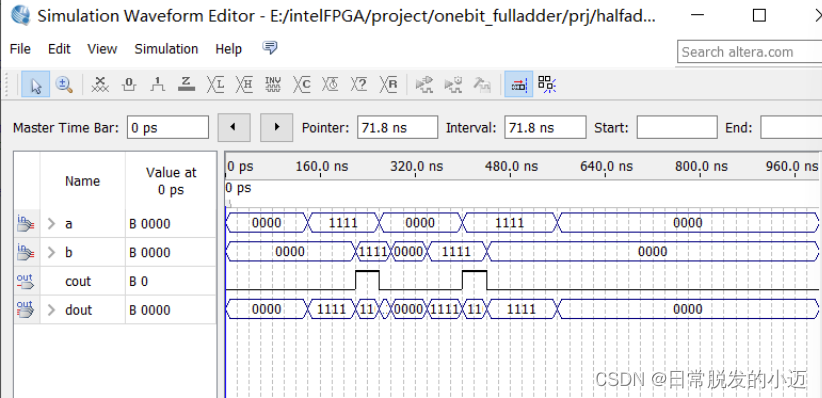

仿真结果如下:

总结

由于上一篇文章步骤较为详细,本次四位加法器的实现步骤省略了一部分,详情可参考上一篇文章。四位加法器是在一位加法器的基础上实现的。

参考:

https://blog.csdn.net/weixin_47554309/article/details/123743633