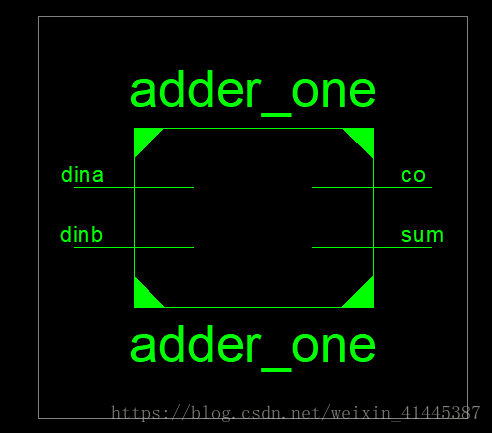

使用ISE设计一个加法器(半加器):

dina (输入)dinb(输出) co(进位输出)sum(和输出)

代码如下:

module adder_one(dina,dinb,sum,co

);

input dina;

input dinb;

output sum;

output co;

assign {co,sum}= dina + dinb ;

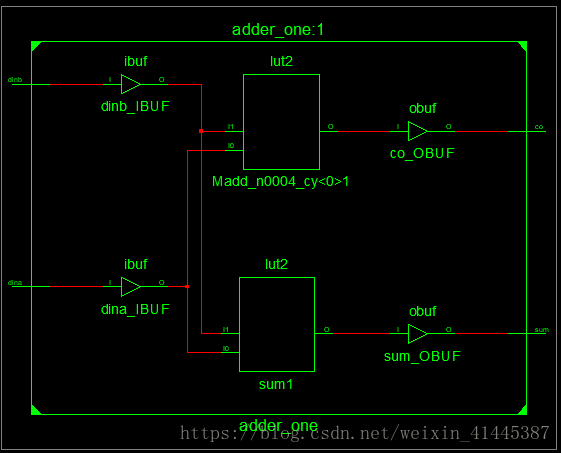

endmodule查看技术原理图:

内部结构:其中 XBUF表示 缓冲

输入输出同时有缓冲不影响数据的值

module tb_adder_one;

// Inputs

reg dina;

reg dinb;

// Outputs

wire sum;

wire co;

// Instantiate the Unit Under Test (UUT)

adder_one uut (

.dina(dina),

.dinb(dinb),

.sum(sum),

.co(co)

);

initial begin

// Initialize Inputs

dina = 0;

dinb = 0;

// Wait 100 ns for global reset to finish

#100;

dina = 1'b1;

dinb = 1'b0;

#100;

dina = 1'b0;

dinb = 1'b1;

#100;

dina = 1'b1;

dinb = 1'b1;

// Add stimulus here

end

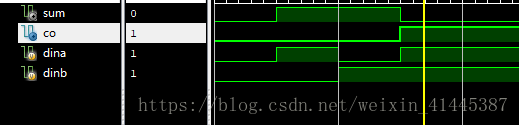

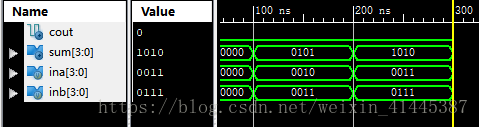

endmodule仿真示意波形图:

从波形图中可以看出加法器的输入和输出的规律

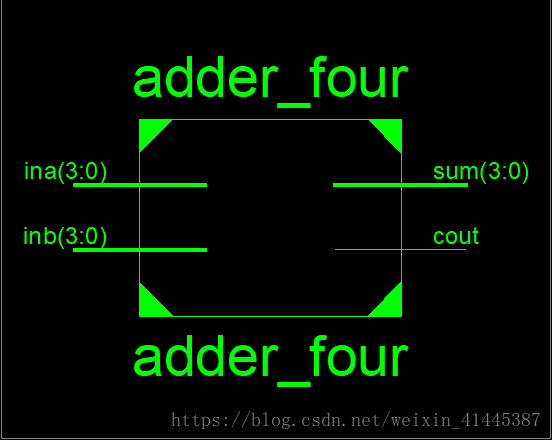

课后作业:设计一个4位的半加法器

代码如下:

module adder_four(cout,sum,ina,inb

);

output[3:0] sum;

output cout;

input[3:0] ina,inb;

assign {cout,sum}=ina+inb;

endmodule

仿真如下:

4位全加器和一位全加器只是多了一个低位进位位Ci

示意图如下: