还是以38译码器为例子

vhdl常用的语法无非就

用在进程下边:

1.if-else-elsif-end if;

2. case x is

when " “=>b<=” “;

when others=>b<=“Z”;

end case;

用在结构体下

1.a<=” “when b=” " else

" “when b=” "else

“Z”;

2 with a select

" " when " ",

" " when " ",

" "when others;

下边还是以38译码器为例

1.用conv_integer做

一定要加unsigned包

代码:

--ujs-lili;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity my3_8 is

port(a:in std_logic_vector(2 downto 0);

b:out std_logic_vector(7 downto 0));

end my3_8;

architecture Behavioral of my3_8 is

begin

process(a)

begin

b<=(others=>'1');

b(conv_integer(a))<='0';

end process;

end Behavioral;

如果这个conv_integer不放在process中的话。b是不会出来正确结果的

2.when-else

放在结构体下面

--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity my3_8_2 is

port(a : in std_logic_vector(2 downto 0);

b : out std_logic_vector(7 downto 0));

end my3_8_2;

architecture Behavioral of my3_8_2 is

begin

b<="11111110"when a="000" else

"11111101" when a="001" else

"11111011" when a="010" else

"11110111" when a="011" else

"11101111" when a="100" else

"11011111" when a="101" else

"10111111" when a="110" else

"01111111" when a="111" else

"ZZZZZZZZ";

end Behavioral;

3.with-select

放在结构体下边,其实和when-else 差不多

--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity my38_3 is

port(a:in std_logic_vector(2 downto 0);

b:out std_logic_vector(7 downto 0));

end my38_3;

architecture Behavioral of my38_3 is

begin

with a select

b<="11111110"when "000" ,

"11111101" when "001" ,

"11111011" when "010" ,

"11110111" when "011" ,

"11101111" when "100" ,

"11011111" when "101" ,

"10111111" when "110" ,

"01111111" when "111" ,

"ZZZZZZZZ" when others;

end Behavioral;

就改了几个地方,1.with-select语句,2去掉else,变“,”。3.when others。

4.case

放在process中

--ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity my38_4 is

port(a : in std_logic_vector(2 downto 0);

b : out std_logic_vector(7 downto 0));

end my38_4;

architecture Behavioral of my38_4 is

begin

process(a)

begin

case a is

when "000"=>b<="11111110";

when "001"=>b<="11111101";

when "010"=>b<="11111011";

when "011"=>b<="11110111";

when "100"=>b<="11101111";

when "101"=>b<="11011111";

when "110"=>b<="10111111";

when "111"=>b<="01111111";

when others=>b<="ZZZZZZZZ";

end case;

end process;

end Behavioral;

说明:以上代码都是经过仿真的

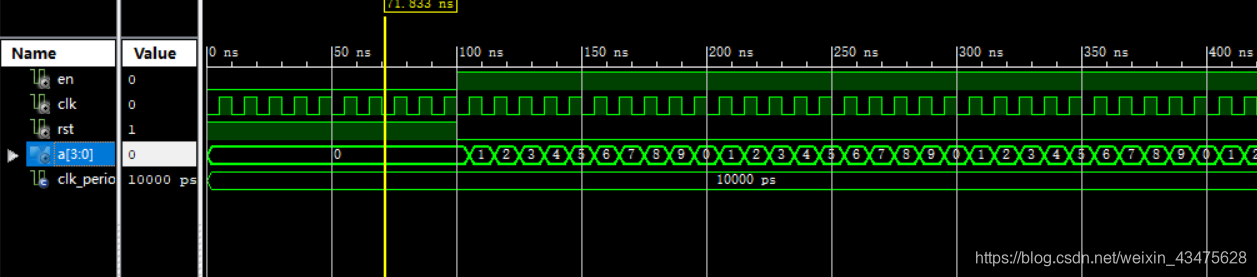

下面再做一个10进制加法计数器

功能:异步复位,上升沿加一

--ujs_lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;--这个一定要有

use IEEE.STD_LOGIC_arith.ALL;--这里可以不用的,你用*才要这个

entity shijinzhi is

port(en,clk:in std_logic;

rst: in std_logic;

a:out std_logic_vector(3 downto 0));

end shijinzhi;

architecture Behavioral of shijinzhi is

signal a1: std_logic_vector(3 downto 0):="0000";

begin

process(clk,rst)

begin

if rst='1' then

a1<="0000";--如果你不是写的a1,仿真就会错,但是a1不会错

elsif clk'event and clk='1' then

if a1 = "1001" then

a1<="0000";

else

a1<=a1+'1';

end if;

end if;

end process;

a<=a1;

end Behavioral;

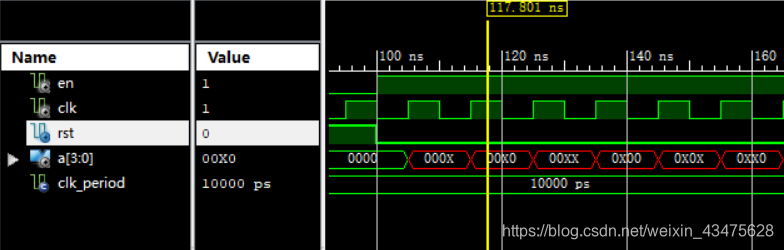

仿真

如果if …a<=“0000”;

正确:

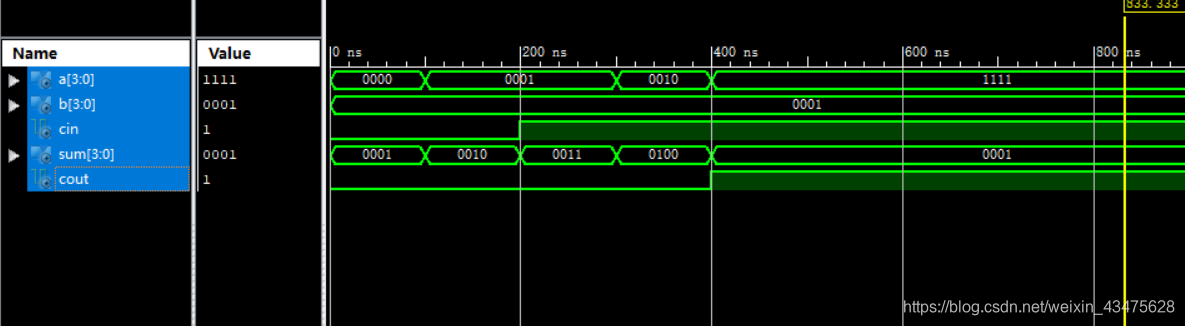

下面再做一个四位二进制的加法器

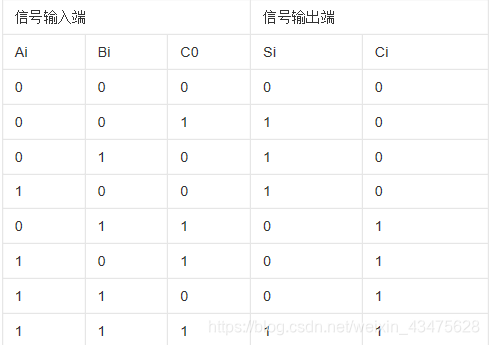

先弄清楚什么是半加器

就是两个二进制数相加,然后理论上说

0 0 0

0 1 1

1 0 1

1 1 2 那我们都知道2是不对的,此时的结果在半加器的输出是0,进位是1,就像微机原理中的溢出一样。

这就,诞生了全加器,其实就是带进位的半加器

s=a异或b异或c0;

ci=ab+(a异或b)与cin;

首先得搞明白什么是四位二进制的加法器

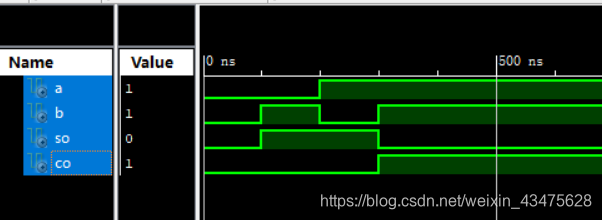

半加器:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity banjiaqi is

port (a,b : in std_logic;

so,co: out std_logic);

end banjiaqi;

architecture Behavioral of banjiaqi is

begin

so<=a xor b;--逻辑运算之间是不可以用加

co<=a and b;

end Behavioral;

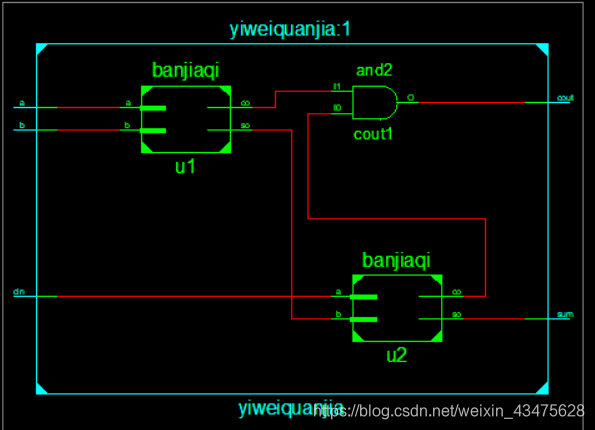

为什么两个半加器加一个与门可以得到一个全加器呢?

你看半加器的输出

so=ain xor bin;

co= ain and bin;

你看全加器的输出

so=ain xor bin xor cin;

co= ain and bin +(ain xor bin )and cin ;

你应该可以看出来只要把第一个半加器的so和cin作为第二个半加器的输入

那么第二个半加器的输出为:

so=ain xor bin xor cin;

co=(ain xor bin )and cin ;

最后再加一个和第一个半价器的co=ain and bin;或门相连ok

仿真:

代码:

--半加器

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity banjiaqi is

port (a,b : in std_logic;

so,co: out std_logic);

end banjiaqi;

architecture Behavioral of banjiaqi is

begin

so<=a xor b;--逻辑运算之间是不可以用加

co<=a and b;

end Behavioral;

--一位全加器

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity yiweiquanjia is

port(a,b,cin:in std_logic;

cout: out std_logic;

sum: out std_logic);

end yiweiquanjia;

architecture Behavioral of yiweiquanjia is

component banjiaqi is

port (a,b : in std_logic;

so,co: out std_logic);

end component;--切记

signal n,m,k :std_logic;

begin

u1:banjiaqi port map

(a=>a,b=>b,so=>m,co=>n);

u2:banjiaqi port map

(a=>cin,b=>m,so=>sum,co=>k);

cout<=k or n;--切记

end Behavioral;

rtl电路:

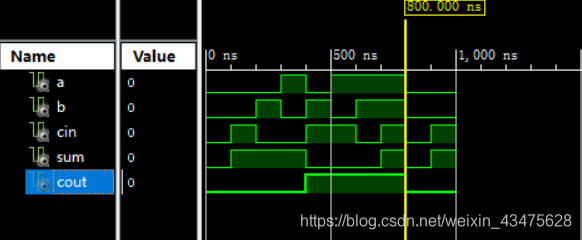

下面开始四位二进制加法器

就是两个4位的输入,一个进位,然后输出4位结果,输出进位

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity siweijiaafaqi is

port(a,b : in std_logic_vector(3 downto 0);

cin:in std_logic;

sum: out std_logic_vector(3 downto 0);

cout: out std_logic);

end siweijiaafaqi;

architecture Behavioral of siweijiaafaqi is

signal aa,bb,sum1: std_logic_vector(4 downto 0);

begin

aa<='0'&a;

bb<='0'&b;

sum1<=aa+bb+cin;

sum<=sum1(3 downto 0);

cout<=sum1(4);

end Behavioral;仿真: