文章目录

一、一位全加器

全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.

二、Quartus-II软件完成一个1位全加器的设计(原理图输入)

一、新建工程

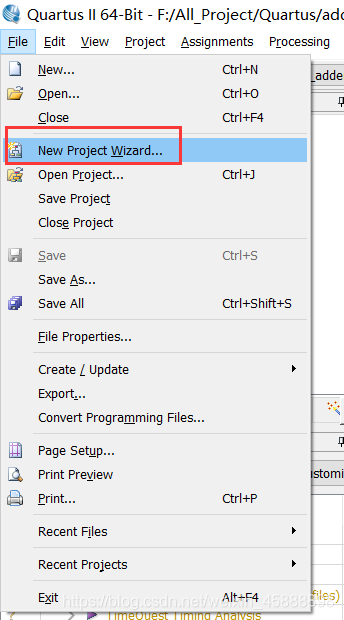

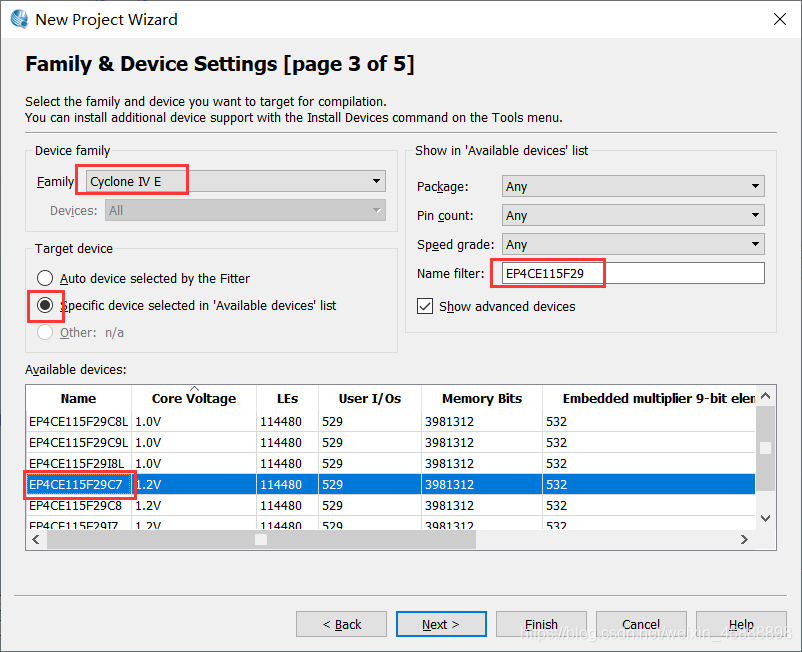

File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

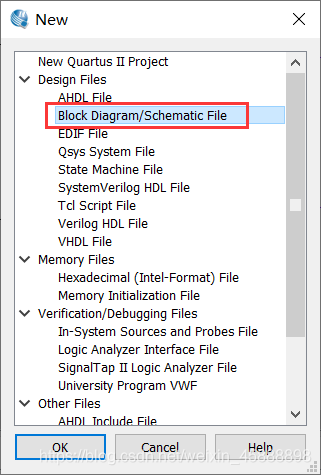

二、新建原理图文件

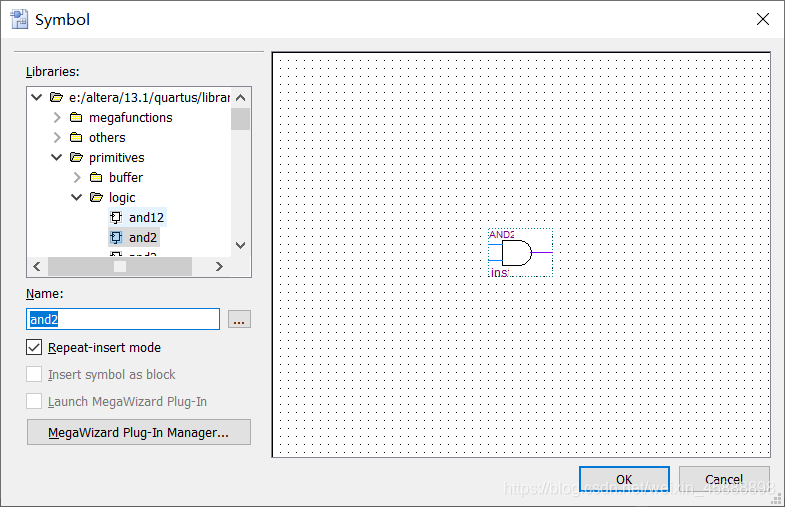

选择元件

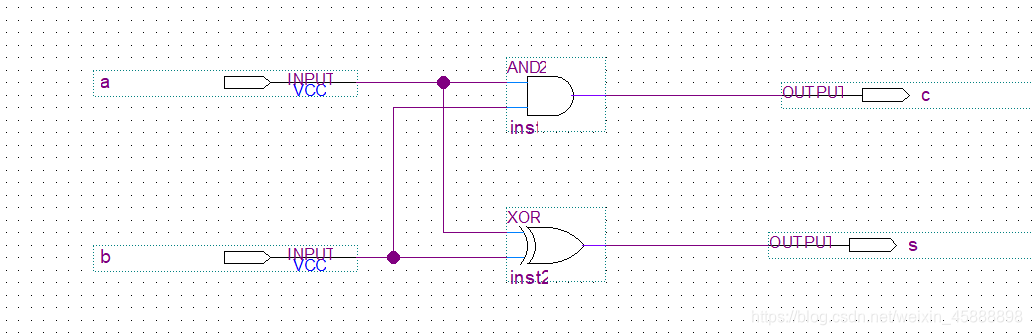

最终半加器的原理图

点击

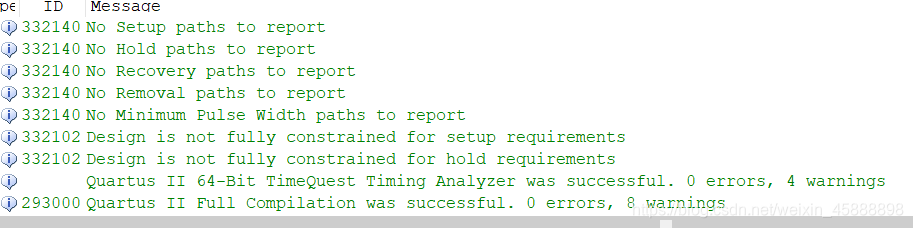

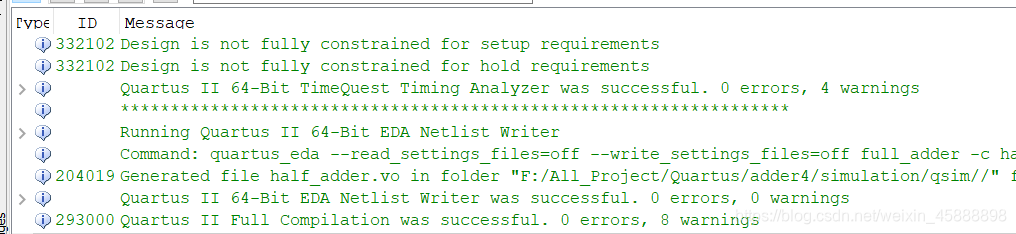

没有红色的错误即可

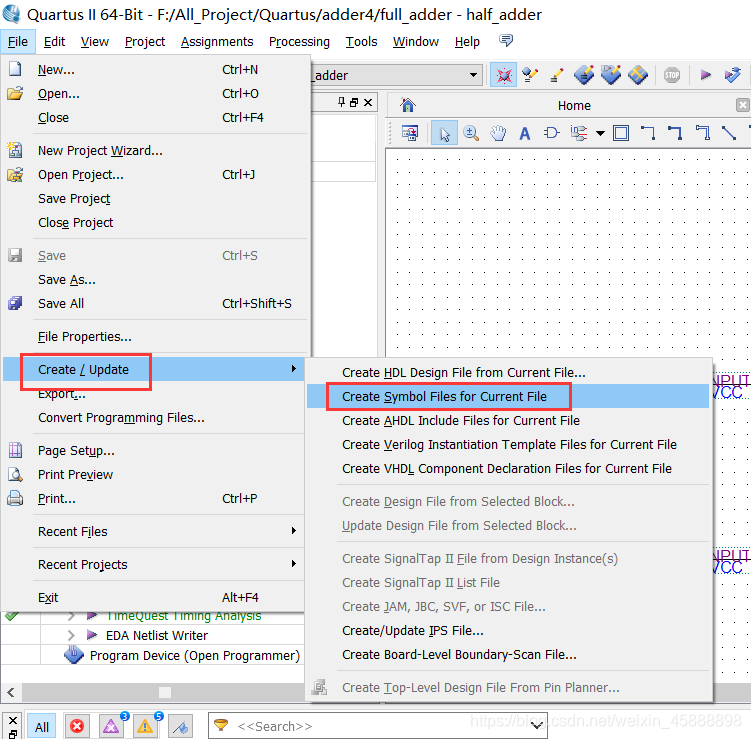

三、将设计项目设置成可调用的元件

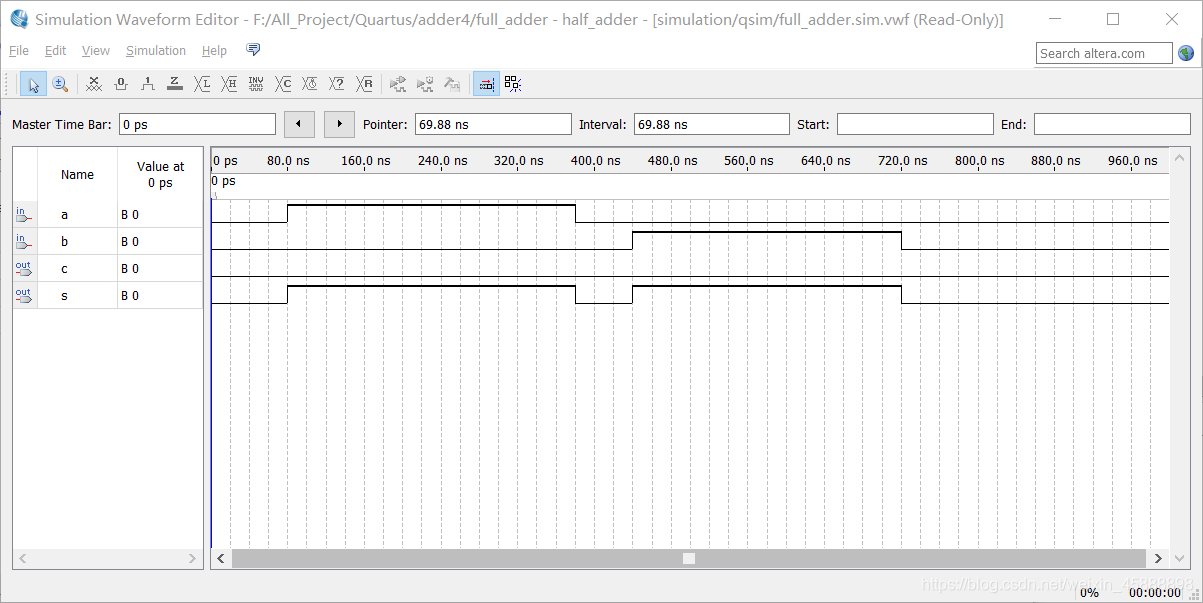

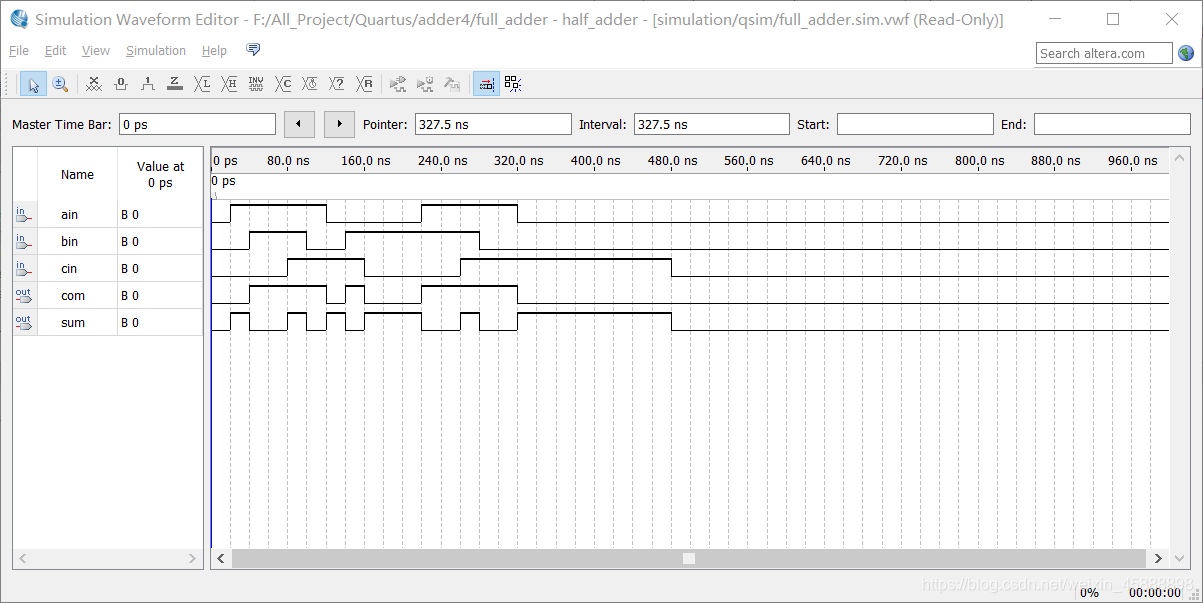

四、半加器仿真

新建波形文件。如上面新建图形文件的方法,从“file”中选择“new”,然后从出现的对话框中选择“university program VWF”。点击“OK”。

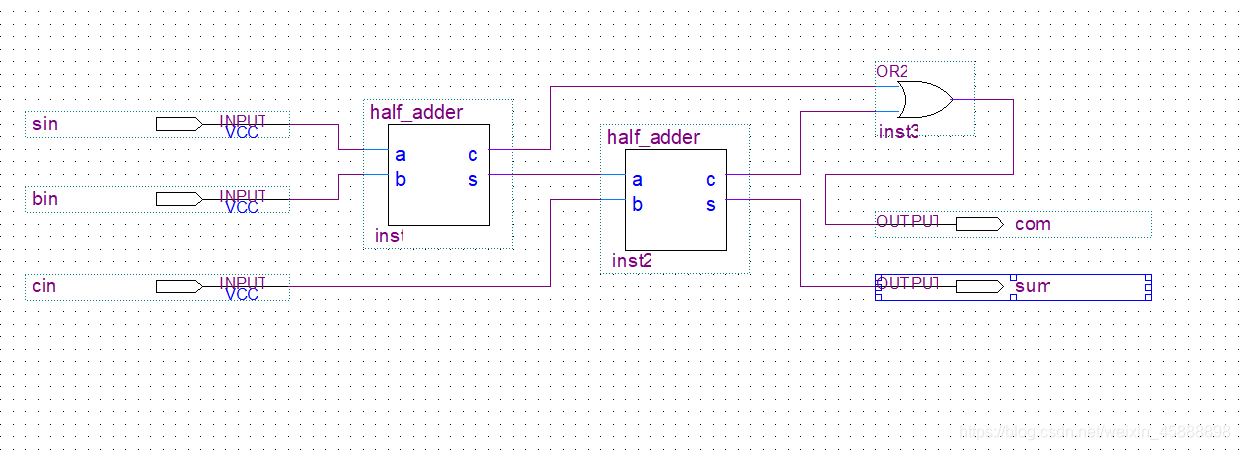

五、设计全加器顶层文件

为了建立全加器的项层文件,必须再打开一个原理图编辑窗,即新建一

个原理图文件。方法同前,即再次选择菜单" File”→“new",原理图文件

编辑输入项"Block Diagram/Schematic File"。

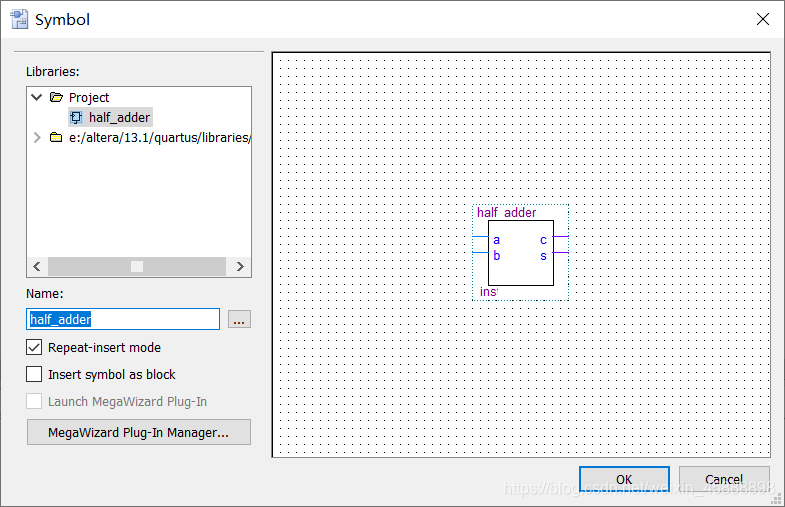

与调入元件的方法一样,即在新打开的原理图编辑窗双击鼠标,在弹出

的“symbol”窗的“name”栏输入底层文件半加器的存储名“half_adder”

调出半加器,

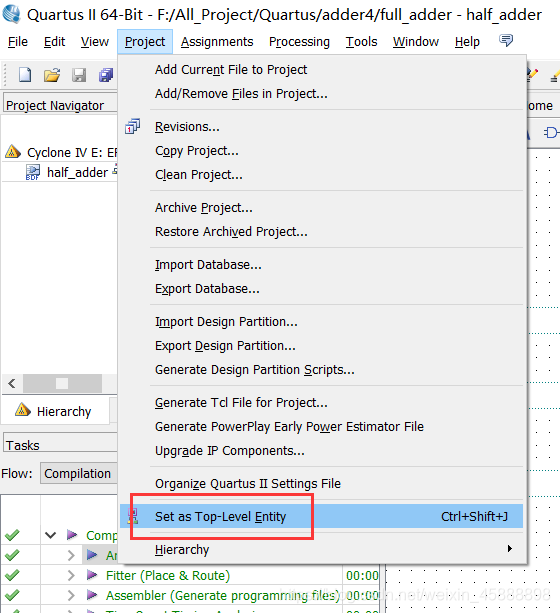

六、将设计项目设置成顶层文件并编译仿真

将顶层文件f_adder.bdf设置为顶层文件的方法:project→set as top_level entity

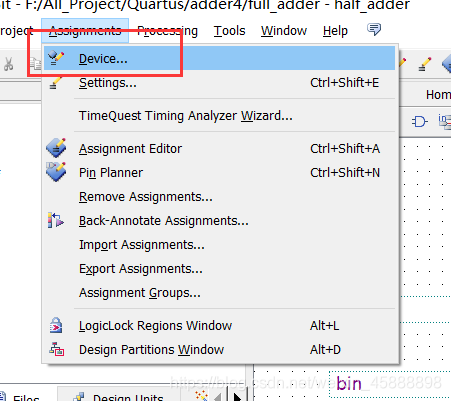

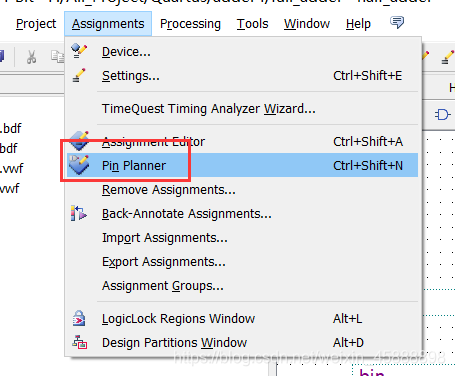

七、引脚绑定及硬件下载测试

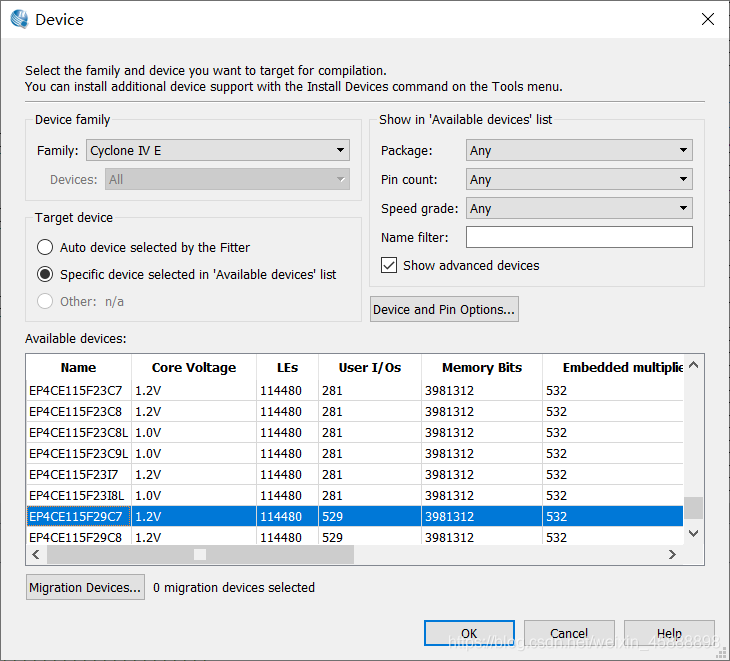

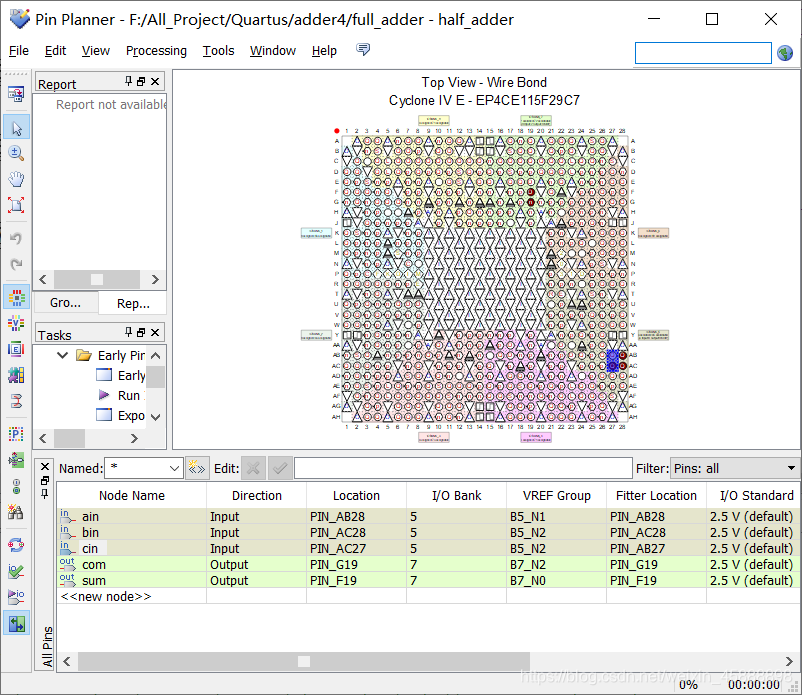

八、引脚绑定

aim管脚为PIN_AB28

bim管脚为PIN_AC28

cim管脚为PIN_AC27

cout管脚为PIN_G19

sum管脚为PIN_F19

九、烧录程序

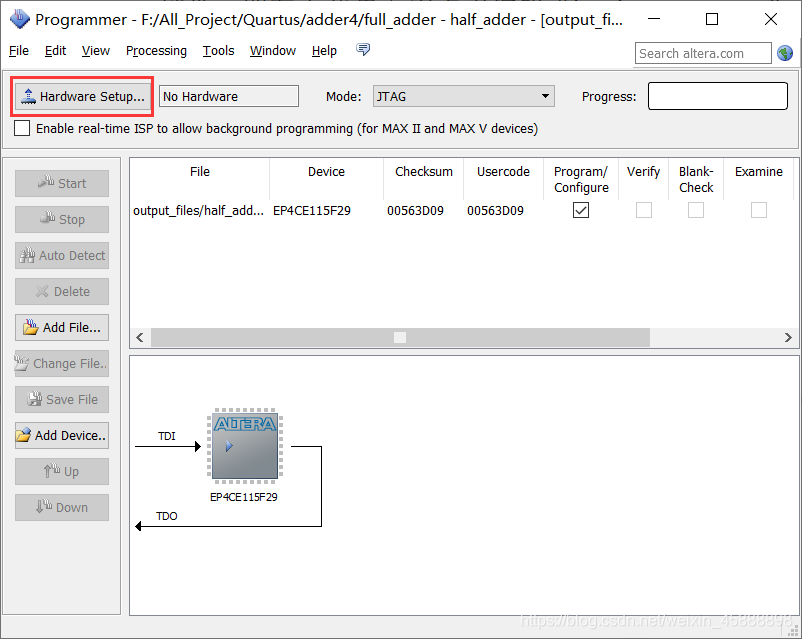

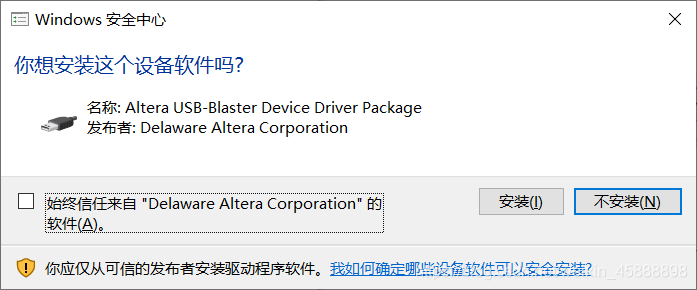

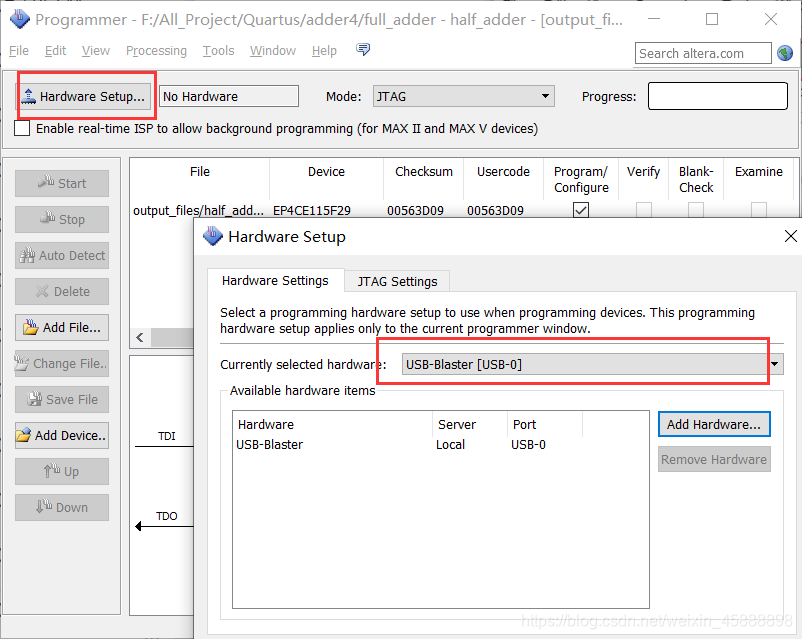

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮 ,则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”

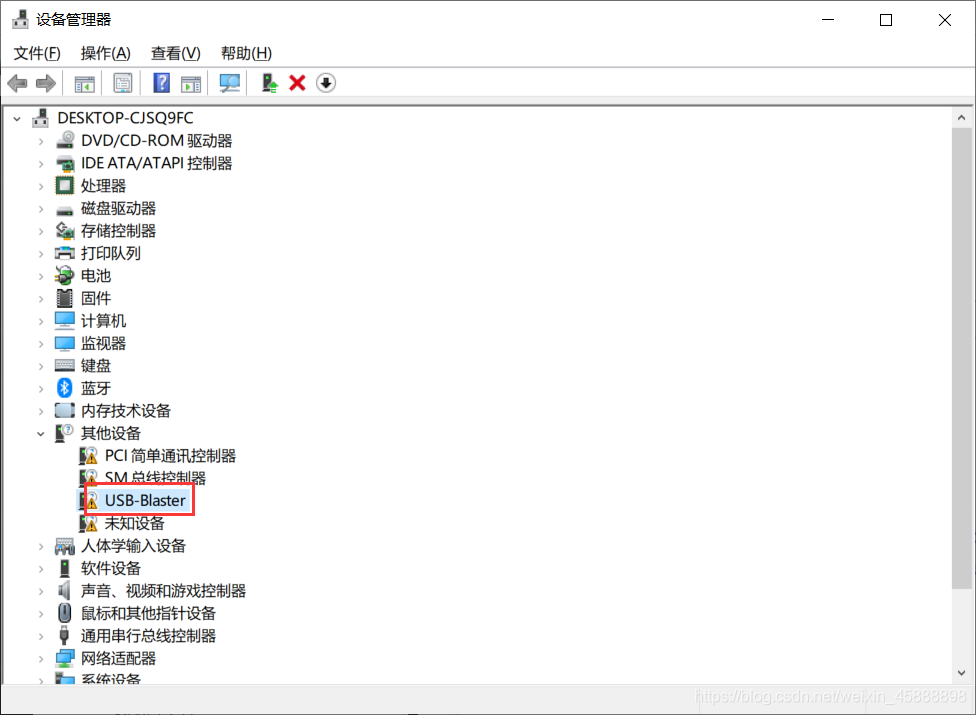

只能从设备管理器里找USB-Blaster,安装相应的驱动

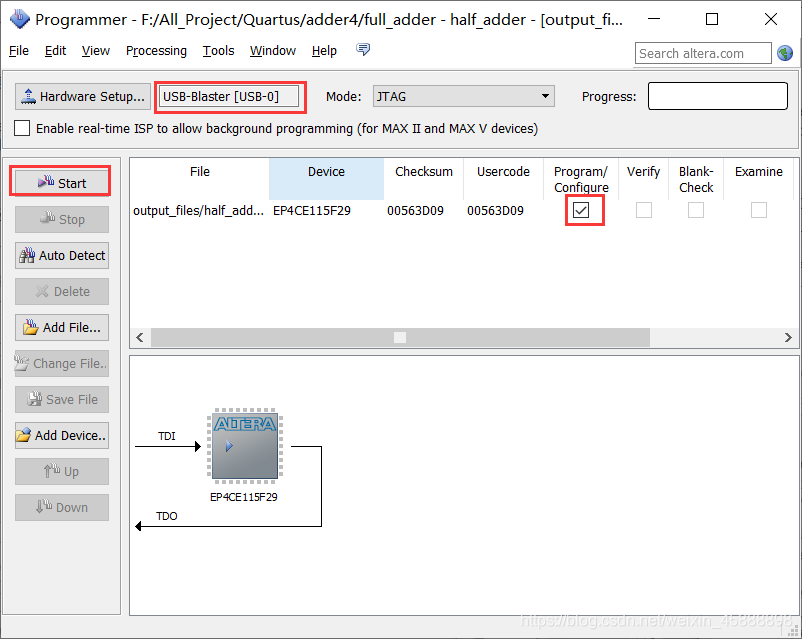

选择USB-Blaster,点击Start

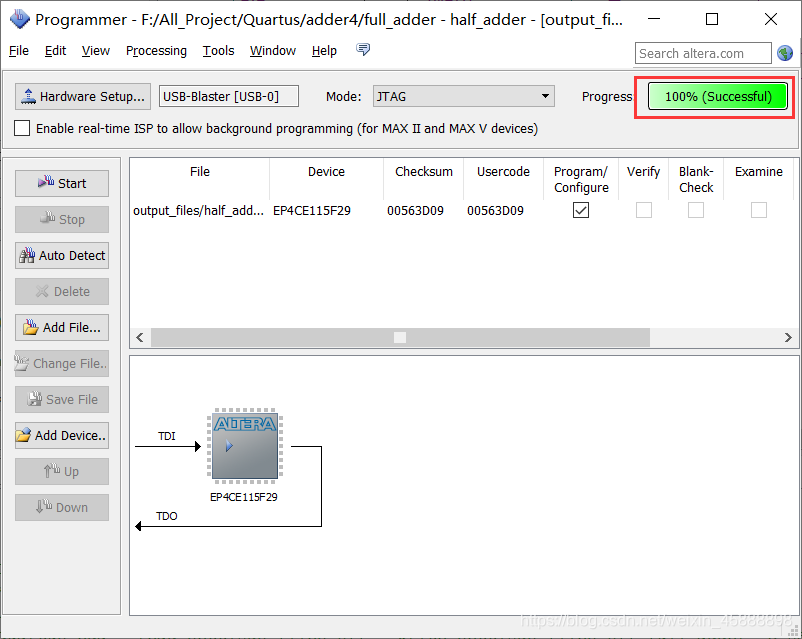

Progress为100%时,烧录成功

十、最终成果