文章目录

一、半加器和1位全加器原理

1. 半加器

所谓半加器,是指对两位二进制数实施加法操作的元器件。

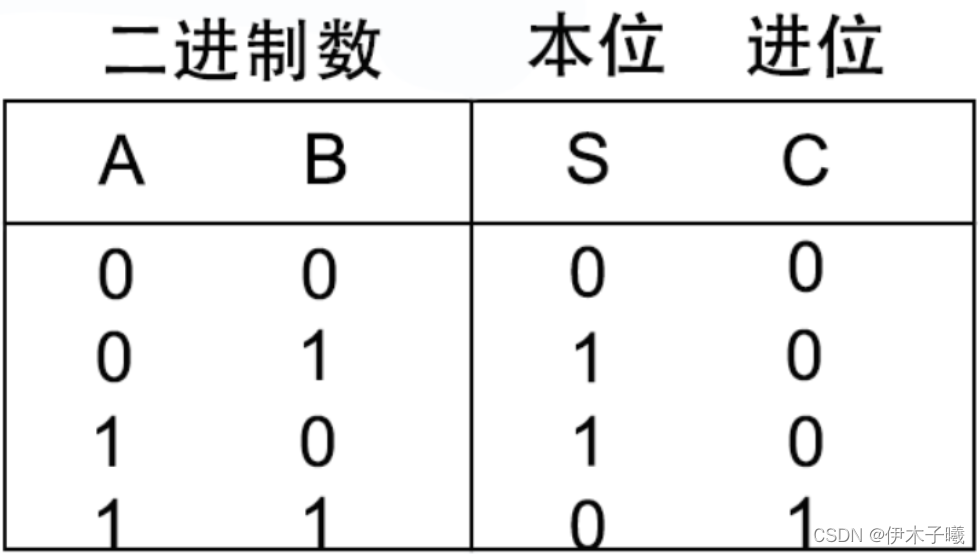

二进制半加器的理解比较简单,就是逢2进1,其真值表为如下图:

2. 1位全加器

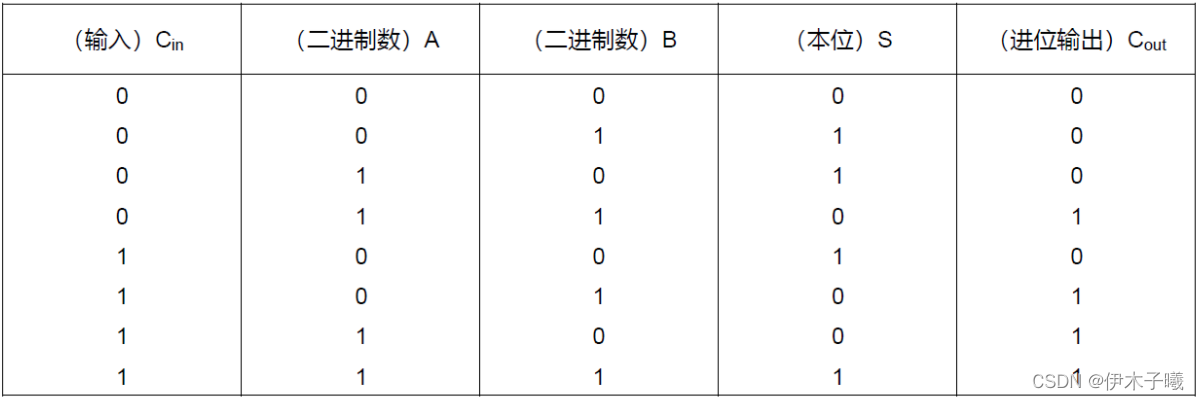

全加器只是加多了一个输入,其实原理和半加器是一样的。全加器真值表如下:

二、实验目的

通过1位全加器的详细设计,掌握原理图输入以及Verilog的两种设计方法。

软件基于quartusII 13.0版本,开发板基于Intel DE2-115。

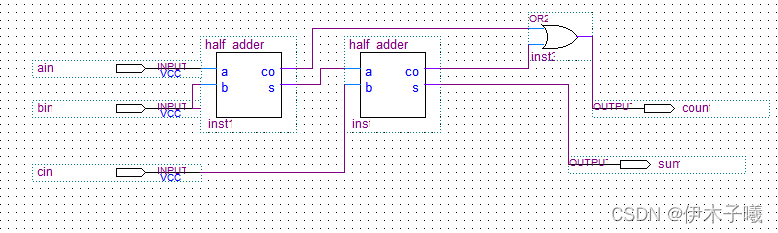

1位全加器可以用两个半加器及一个或门连接而成, 因此需要先完成半加器的设计。

三、设计半加器

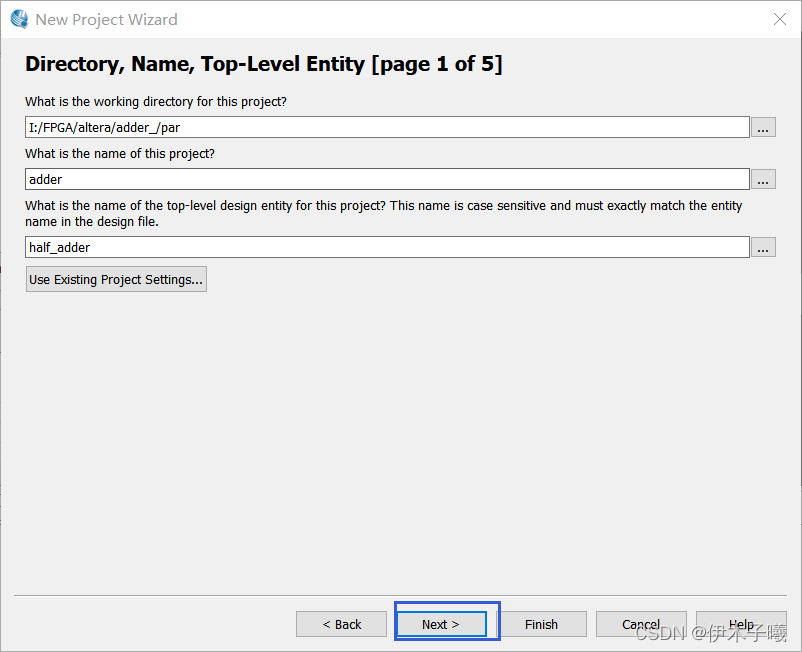

1. 新建项目

file->new Project Wizard选择项目目录,项目名称,顶层文件

-

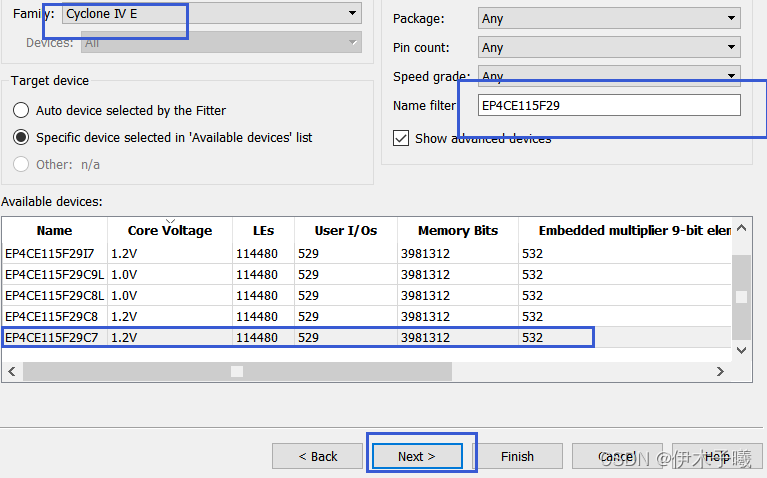

选择对应芯片型号

-

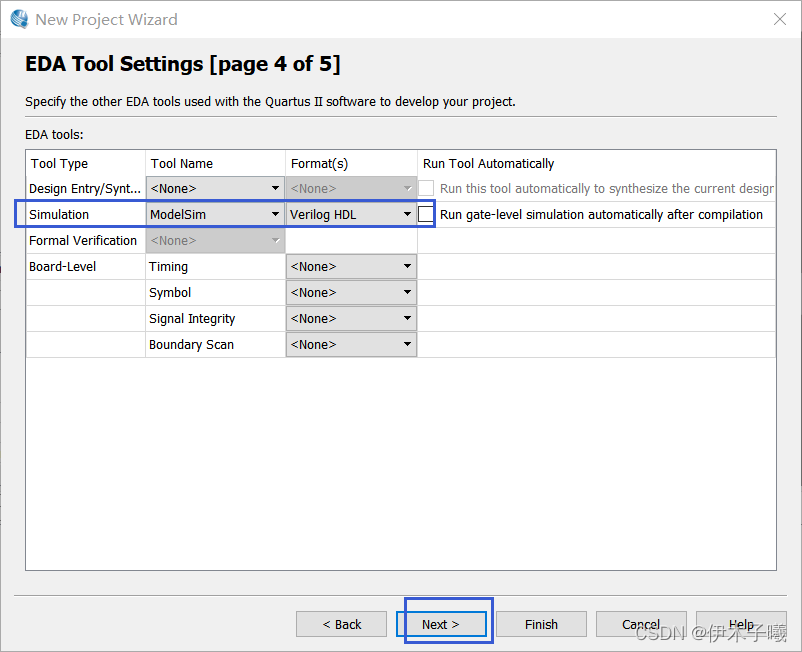

选择仿真

-

next->finsh

2. 创建原理图

-

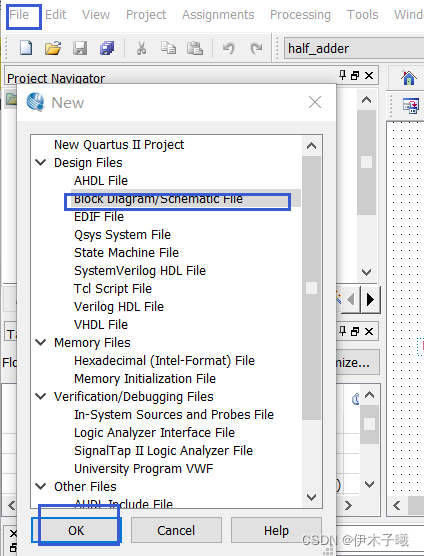

file->new->Block Diagram/Schematic File->OK

-

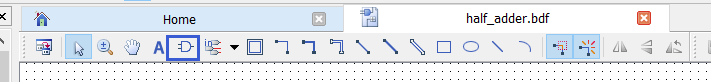

点击按纽

Symbol Tool或直接双击原理图空白处

-

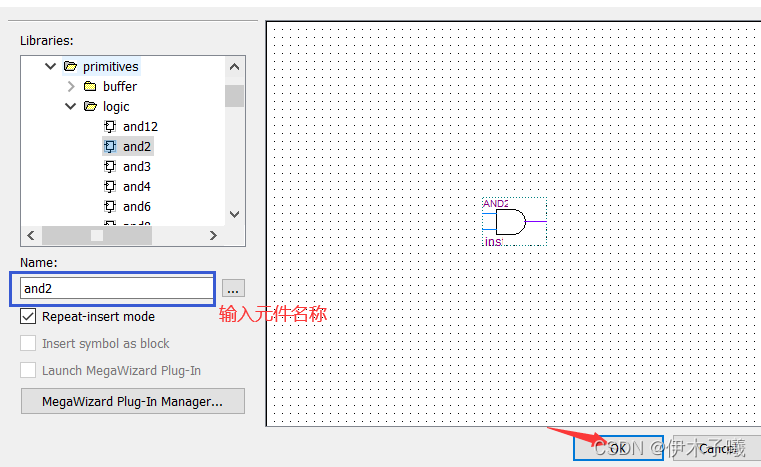

从Symbol窗中选择需要的符号,或者直接在name文本框中键入元件名

-

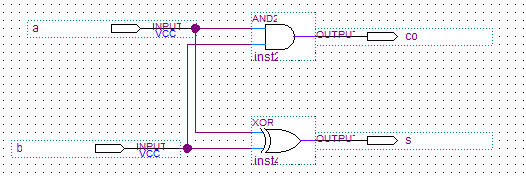

分别调入元件and2,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。输入各引脚名:a、b, co和s。

-

保存,编译

-

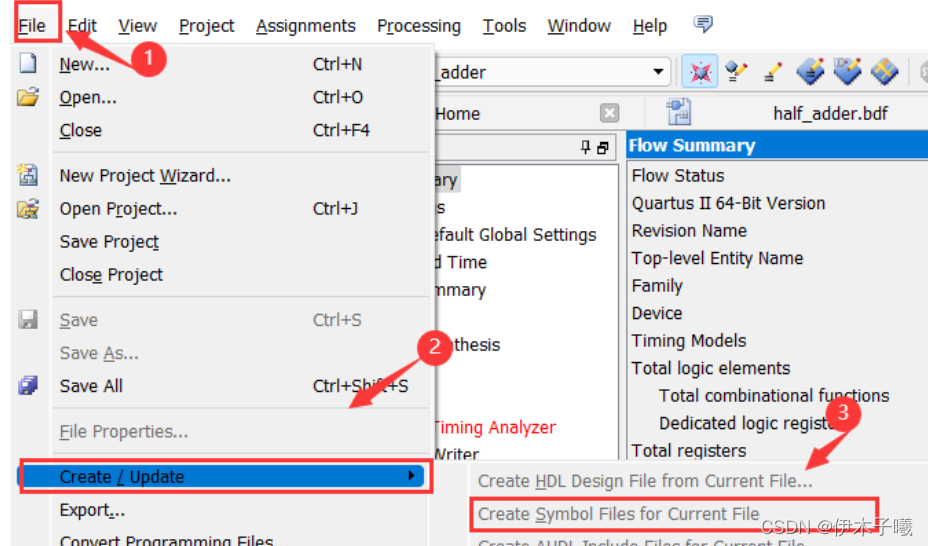

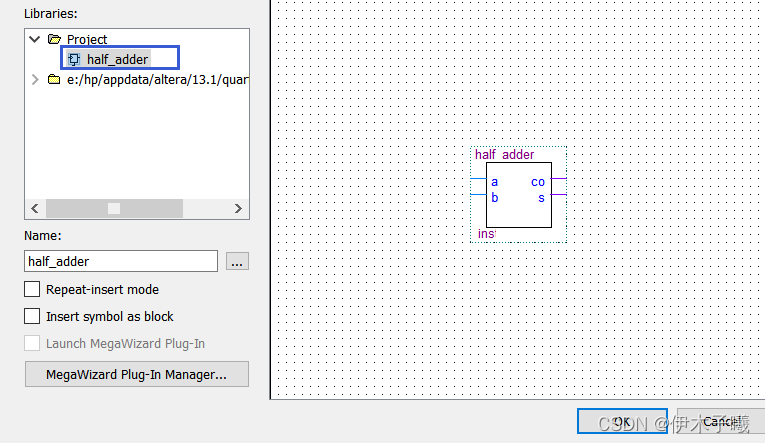

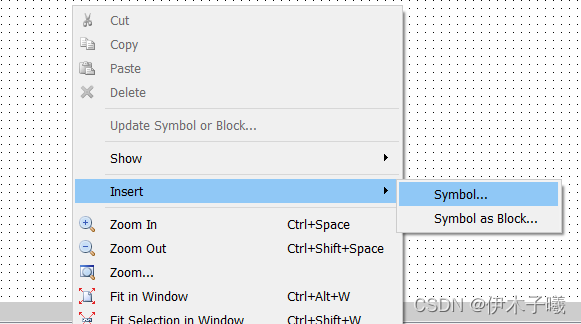

将设计项目设置成可调用的元件

为了构成全加器的项层设计,必预将以上设计的半加器half_adder.bdf设置成可调用的元件

file->Create/Update->Create Symbol Files For Current File

3. 半加器仿真

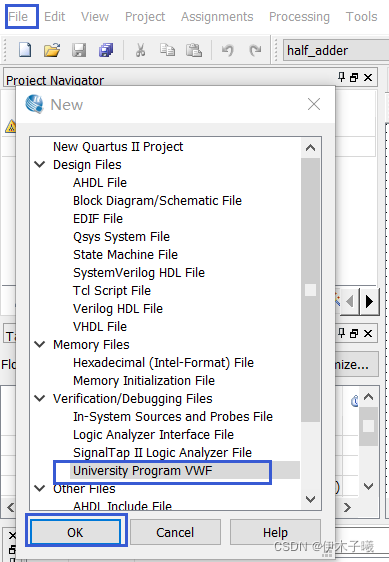

- 选择

file->new->University Program VWF->OK

-

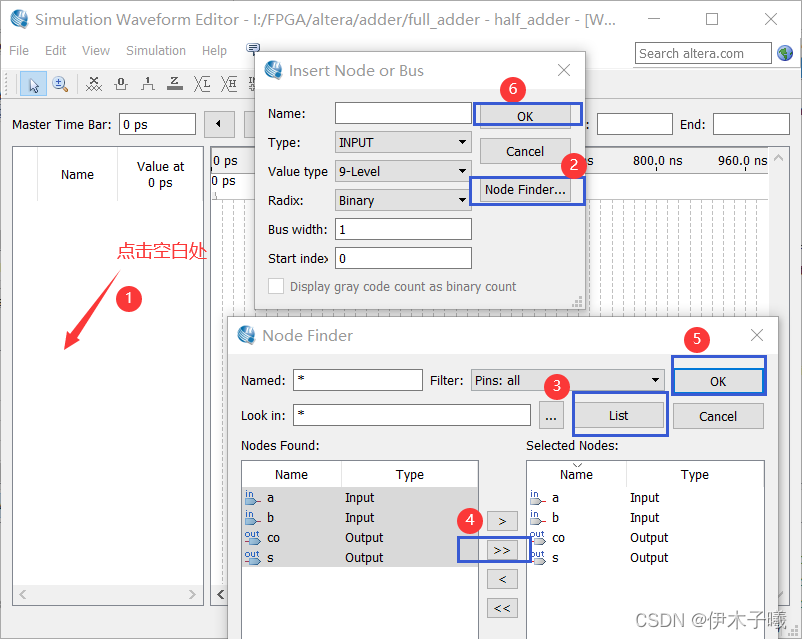

选择引脚序号依次选择

-

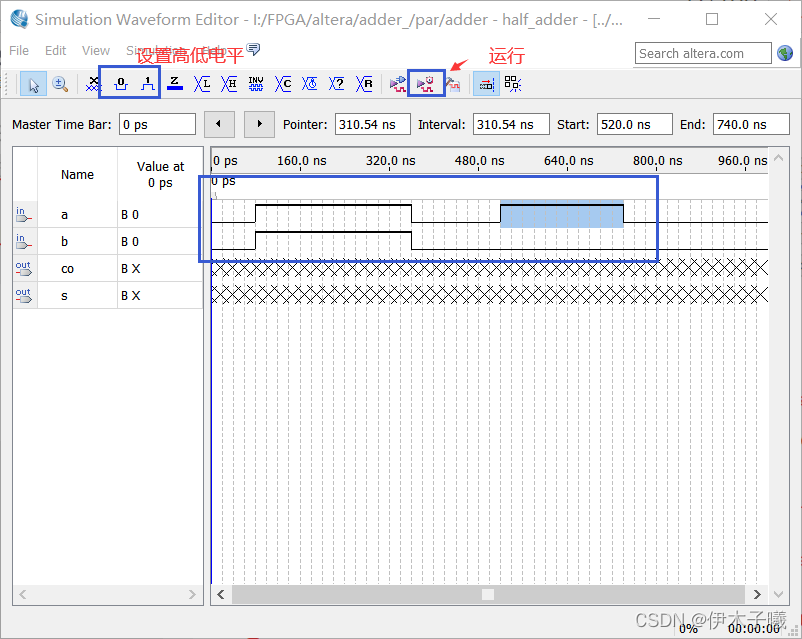

设置高低电平之后运行

-

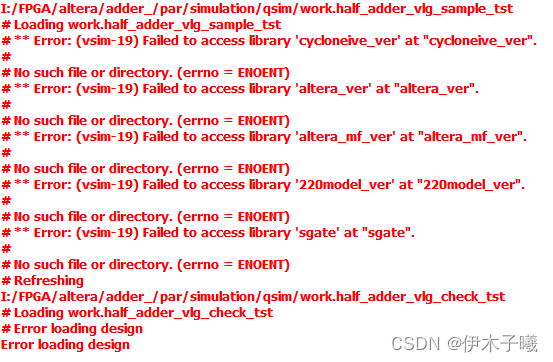

运行会报错

-

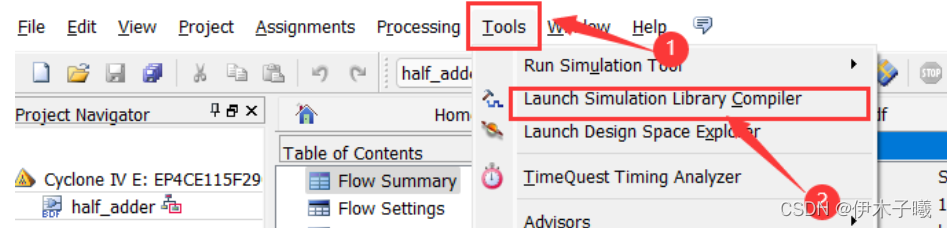

选择

Tools->Launch Simulation Library Compiler

-

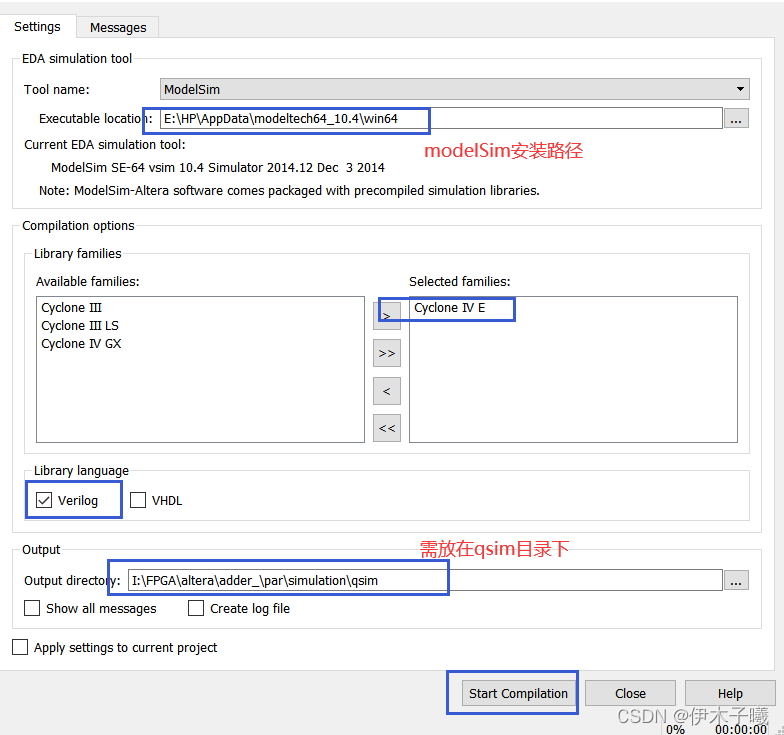

选择modelSim安装路径,选择芯片类型,选择库语言,选择输出文件路径

-

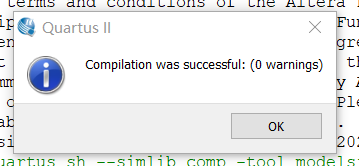

出现0 warnings 说明编译成功

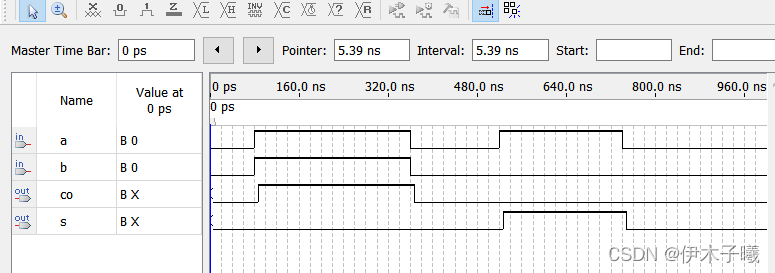

- 再次设置波形,运行,观察波形图

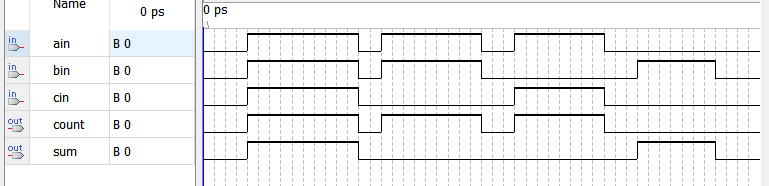

四、设计全加器

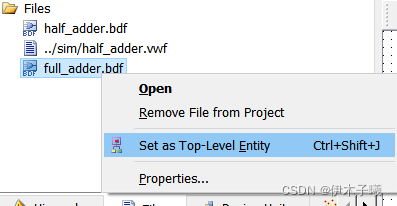

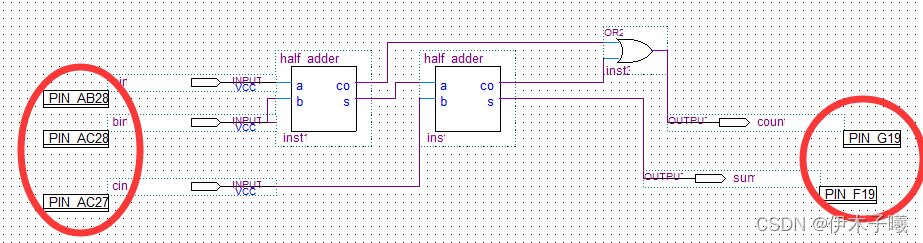

-

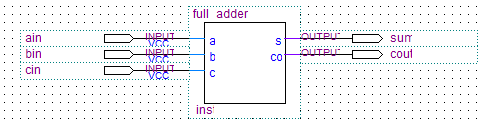

新建原理图 full_adder,并设为顶层文件

-

调用之前设计的半加器元件,以此设计出全加器原理图

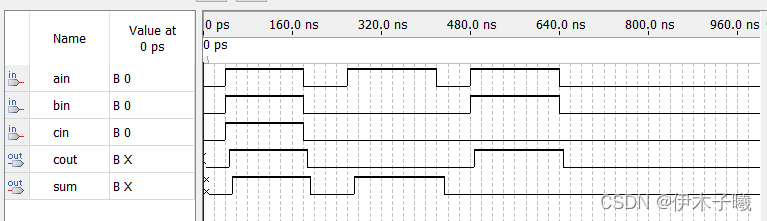

- 仿真测试

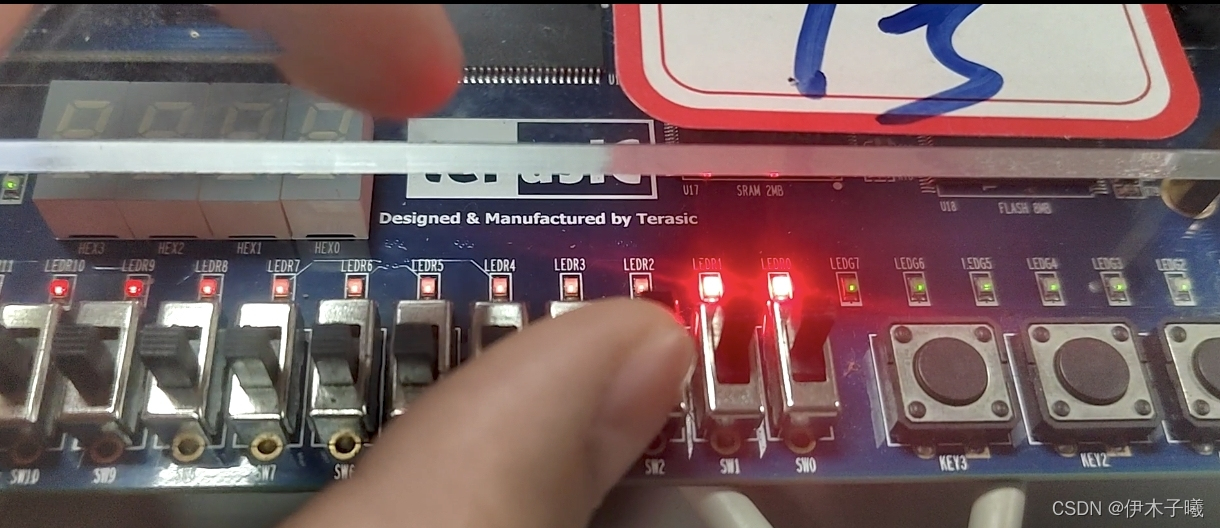

五、硬件下载测试

1. 引脚绑定

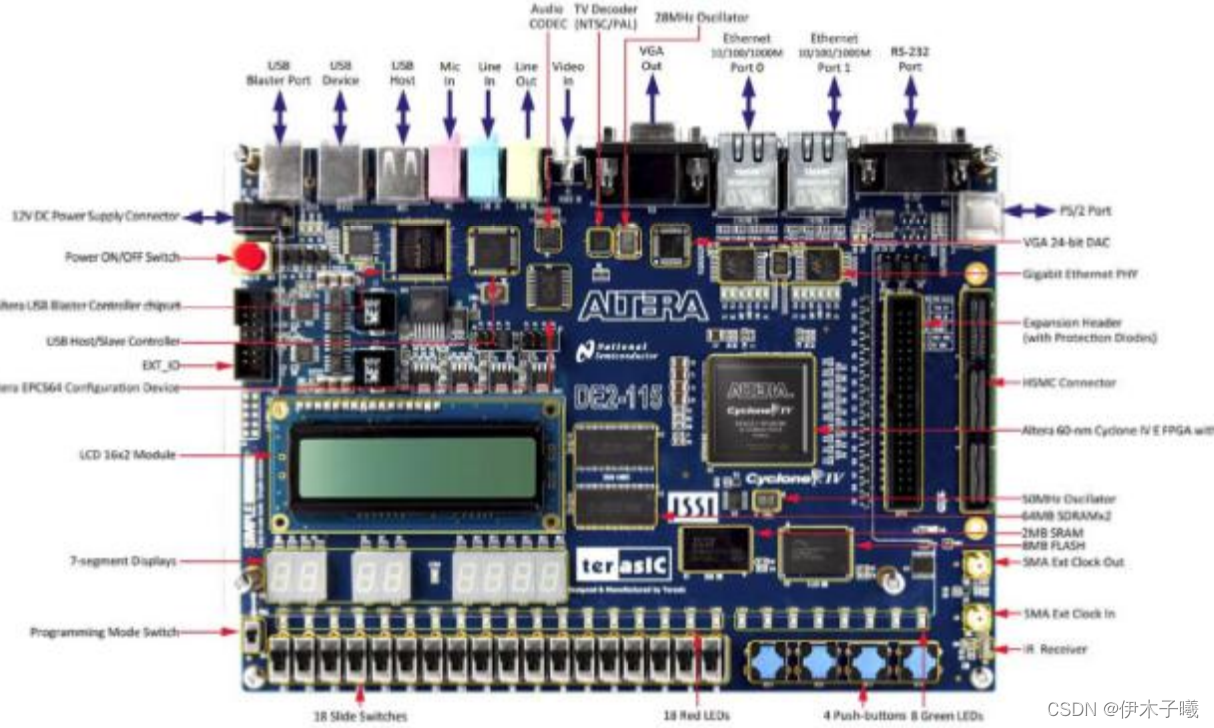

引脚绑定前先要确定具体硬件电路,即目标芯片与外围电路(输入、输出显

示等)的连接情况。实验室使用的ED2-115开发板,除了核心FPGA芯片外,还自

带一些外围输入输出电路。我们就是利用这些输入输出电路来进行硬件测试。

如全加器引脚绑定,可以这样设计:开发板上的18个拨码开关选其中三

个,SW0,SW1,SW2分别接ain、bin、cin(开关向上拨和向下拨分别显示输入

是高还是低电平);LED0,LED1分别接co和sum,灯亮表示输出为“1”,灯灭

表示输出为“0”。

硬件设计好后,还需要查引脚图(引脚图见附录)进行引脚绑定。

从 附 录 “ 表 4-1 拨 动 开 关 引 脚 配 置 ” 中 找 到 输 入 的 三 个 开 关

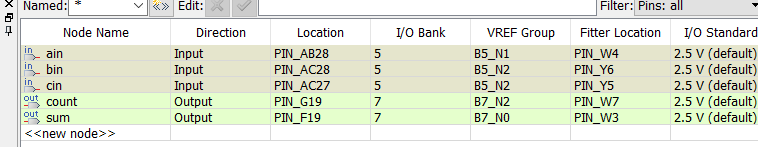

SW0,SW1,SW2,再找到对应的“FPGA引脚号”。如图:

相应的,在附录的表 4-3 中查找到 LED 的引脚配置。

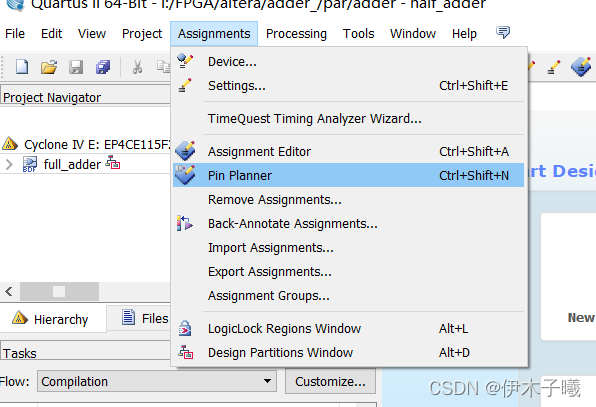

然后在软件中,从菜单中选择“assignments→pin planner”,如图,调出引

脚绑定窗口,然后从下拉窗口中选择相应的输入输出端口,再在“location”栏

填入对应的 FPGA 引脚即可,如图。

选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上。引脚绑定好

并编译过的文件如图

然后就可以下载到硬件上进行测试了。

2. 下载测试

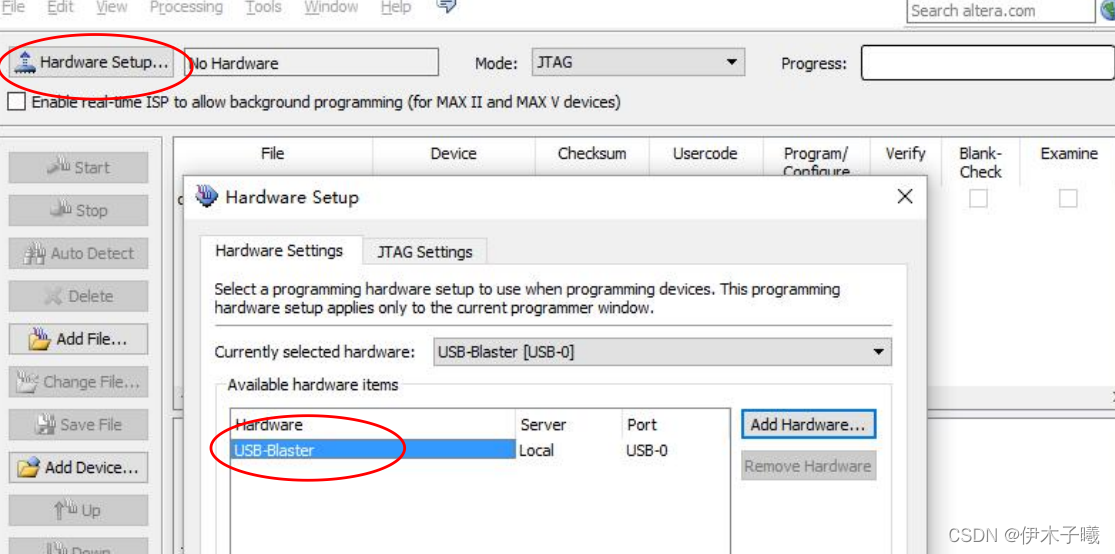

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开

关,以免烧坏板子)。点击软件工具栏上的按钮 ,

则出现下载界面。第一次下载需安装

硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USB

blaster”,再点击“ok”,则硬件被安装上。

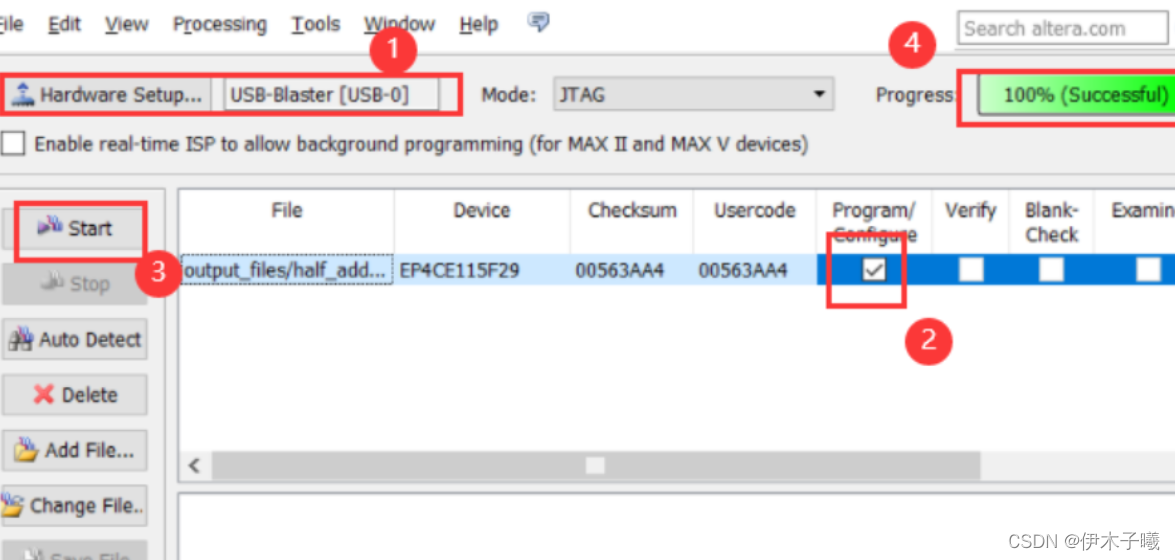

安装好硬件的界面如图。然后在下载的.sof 文件后面的复选框中打勾,再点击”start”,

当进度条达到 100%时,即下载成功,可以进行硬件观测

结果验证

| ain | bin | cin | sum | cout |

|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 |

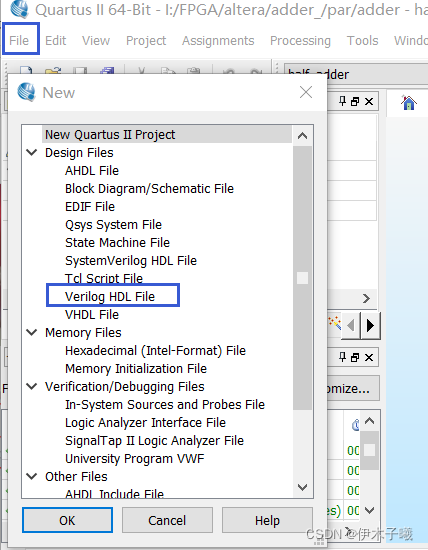

六、Verilog语言设计

-

file->new->Verilog HDL File->OK

-

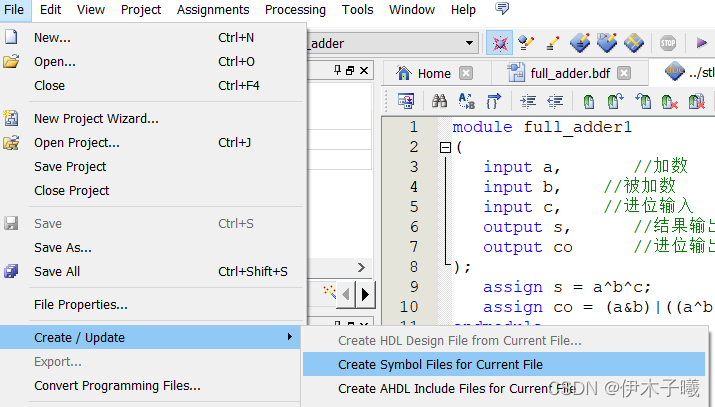

代码:

module full_adder1

(

input a, //加数

input b, //被加数

input c, //进位输入

output s, //结果输出

output co //进位输出

);

assign s = a^b^c;

assign co = (a&b)|((a^b)&c);

endmodule

-

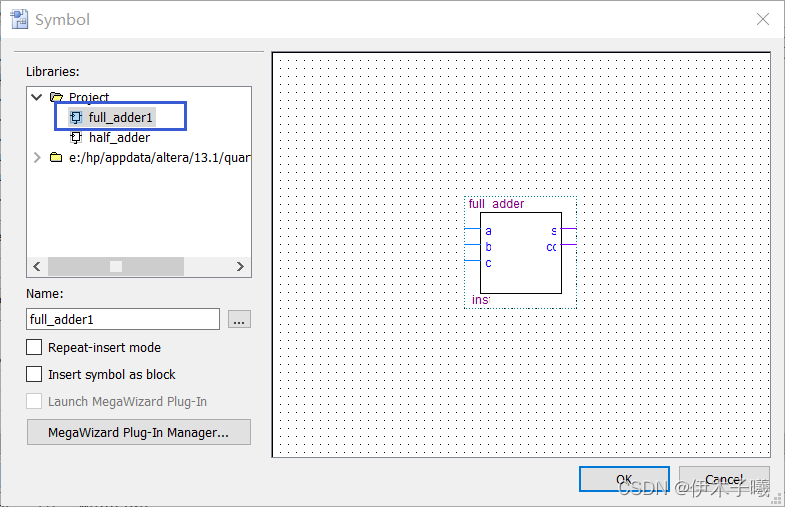

file->Create/Upadte->Create Aysbol Files For Current File生成原理图

-

选择原理图

-

添加输入输出

-

仿真测试

七、总结

通过1位全加器的详细设计,掌握了原理图输入以及Verilog的两种设计方法。