ILA核提供触发和跟踪功能,根据用户设置的触发条件捕获数据,然后在ICON控制下,通过边界扫描口将数据上传到PC上,最后再Analyzer中显示出信号波形。

尽管在行为仿真中我们不需要加入ILA就可以对输入输出、parameter、wire和reg类型的数据进行观测,但是在程序烧进板子的时候我们是无法看到这些信号的变化的,所以通过ILA抓取自己想要观测的信号,就可以观测它们,在烧进比特流文件后观测信号以判断代码是否是正确的。

触发

在使用ILA IP核时,必须选择何时开始捕获数据到IP核,这称为触发事件。

a. 触发器端口。为了监视设计中的不同信号和总线数据,需要使用不同的触发器端口。例如,如果要监视设计中内部系统总线的控制信号、地址信号和数据信号,就必须为每个/组信号指定一个单独的触发器端口。如果将这些不同的信号和总线连接到一个触发器端口,则在查找指定范围内的地址总线时就无法监视CE、WE和OE等控制和使能信号的变化。为使实现资源尽可能少,可以选择不同类型的匹配单元来定制出发所需要的ILA IP核。

b. 匹配逻辑。每个触发端口都有一个或多个匹配单元,这些匹配单元是真正执行比较的逻辑块。有几类匹配单元可以使用。最简单的匹配单元是等于(=)或不等于(!=)比较,这种匹配单元占用的FPGA逻辑资源最少。最复杂的匹配单元可以实现包括等于(=)、不等于(!=)、大于(>)、小于(<)、大于等于(>=)、小于等于(<=)及范围比较在内的所有类型的比较。匹配单元也可以配置为包括信号沿检测,例如检测比较是上升沿、下降沿或变化沿(上升沿和下降沿)。匹配单元的类型如下所述。

(1)基本匹配单元(Basic)和包括信号沿的基本匹配单元(Basic with Edges);基本匹配单元可以执行等于(=)、不等于(!=)比较,包括信号沿的基本匹配单元还可以进行上升沿(R)、下降沿(F)和变化沿(B)的比较。

(2)扩展匹配单元(Extended)和包括信号沿的扩展匹配单元(Extended with Edges):扩展匹配单元可以执行等于(=)、不等于(!=)、大于(>)、小于(<)、大于等于(>=)、小于等于(<=)比较,包括信号沿的基本匹配单元还可以进行上升沿(R)、下降沿(F)和变化沿(B)的比较。

(3)范围匹配单元(Range)和包括信号沿的范围匹配单元:范围匹配单元可以执行扩展匹配单元的所有匹配操作,同时还可以比较值的范围以及超出指定范围的值,包括信号沿的范围匹配单元还可以进行上升沿(R)、下降沿(F)和变化沿(B)的比较。

c.匹配单元计数器。在指定触发器端口上的匹配单元组可以为每个输出配置一个匹配计数器,用于检测触发事件出现的次数,可以是序列的,也可以不是序列的。计数器的大小在生成IP核时指定,技术的事件和/或是否进行序列化计数过程在运行时决定。

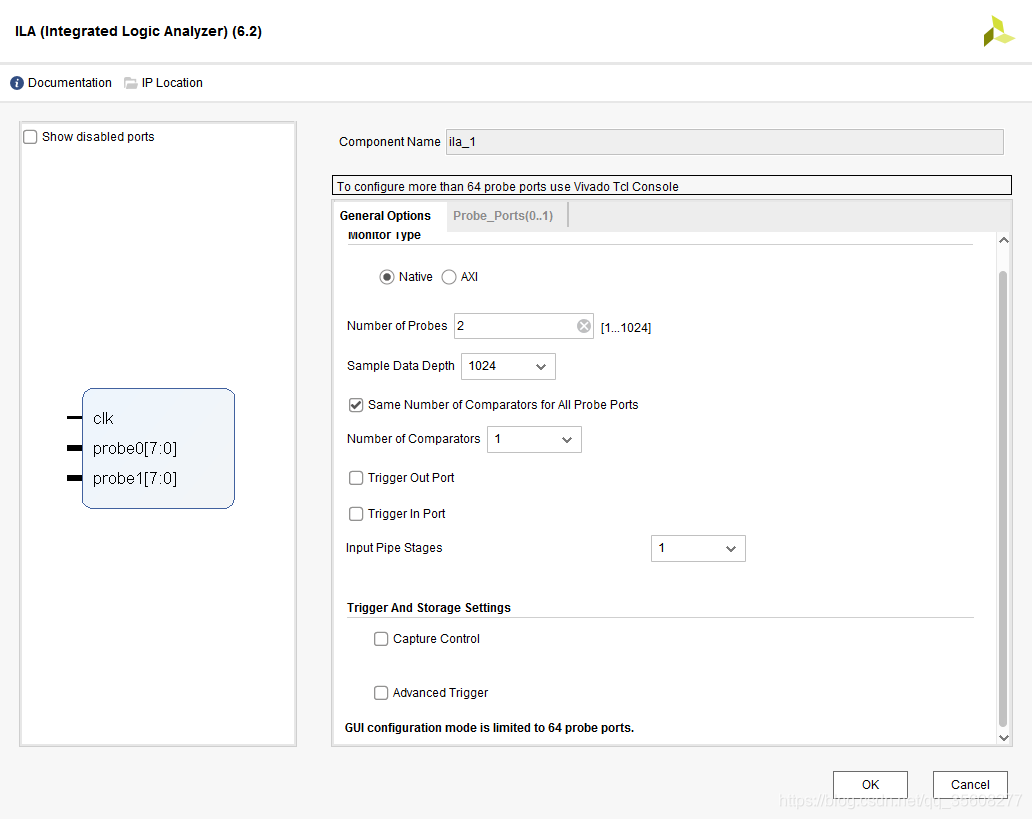

Number of probes 2 为设置需要观察信号的组为2组,

Sample Data Depth 1024 设置采样的深度,这是需要消耗FPGA的BRAM的BRAM越大可以设置的采样深度就越大,当然编译速度会降低。

Probe Port 探针类似示波器的表笔,只是这里是在FPGA内部

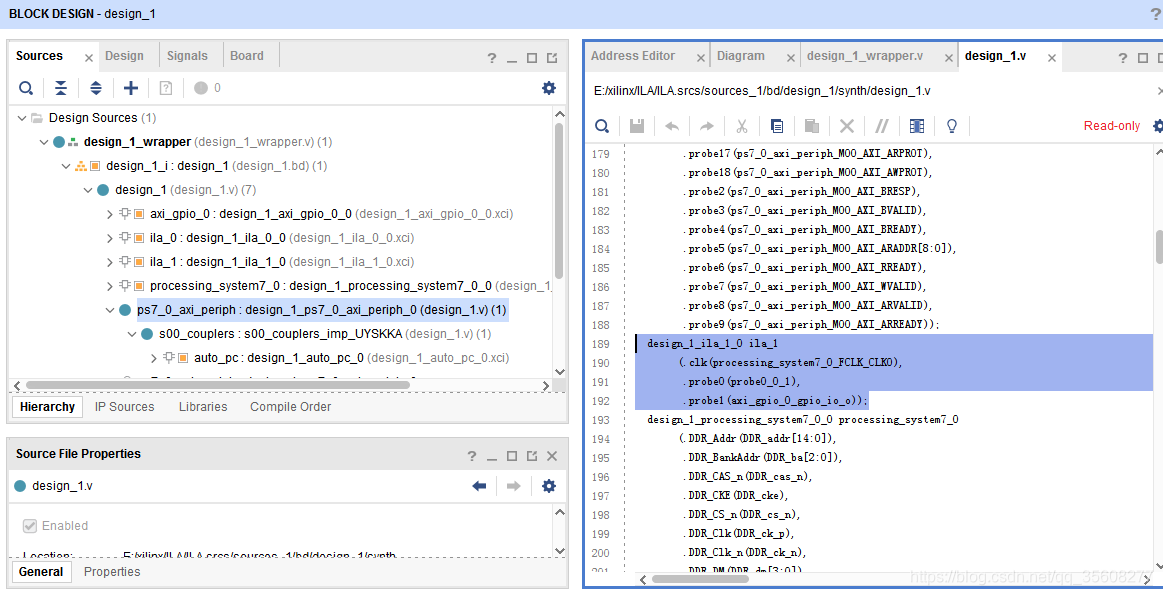

生成

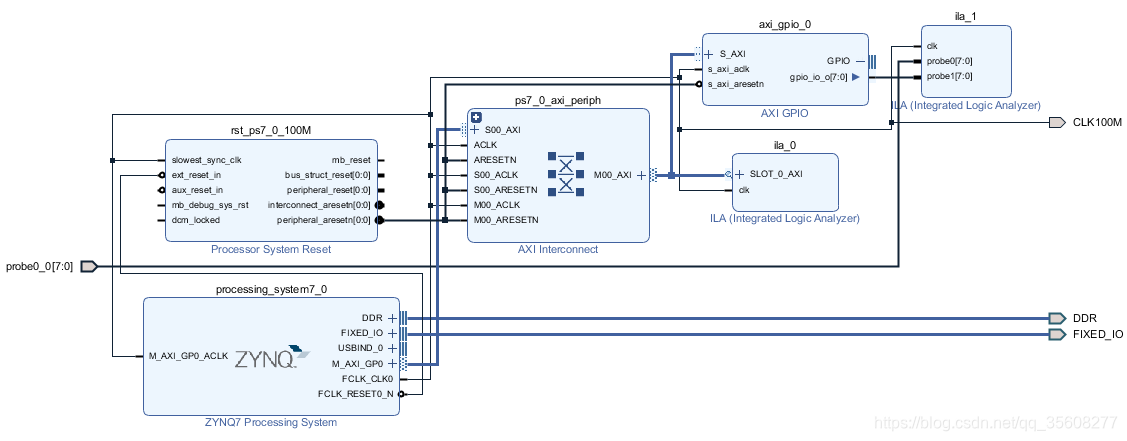

观察fpga cnt 和在sdk axigpio cnt 的速度差别,和axi 逻辑

启动sdk

open target