版权声明:本博客内容来自于个人学习过程中的总结,参考了互联网、数据手册、帮助文档、书本以及论文等上的内容,仅供学习交流使用,如有侵权,请联系,我会重写!转载请注明地址! https://blog.csdn.net/Reborn_Lee/article/details/88920770

RTL设计

在RTL设计中,将想要抓取的信号前加上: (*KEEP = "TRUE"*) reg led_reg02;

例如,本例中需要抓取的信号是led_reg02;

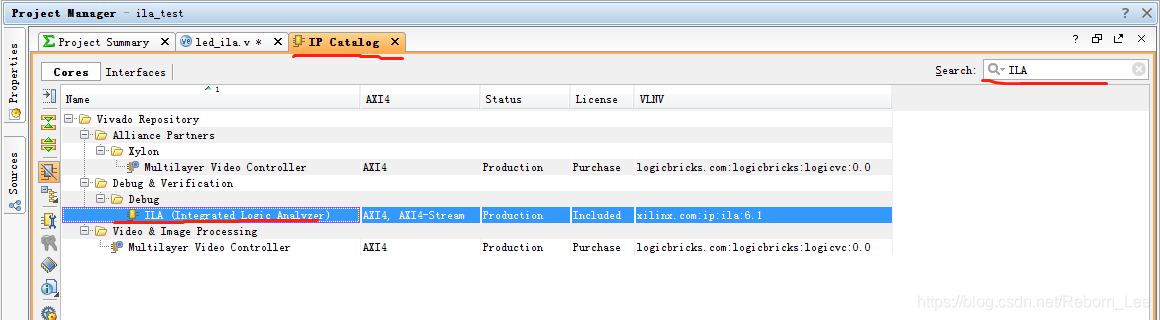

ILA核的生成及例化

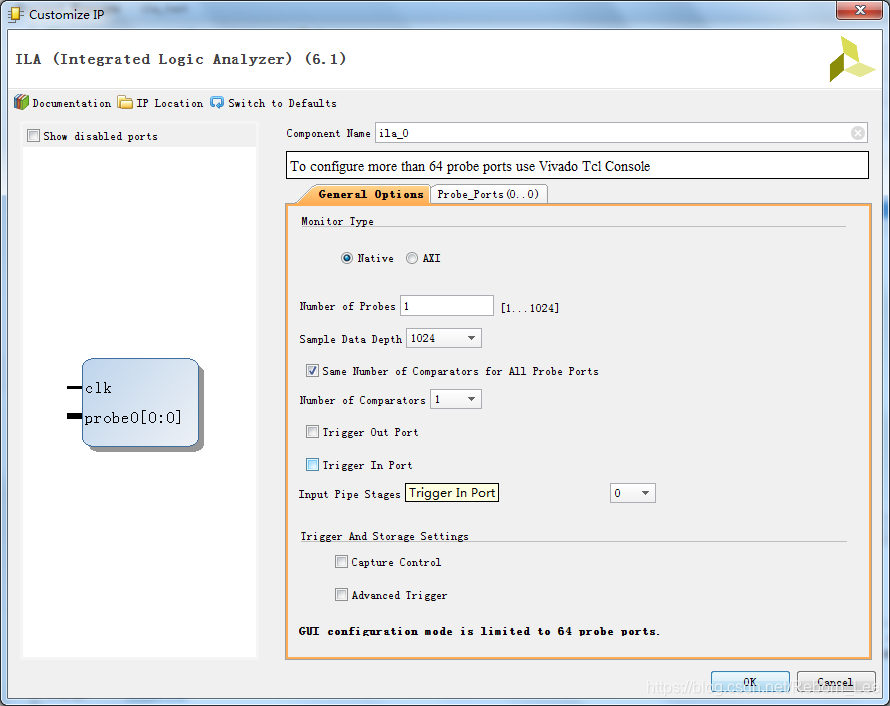

之后生成一个ILA核,如下:

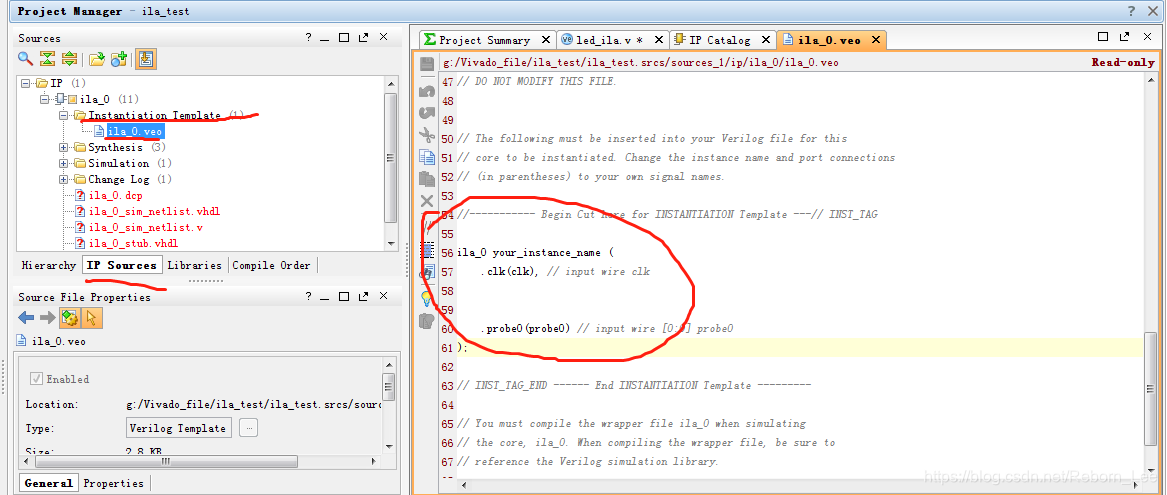

点击OK,生成ILA核完毕。之后在程序中例化ILA核:

给出例化程序部分:

ila_0 ila_sysclk (

.clk(sys_clk), // input wire clk

.probe0(led_reg02) // input wire [0:0] probe0

);我需要抓取的是led_reg02;

sys_clk是系统时钟。

下面进行综合,实现以及生成比特流文件。

下载比特流到FPGA

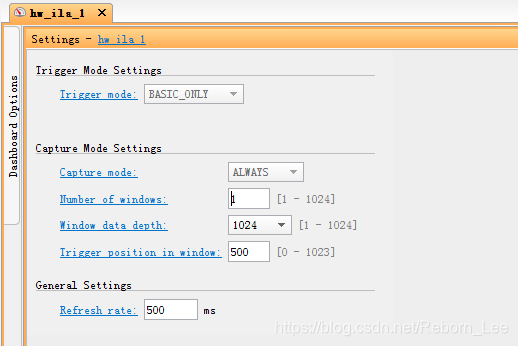

比特流生成之后,对FPGA上电,并打开Hardware Manager:

可以修改设置:

点击触发按钮:

完毕。

本文介绍了一种方便的使用ILA核的方法,当然还有其他的方式,自己去尝试。

参考: