整体流程

- 将vivado里的工程加入逻辑分析仪到需要debug的端口,综合实现完成后得到比特流,送入SD卡。如果要查看AXI4-Full总线,这里需要注意system ILA里面有一个number of outstanding Read/Write Transactions,这个值如果太小,实际的ILA波形会显示Overflow

送入SD卡的流程主要分两种情况:Petalinux流程和PYNQ流程。前者需要把比特流放置在boot分区(SD卡上的第一个分区),并修改BootLoader,后者只需要复制到板子的home目录即可。

- 板子的启动设置为SD卡启动。看看vivado能否检测到FPGA,如果不能,先换至JTAG启动,等能检测到了再换成SD卡启动。

注意:SD卡启动过程中不要把JTAG线连至vivado,会启动失败

- 确定启动成功后还不能直接用vivado调试JTAG,有时候vivado烧写比特流的时候会导致CPU卡死,表现为串口和网口均无反映。这是因为Linux的cpuidle低功耗子模块发现Vivado的行为后将CPU关闭所致。解决方法需要修改UBoot的启动参数,在末尾添加cpuidle.off=1。为了实现这一点,有若干方法:

- 如果拥有设备树源文件,直接在bootargs末尾加即可,例如:

/ {

chosen {

bootargs = " console=ttyPS0,115200n8 earlycon clk_ignore_unuse cpuidle.off=1"; //举个例子,前面的选项替换为实际的args

};

};

- 或者在uboot命令行使用

setenv bootargs ....... cpuidle.off=1,省略部分为原来的bootargs变量。只执行setenv是临时修改,想永久保存还需要再执行saveenv,设置完执行boot或bootm即可正常启动。bootargs变量查看方式可以用 dmesg | grep command或者cat /proc/cmdline

- 接下来可以debug硬件了,在vivado的调试界面启动trigger,在串口或者网口启动需要debug的程序,vivado会在指定位置触发。

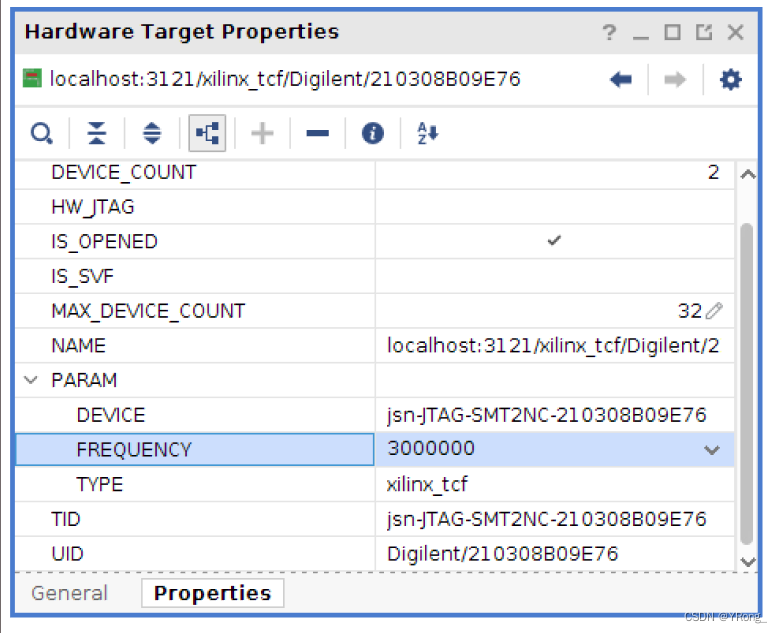

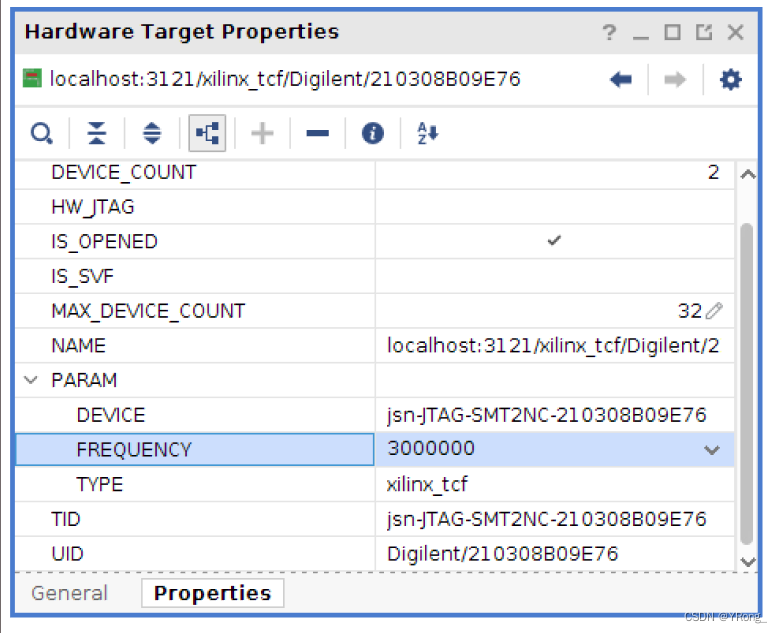

注意ILA的时钟频率必须比JTAG的时钟频率高2.5倍,否则会报错。调整JTAG时钟频率的位置在Hardware Manager里,选中器件-properties-PARAM-FREQUENCY,如下图所示。