打开Vivado, 并新建一个工程,取名dividerIla ,类型(type),选择RTL Projecct,Default Part 根据你的硬件平台选择。这个一定要选择正确,因为需要下载并运行的。我的平台是AC7010, 选择的是xc7z010clg400-1。

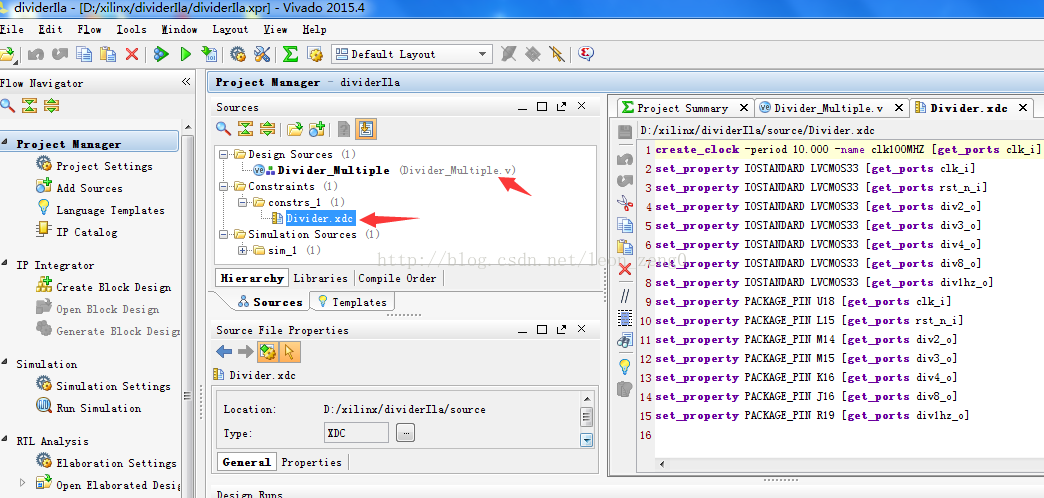

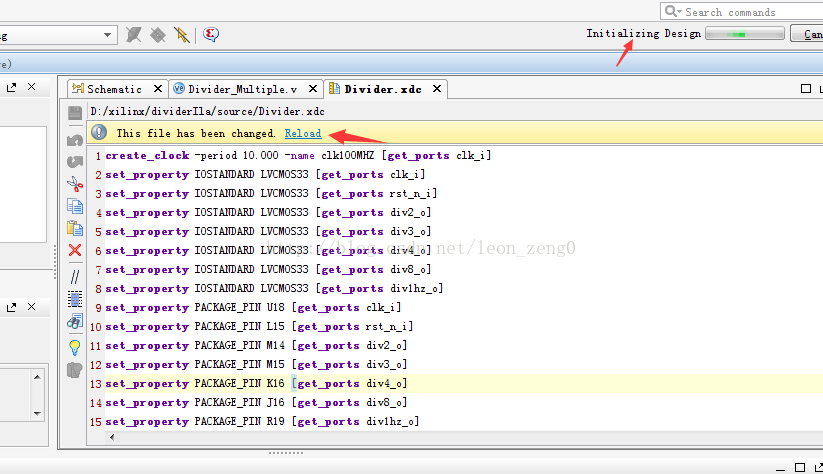

接下来是添加下载的源程序文件:Divider_Multiple.v 到Design Sources 下, Divider.xdc 到 Constarnts下。最后的效果如下图,其操作过程不详述,如果操作不来,请去查看我写的 Vivado 下的仿真入门一文,那有详细图示。

这里特别注意,如果你的硬件平台不一样,你需要修改Divider.xdc文件。这里分配硬件的管脚,需要与你的硬件一致,特别是clk_i, div1hz_o。 clk_i 是时钟输入脚,我的硬件是U18, div1hz_o 是led 闪灯控制,我的是R19, rst_n_i 是复位脚,我的是L15(其实没有使用)。

在这一步的时候,如果你综合(Synthesis), 执行(Implementation),产生比特流(Genrate Bitstream), 并下载 运行,应该看到你的一个LED 在一闪一闪的。这就是说,如果硬件平台不一致,你就要保证程序是正确无误的,否则,你要修改好。

如果你不想下载,这里提供copy 程序,就是这2个程序的代码。

Divider_Multiple.v 代码:

`timescale 1ns / 1ps

module Divider_Multiple(

input clk_i,

input rst_n_i,

output div2_o,

output div3_o,

output div4_o,

output div8_o,

output div1hz_o

);

reg div2_o_r=1'b0;

always@(posedge clk_i)

div2_o_r=~div2_o_r;

reg [1:0]div_cnt1=2'b00;

always@(posedge clk_i)

div_cnt1<=div_cnt1+2'b1;

reg div4_o_r=1'b0;

reg div8_o_r=1'b0;

always@(posedge clk_i)

begin

if(div_cnt1==2'b00 || div_cnt1==2'b10)

div4_o_r=~div4_o_r;

else

div4_o_r=div4_o_r;

end

always @ (posedge clk_i)

begin

if((~div_cnt1[0]) && (~div_cnt1[1]))

div8_o_r=~div8_o_r;

else

div8_o_r=div8_o_r;

end

reg[1:0] pos_cnt=2'b00;

reg[1:0] neg_cnt=2'b00;

always@(posedge div2_o_r)

begin

if(pos_cnt==2'd2)

pos_cnt<=2'b00;

else

pos_cnt<=pos_cnt+2'b01;

end

always@(negedge div2_o_r)

begin

if(neg_cnt==2'd2)

neg_cnt<=2'b00;

else

neg_cnt<=neg_cnt+2'b01;

end

reg div3_o_r0;

reg div3_o_r1;

always@(posedge div2_o_r)

if(pos_cnt<2'd1)

div3_o_r0<=1'b1;

else

div3_o_r0<=1'b0;

always@(posedge div2_o_r)

if(neg_cnt<2'd1)

div3_o_r1<=1'b1;

else

div3_o_r1<=1'b0;

reg div1hz_o_r=0;

reg [25:0] div1hz_cnt=0;

always @(posedge clk_i)

if(div1hz_cnt<26'd50_000_000)

div1hz_cnt<=div1hz_cnt+1'b1;

else

div1hz_cnt<=0;

always@(posedge clk_i)

if(div1hz_cnt==26'd49_999_999)

div1hz_o_r<=~div1hz_o_r;

else

div1hz_o_r<=div1hz_o_r;

assign div2_o=div2_o_r;

assign div3_o=div3_o_r1;

assign div4_o=div4_o_r;

assign div8_o=div8_o_r;

assign div1hz_o=div1hz_o_r;

endmodule

Divider.XDC代码:

create_clock -period 10.000 -name clk100MHZ [get_ports clk_i]

set_property IOSTANDARD LVCMOS33 [get_ports clk_i]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n_i]

set_property IOSTANDARD LVCMOS33 [get_ports div2_o]

set_property IOSTANDARD LVCMOS33 [get_ports div3_o]

set_property IOSTANDARD LVCMOS33 [get_ports div4_o]

set_property IOSTANDARD LVCMOS33 [get_ports div8_o]

set_property IOSTANDARD LVCMOS33 [get_ports div1hz_o]

set_property PACKAGE_PIN U18 [get_ports clk_i]

set_property PACKAGE_PIN L15 [get_ports rst_n_i]

set_property PACKAGE_PIN M14 [get_ports div2_o]

set_property PACKAGE_PIN M15 [get_ports div3_o]

set_property PACKAGE_PIN K16 [get_ports div4_o]

set_property PACKAGE_PIN J16 [get_ports div8_o]

set_property PACKAGE_PIN R19 [get_ports div1hz_o]

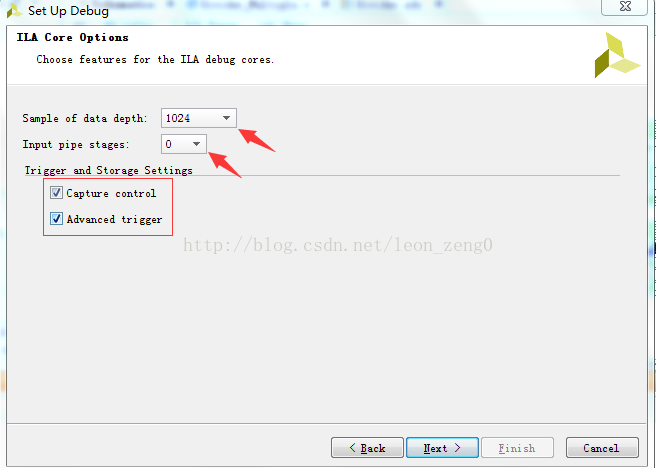

2 :设置调试参数

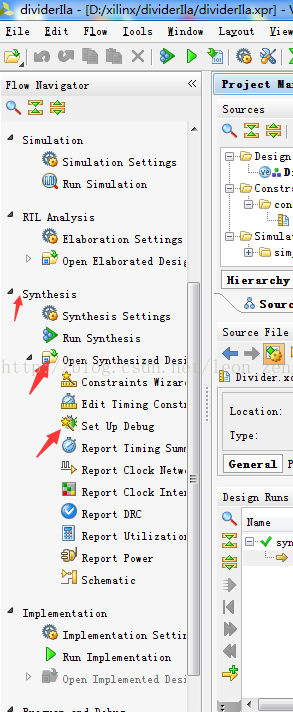

如果你还没有综合,那就先执行综合(Run Synthesis),需要一点时间, 然后按下图打开Synthesis -> Set up Debug

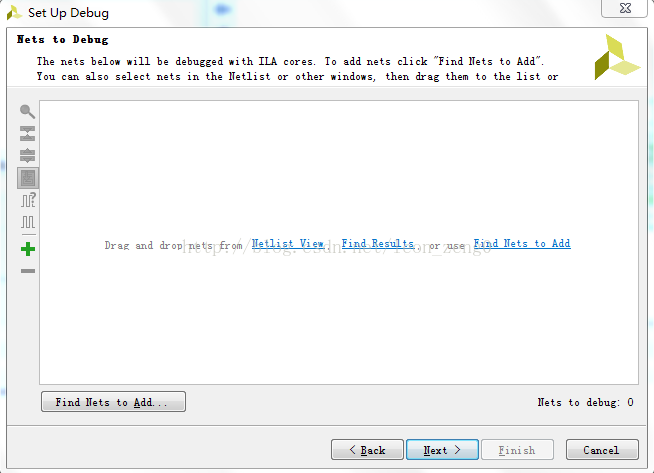

下面就是Set Up Debug 的开始对话框,一个网点也没有。我们需要添加要监控或触发条件的Net。

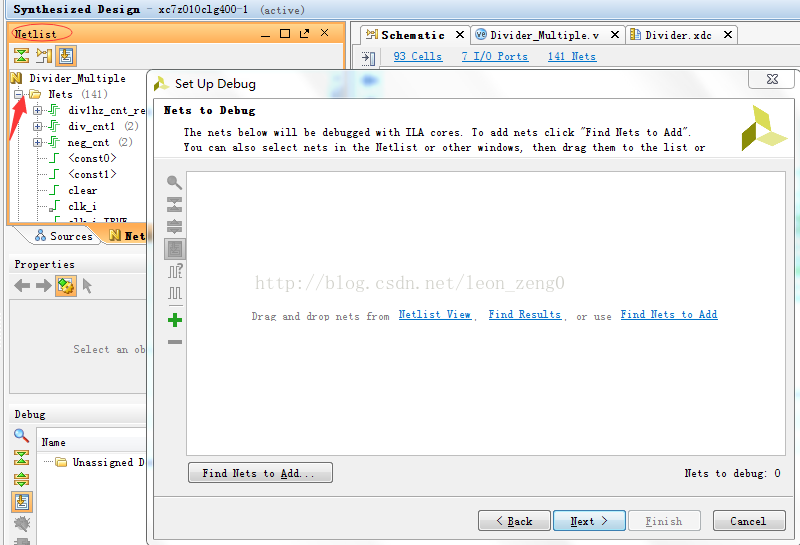

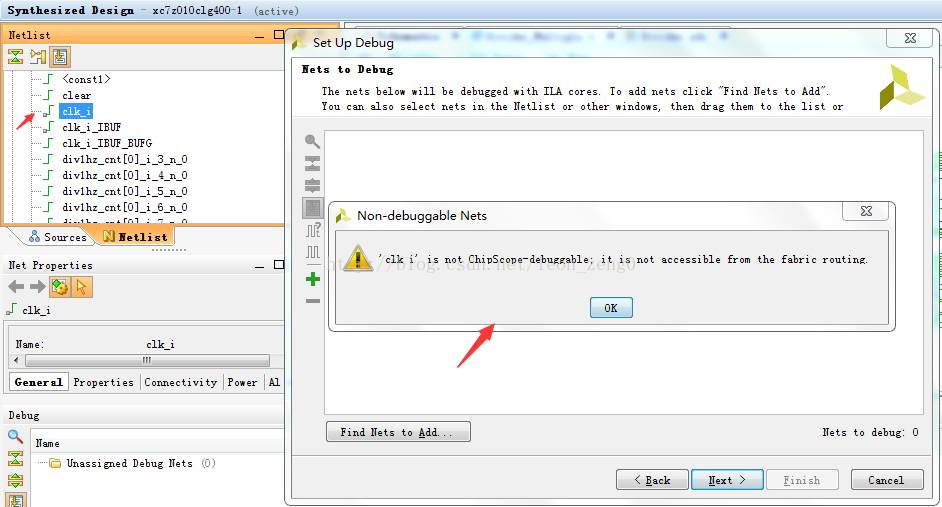

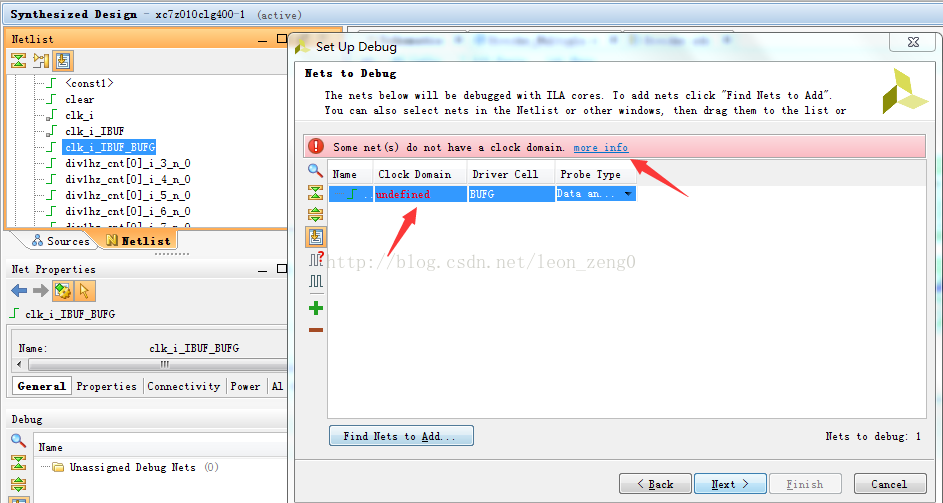

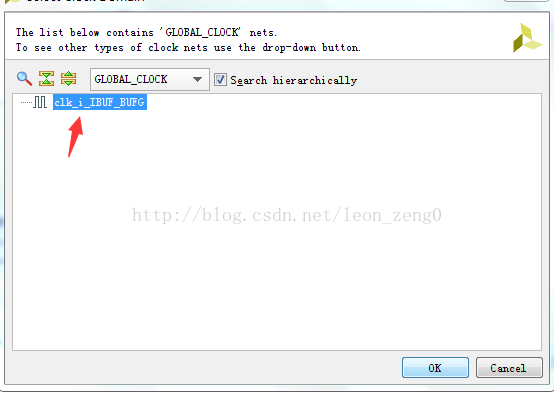

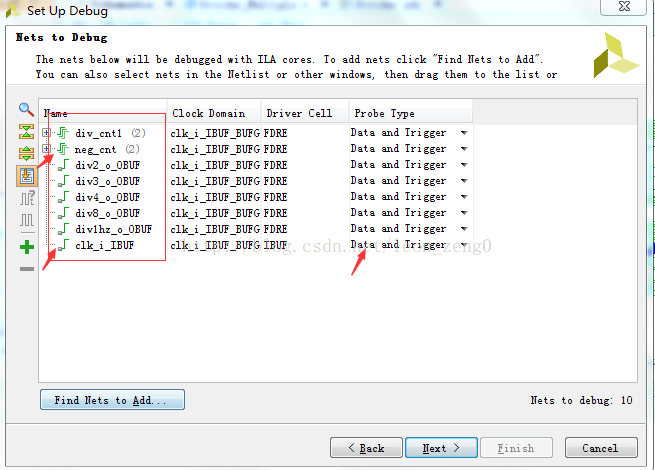

点击Netlist View:

这个时候出现了Netlist View, 点开Nets, 可以看到很多Nets ,右键加入或者直接拖拉

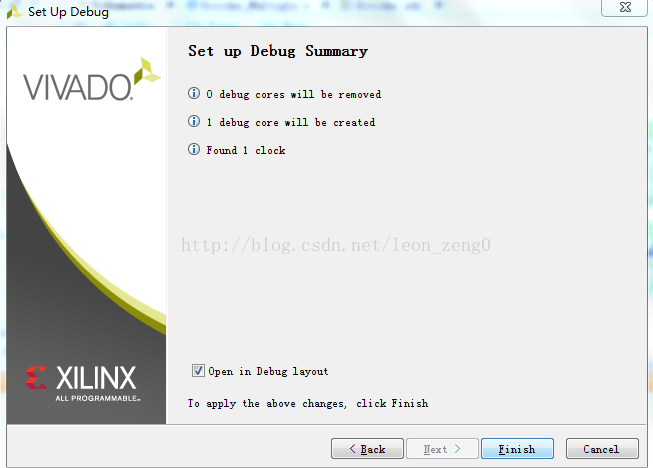

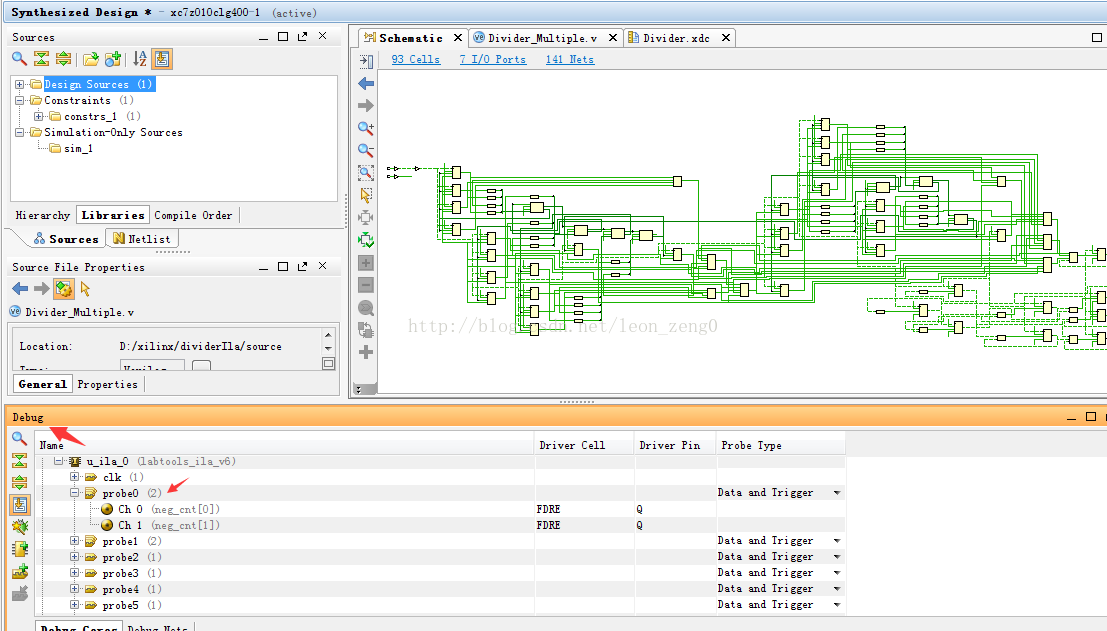

点击Finish,设置完成,出现如下视图,可以看到Debug 窗口。

3:后续操作

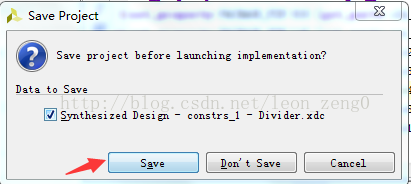

设置完成后,运行执行 (Run Implementation), 这个时候弹出一个对话框,我选择Save

原来我们做的这些设置,就是修改Divider.XDC 文件的内容,如下图点击Reload:

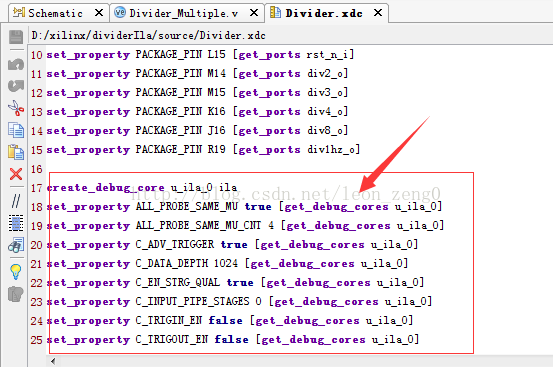

我们看到约束文件Divider.XDC 增加了好些内容。你能看懂吗,ug908都有介绍,

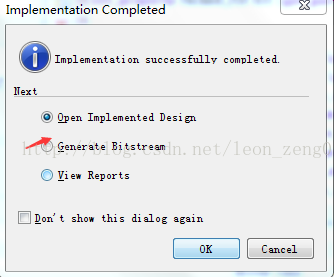

漫长的等待后,Implementation 终于结束了,这里我选择了红箭头选择,产生比特流。

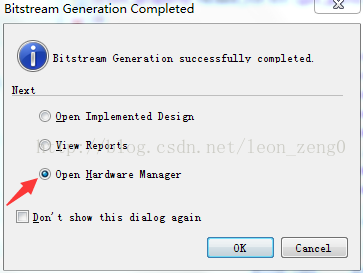

比特流也产生完了,我选择打开硬件管理

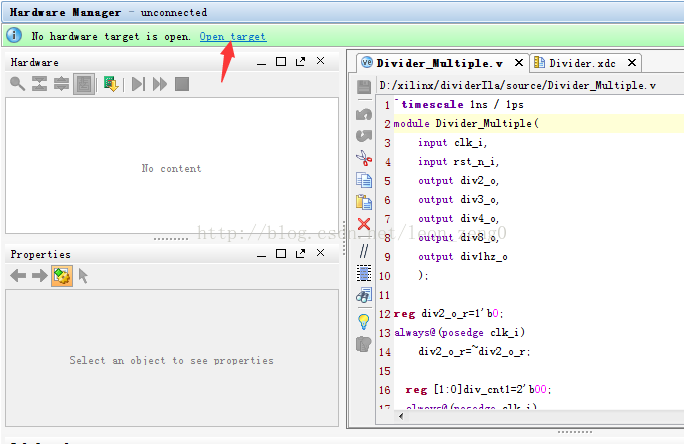

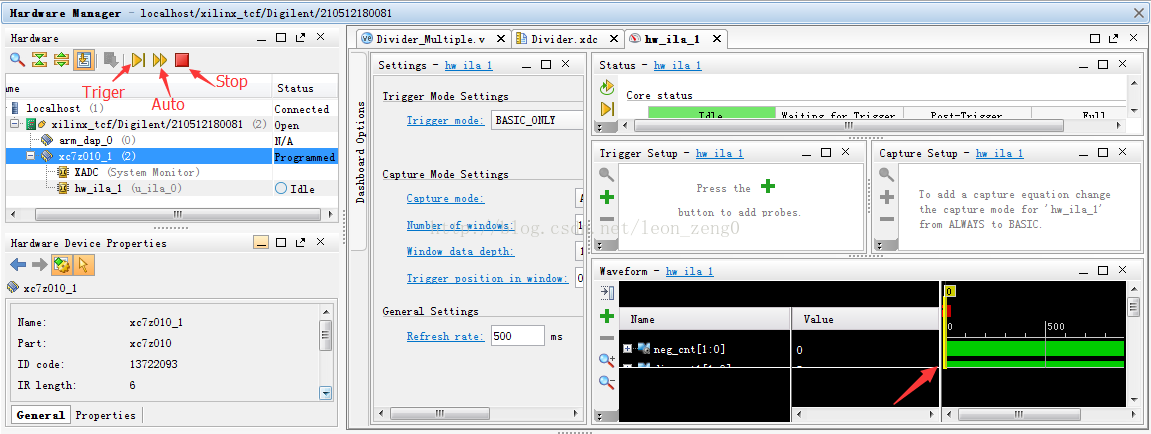

硬件管理的界面是这样的, 硬件目标还没打开。这时要打开你的硬件,其实我是一开始就准备好了,包括JTAG。

这是选择红箭 Open target

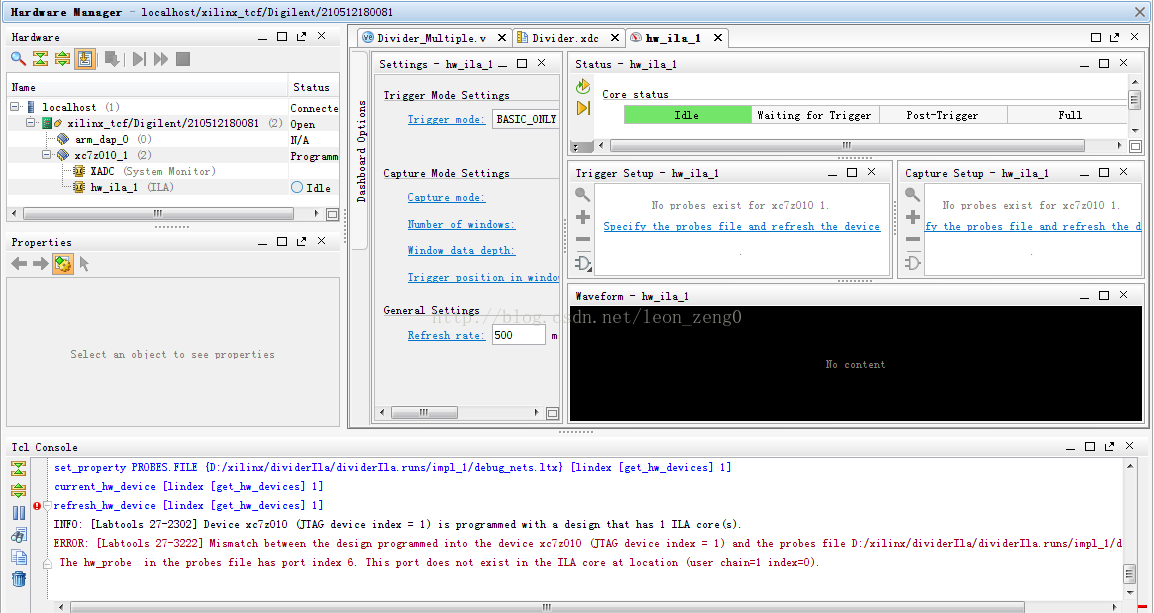

连接好目标是这样的,下面还有错误提示。什么意思,原来还没有下载。

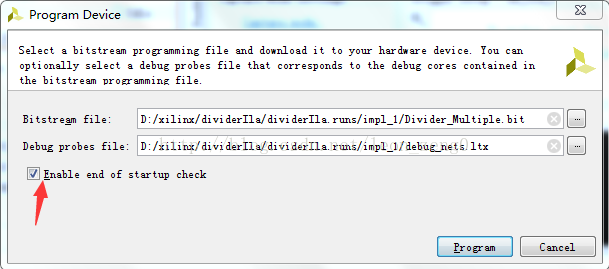

那我就下载,看上去要送2个文件下去,我还勾上直接启动。

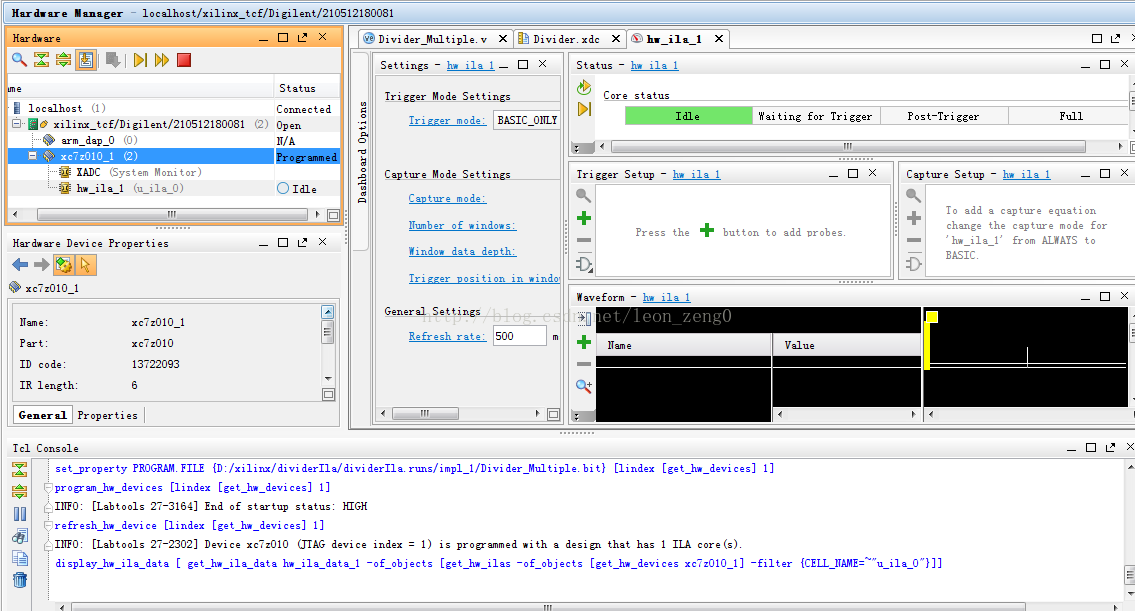

是的吧,下载后错误消失了。现在我们就要采样,看波形了。

4:波形采样和显示控制

通过上面一连串的操作,终于到了显示界面。左上方有3个红箭标注的就是采样控制操作,分别是:

Triger:触发控制,这个要设置触发条件,

Auto 直接触发

Stop 停止触发

这个就和示波器类似。

一定要触发采样,右边才有密密麻麻的波形出现。

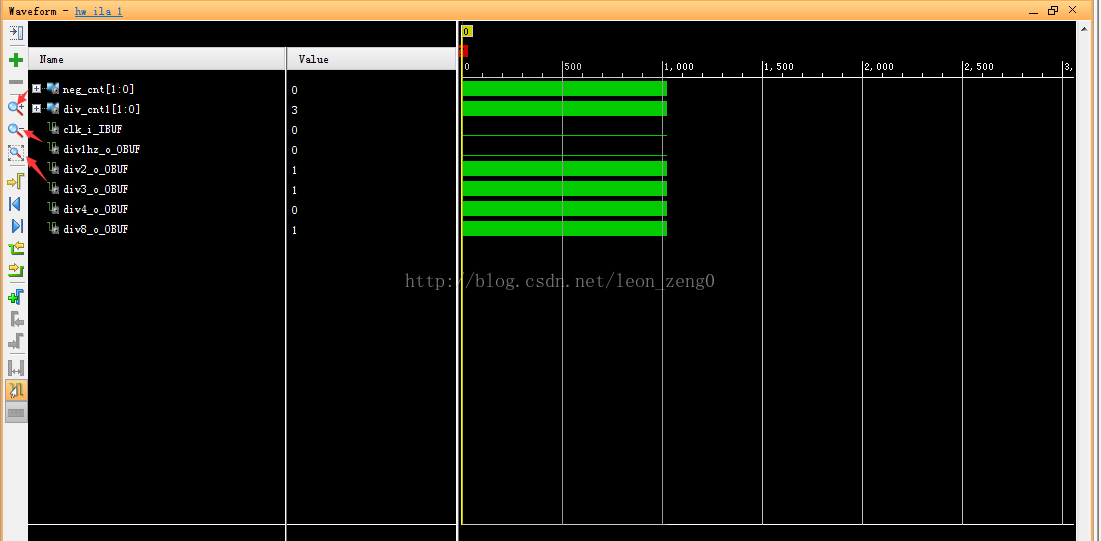

点击Wavefore 最大化,再最大化。容易看清楚一点。看看左边3个红箭的按钮

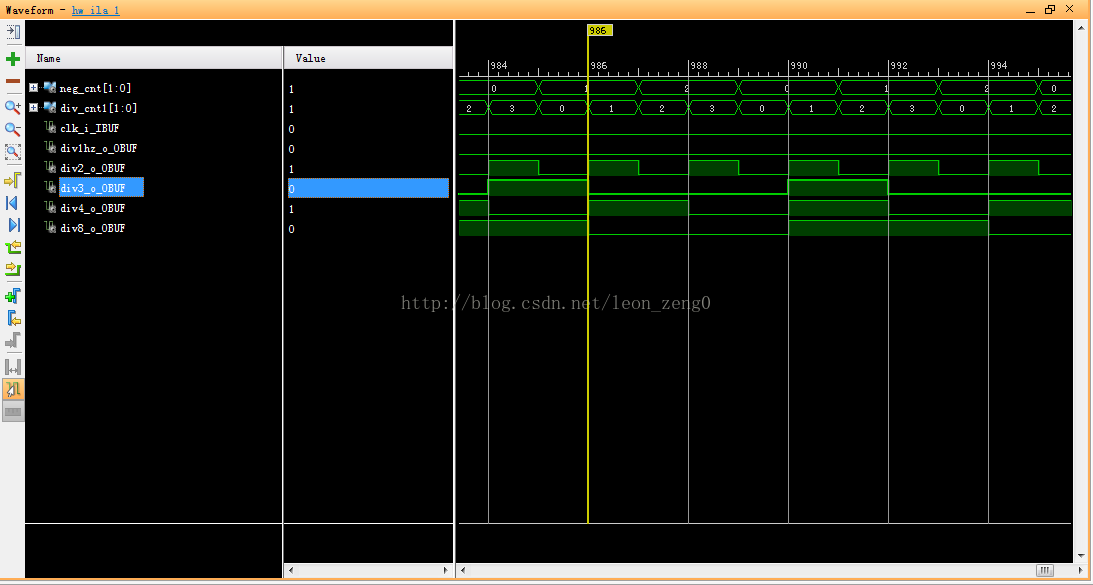

点击波形窗口左边的按钮,显示全部,放大,缩小,调整到波形比较清楚一点。这就是实测的波形,我第一次看到的时候很激动。

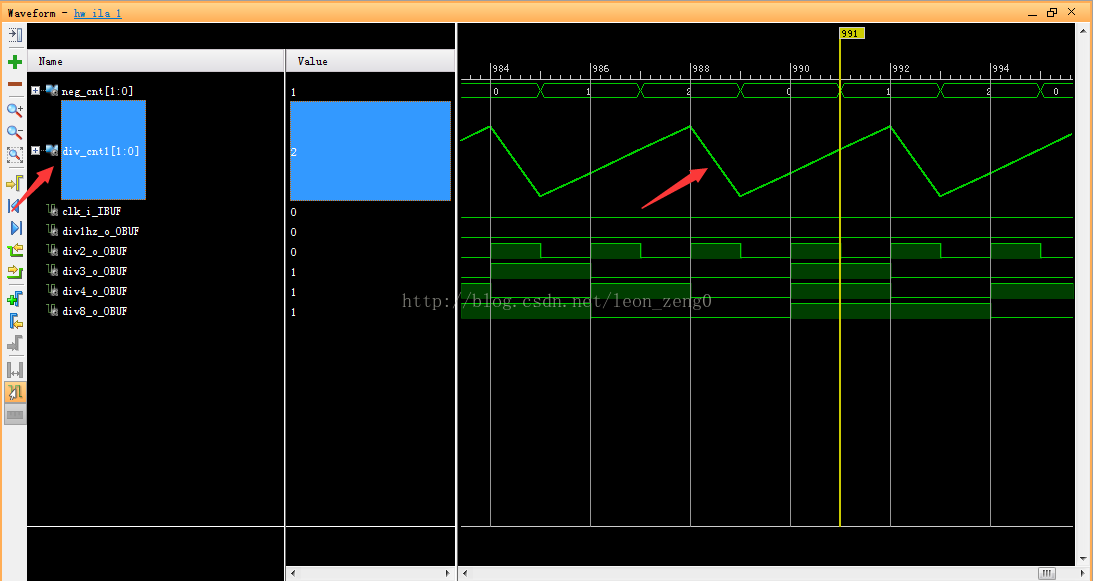

右键选择模拟方式看数据,看到模拟变化,而不是数据。

不要只是看看,动手自己做一次。右键一下,还有好些功能。就和大家分享到这里,希望对你有用。