刚开始学习vhdl和modelsim,这篇文章其实我是瞎写的,方便以后看现在的青涩!

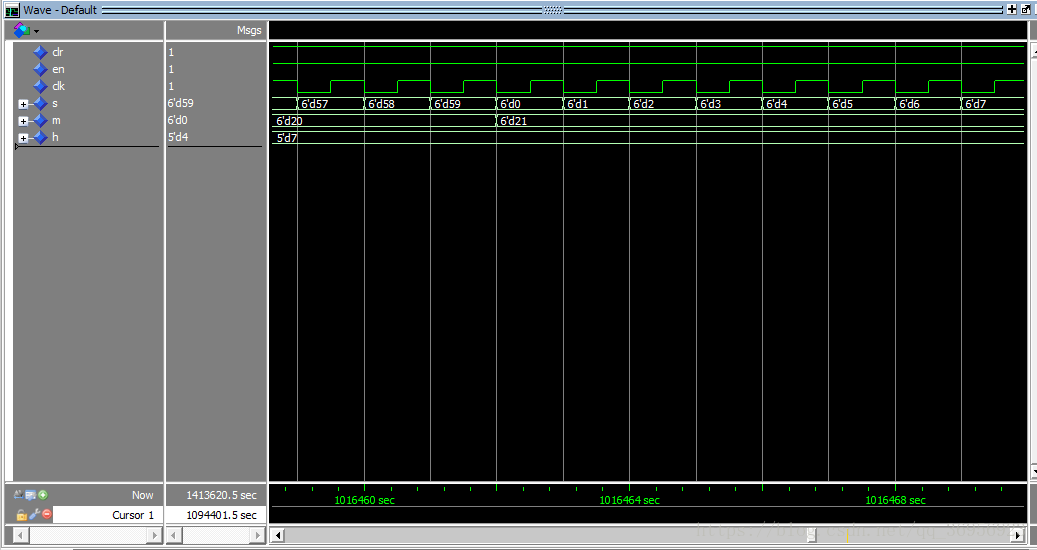

一开始自己在网上找了个六进制计数器,毕竟是抄来的,没什么成就感,闲着无聊就开始为难自己啦!想起大三的时候用msp430和1602做过一个时钟,当时是用c写的,现在想用vhdl写一下,看看能不能写出来,经过一下午的努力吧,算是写出来了,也不知道这个程序应该烧到什么芯片运行,管他呢。(有知道的大佬可以给我推荐几款便宜的芯片,让我把这个时钟做出来,其实我也不知道好不好使!)

Library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity cnt1 is

port

(

clr,en,clk :in std_logic;

s :out std_logic_vector(5 downto 0);

m :out std_logic_vector(5 downto 0);

h :out std_logic_vector(4 downto 0)

);

end entity;

architecture rtl of cnt1 is

signal tmp_s :std_logic_vector(5 downto 0);

signal tmp_m :std_logic_vector(5 downto 0):="000000";

signal tmp_h :std_logic_vector(4 downto 0):="00000";

begin

process(clk)

-- variable q6:integer;

begin

if(clk'event and clk='1') then

if(clr='0')then

tmp_s<="000000";

elsif(en='1') then

if(tmp_s="111011")then

tmp_s<="000000";

else

tmp_s<=unsigned(tmp_s)+'1';

end if;

end if;

end if;

s<=tmp_s;

-- qa<=q(0);

-- qb<=q(1);

-- qc<=q(2);

end process;

process(clk)

begin

if(tmp_s/="111011")then

tmp_m<=tmp_m;

elsif(tmp_m="111011")then

tmp_m<="000000";

else

tmp_m<=unsigned(tmp_m)+'1' after 1000 ms;

end if;

m <=tmp_m ;

end process;

process(clk)

begin

if(tmp_m/="111011")then

tmp_h<=tmp_h;

elsif(tmp_h="10111")then

tmp_h<="00000";

else

tmp_h<=unsigned(tmp_h)+'1' after 59500 ms;

end if;

h <=tmp_h ;

end process;

end rtl;

testbench:

library ieee;

use ieee.std_logic_1164.all;

entity cnt1_tb is

end cnt1_tb;

architecture rtl of cnt1_tb is

component cnt1

port(

clr,en,clk :in std_logic;

s :out std_logic_vector(5 downto 0);

m :out std_logic_vector(5 downto 0);

h :out std_logic_vector(4 downto 0)

);

end component;

signal clr :std_logic:='0';

signal en :std_logic:='0';

signal clk :std_logic:='0';

signal s :std_logic_vector(5 downto 0);

signal m :std_logic_vector(5 downto 0);

signal h :std_logic_vector(4 downto 0);

constant clk_period :time :=1000 ms;

begin

instant:cnt1 port map

(

clk=>clk,en=>en,clr=>clr,s=>s,m=>m,h=>h

);

clk_gen:process

begin

wait for clk_period/2;

clk<='1';

wait for clk_period/2;

clk<='0';

end process;

clr_gen:process

begin

clr<='0';

wait for 1500 ms;

clr<='1';

wait;

end process;

en_gen:process

begin

en<='0';

wait for 2500 ms;

en<='1';

wait;

end process;

end rtl;