7人表决器,即大于等于3个人同意,结果为成功。用逻辑0和1表示就是超过3个1为真用‘1’表示,不成功用‘0’表示。则其程序如下:

library ieee;

use ieee.std_logic_1164.all;

entity qb7 is

port(

a:in std_logic_vector(6 downto 0);

b:out std_logic

);

end;

architecture bhv of qb7 is

begin

process(a)

variable Q :integer;

begin

Q:=0;

for n in 0 to 6 loop

if(a(n)='1') then Q:=Q+1;

end if;

end loop;

if Q>=4 then b<='1';

else b<='0';

end if;

end process;

end bhv;

在程序中,输入端口a,它的数据类型标准矢量类型(按位矢量输出)std_logic_vector(6 downto 0);即a<="1101101"可以这样赋值。

输出端口b,它的数据类型标准逻辑型(包含bit'0'和'1')std_logic;对于输出的结果用'0'和'1'表示。

变量Q,它的数据类型是整形,因为Q是统计1的个数,故用整数类型替代。

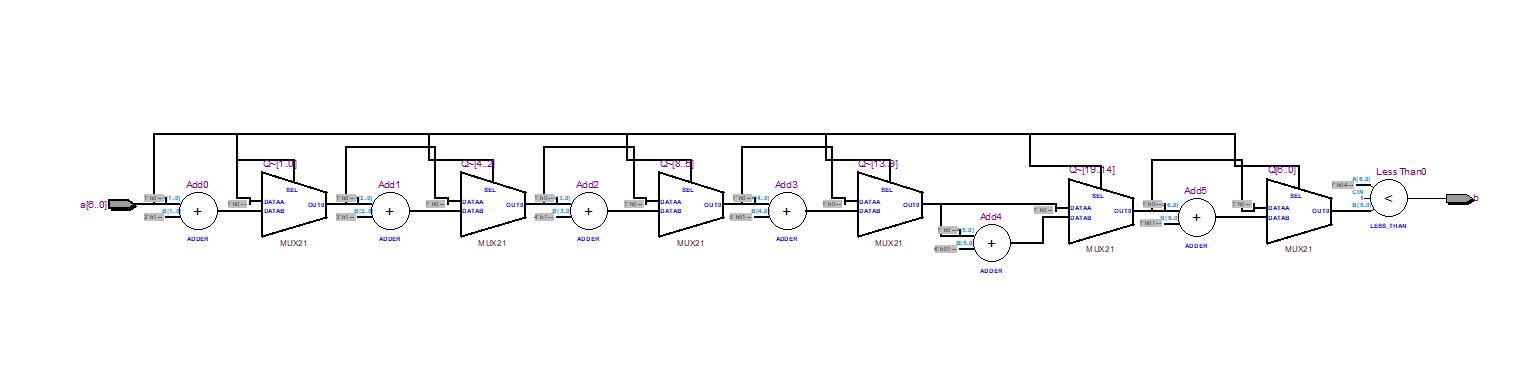

七人表决器的原理图:

七人表决器的仿真图: