Table of contents

- 1 Introduction

- 2. Implementation of MPEG2 video compression

- 3. My existing FPGA image and video codec scheme

- 4. My existing PCIE solution

- 5. MPEG2 video compression PCIE transmission design scheme

- 6. Detailed explanation of Vivado project

- 7. XDMA driver installation under Linux

- 8. Board debugging and verification

- 9. Benefits: Acquisition of engineering codes

1 Introduction

MJPEG, MPEG2, MPEG4, H264 are 4 popular and highly compatible video encoding formats. Among them, MJPEG performs JPEG image compression on each frame independently, without using inter-frame correlation, so the compression effect is poor. MPEG2, MPEG4, and H264 do interframe compression, but the latter two are more complex and perform better. Although MPEG2 is relatively old (1994), it has no obvious disadvantages with MPEG4 and H264 under the condition of low compression rate, so MPEG2 can still be used in applications requiring high quality and low compression rate. . .

PCIE (PCI Express) adopts the current popular point-to-point serial connection in the industry. Compared with the shared parallel architecture of PCI and earlier computer buses, each device has its own dedicated connection. It does not need to request bandwidth from the entire bus, and it can Improving the data transmission rate to a very high frequency and achieving the high bandwidth that PCI cannot provide is the preferred direction of high-speed interfaces in various industries at present, and has high practical value and learning value;

This design uses Xilinx's official XDMA solution to build a PCIE communication platform based on Xilinx series FPGAs. This solution is only applicable to Xilinx series FPGAs. It also provides XDMA installation drivers and QT host computer source codes, eliminating the need to use XDMA tedious drivers. I am at a loss for finding and developing PC software, and building a vivado project, saves the embarrassment of not knowing how to use XDMA, making the use of PCIE easy to use, without having to care about its complicated PCIE protocol; because I The development board only supports PCIE X1, so the code provided is the PCIE X1 architecture. If you need friends with PCIE X1, X2, X8, X16, X32, you can modify this project by yourself, or follow me, I will release new projects in real time .

This article describes in detail the design scheme of building a PCIE communication platform based on XDMA by FPGA. Taking advantage of the large logic resources of the development board, it realizes the functional test of MPEG2 video compression and transmission through PCIe; the engineering code can be comprehensively compiled and debugged on the board, and can be directly transplanted , suitable for project development of students and graduate students in school, and also suitable for project development of on-the-job engineers, which can be applied to the high-speed interface fields of medical, military and other industries; provide complete and smooth engineering source code

and technical support;

engineering source code and technology The way to obtain support is at the end of the article, please be patient and read to the end;

The difference between this design and the PCIE project I wrote before is that the hardware and software of this XDMA PCIE project run on the Linux system, and the driver installation, API calls and application software of XDMA are different from those running on the Windows system. PCIE application in Linux system, of course, users of Windows system can also refer to it, because XDMA is the same, only the driver installation is different;

2. Implementation of MPEG2 video compression

Regarding the implementation of MPEG2 video compression, I have written an article before. I suggest you look back and understand the principles and methods of MPEG2 video compression. Article link: https://blog.csdn.net/qq_41667729/article/details /129998492

3. My existing FPGA image and video codec scheme

My homepage has an FPGA image and video codec column, which includes not only mainstream video codecs such as MPEG2, H264, and H265, but also mainstream image codecs such as JPEG, JPEG-LS, and PNG; all use FPGA hardware to achieve codec acceleration; The following is the column address: https://blog.csdn.net/qq_41667729/category_12277772.html?spm=1001.2014.3001.5482

4. My existing PCIE solution

My homepage has a PCIE communication column, which includes PCIE solutions based on RIFFA and PCIE solutions based on XDMA; there are simple data interaction, speed measurement, and application-level image acquisition and transmission, as well as pure FPGA-based PCIE projects , there is also a PCIE project based on the zynq architecture, the following is the column address: https://blog.csdn.net/qq_41667729/category_12252265.html?spm=1001.2014.3001.5482

5. MPEG2 video compression PCIE transmission design scheme

MPEG2 video compression PCIE transmission scheme design architecture is shown in the figure below:

the design is divided into two parts: FPGA design and Linux software design;

FPGA hardware design

MPEG2 video compression:

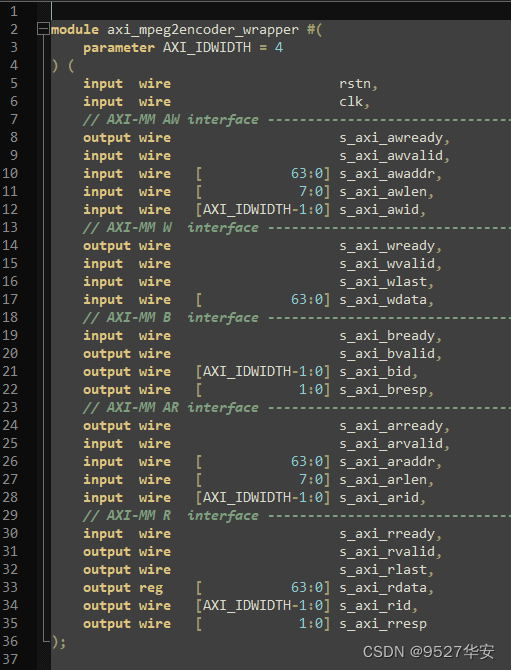

implemented in systemverilog language, belongs to YUV422 video stream, the output is 256-bit wide MPEG2 video stream, you can refer to the flow direction of the arrow in the design block diagram; on this basis, hang the MPEG2 video compression module on the AXI4 bus, here It is an AXI4 slave, so the final package of MPEG2 video compression is an AXI4 interface, which can directly interact with XDMA;

PCIe:

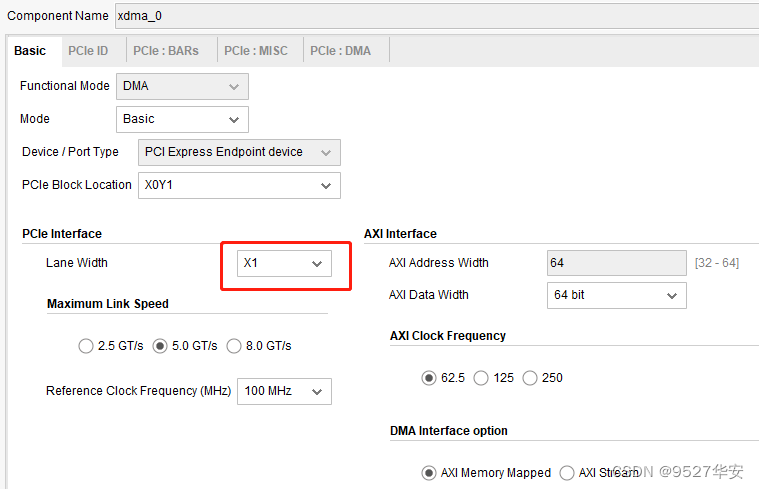

directly call the official XDMA, because my board only has PCIe X1 interface, so configure XDMA as X1 mode can also be configured as other modes such as X2 X4 X8; the specific configuration is as follows:

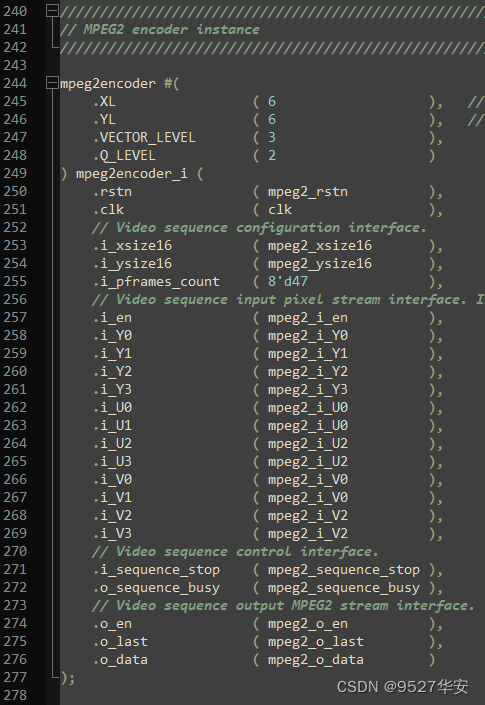

After MPEG2 video compression is mounted on the AXI4 interface, the top-level interface and instantiation part are as follows:

software design

Directly call the official XDMA API to implement software functions. The main function xdma_mpeg2encode.c implements two functions:

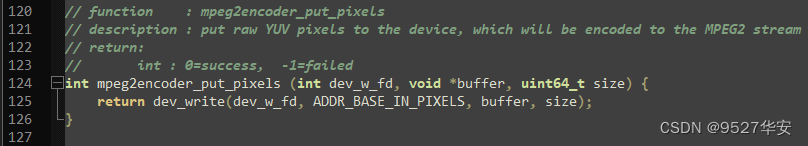

1: Send the .YUV format file to the PCIe sending port, and send it to the FPGA board through the PCIe bus. XDMA in the FPGA receives it through AXI4 The bus sends MPEG2 video compression as video input; the function sub-function of loading .YUV files is shown in the figure:

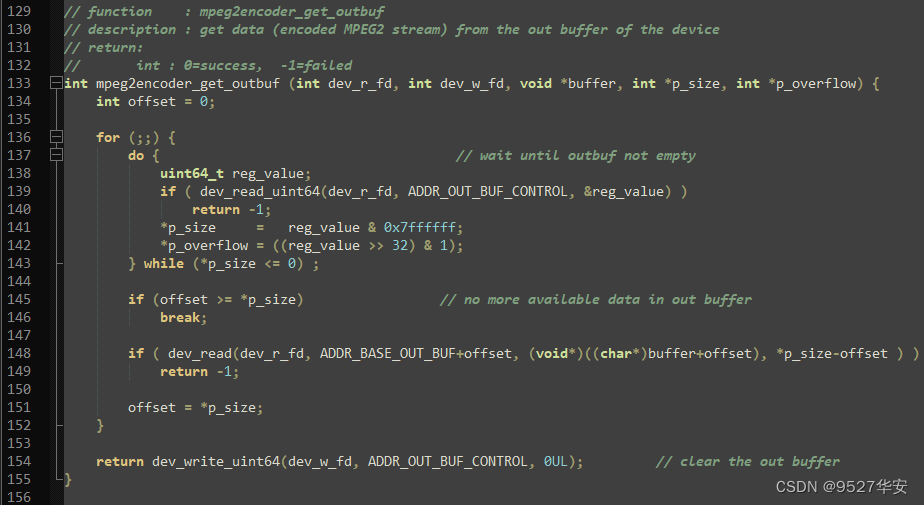

2: MPEG2 video compression in the FPGA receives the input video, real-time compresses the video into an MPEG2 video stream, and sends it through the AXI4 bus To XDMA, XDMA is sent to the computer through the PCIe bus. Another function of xdma_mpeg2encode.c is to receive MPEG2 video stream and convert it to a video file in .m2v format. The video of this file can be played by VLC player; read

MPEG2 The functional sub-functions of the video stream are as shown in the figure:

So far, a complete FPGA to realize the function of MPEG2 video compression PCIe transmission has been built. . .

6. Detailed explanation of Vivado project

Development board FPGA model: Xilinx–xc7vx690tffg1761-3;

development environment: Vivado2019.1;

input: software program feeds .YUV format video stream;

output: MPEG2 video stream software converted to .m2v format video file;

application: MPEG2 video compression PCIe acquisition card;

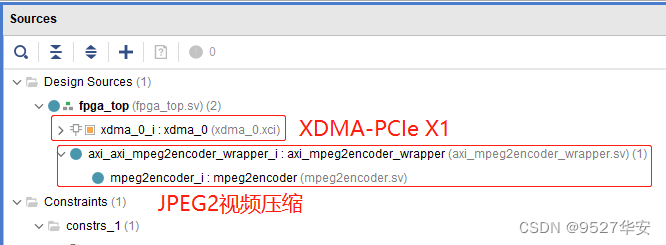

The project source code architecture is as follows:

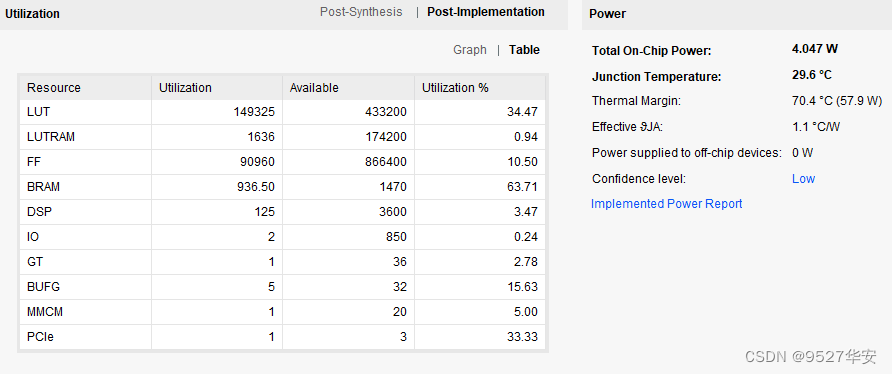

The FPGA resource consumption and power consumption estimates are as follows:

7. XDMA driver installation under Linux

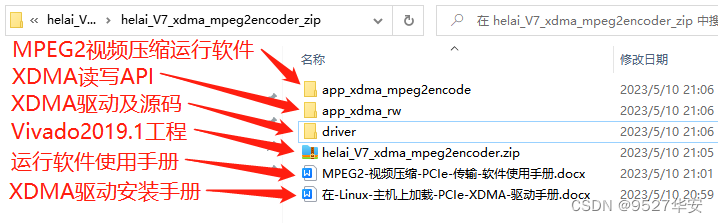

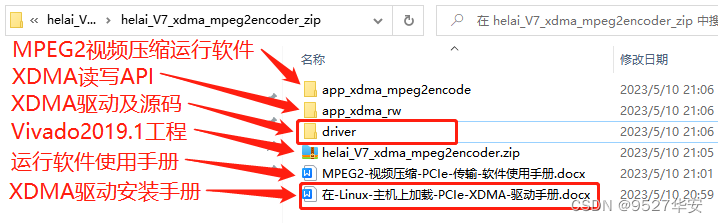

The XDMA driver and driver installation manual are provided in the data package, you can open the manual and install it, the location is as shown in the figure:

8. Board debugging and verification

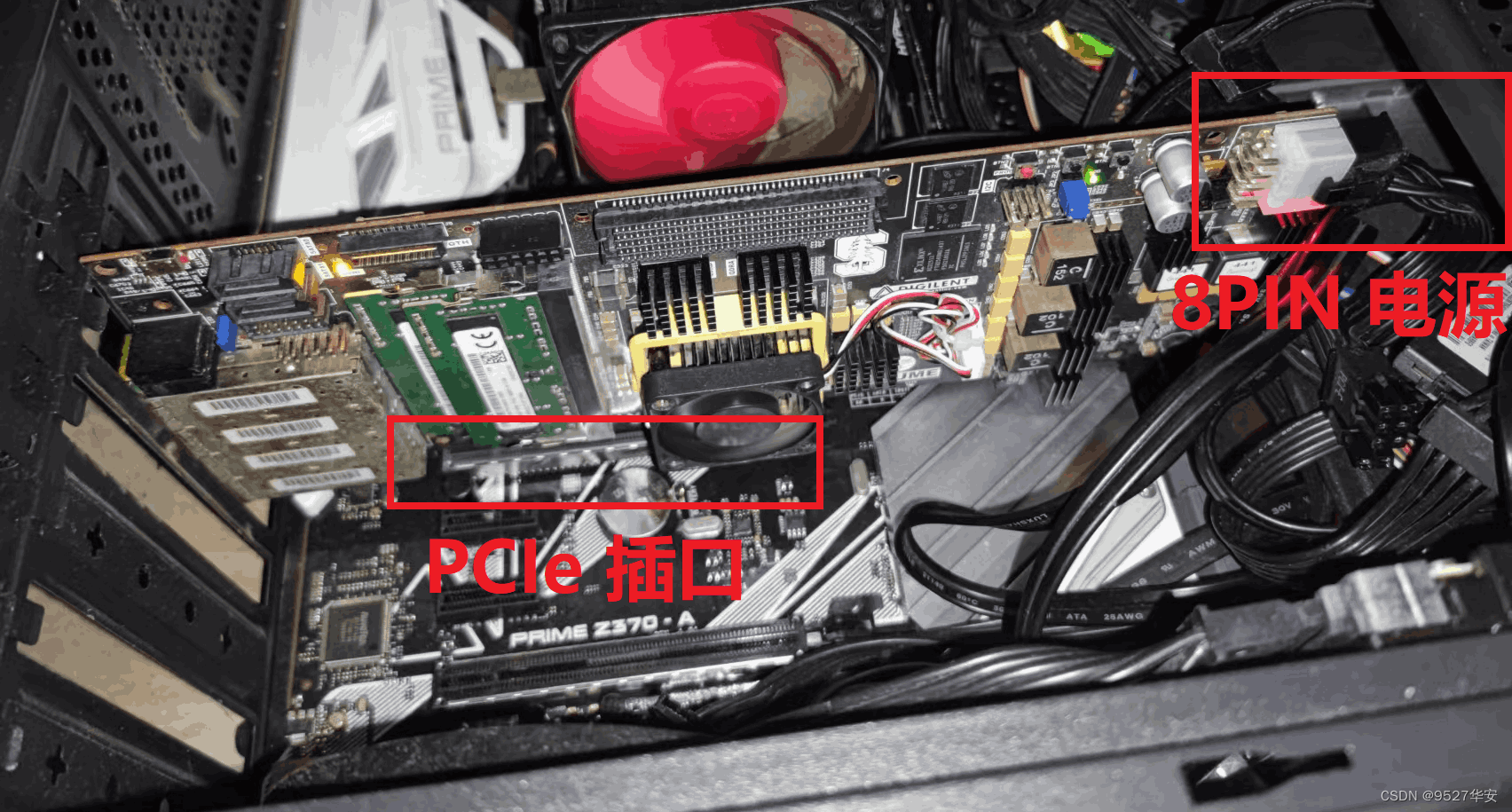

Step 1: First insert the FPGA board into the PCIE slot of the computer motherboard, as follows:

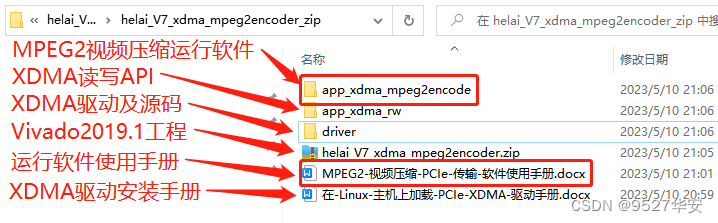

Step 2: Follow the software manual to execute the commands step by step. The data package provides the MPEG2 video compression operation software and software manual. Just execute the command step by step according to the software manual. The position is as shown in the figure:

Step 3: After executing the software, you can see the compressed MPEG2 video, and then play it with VLC player. The position of the generated video file is as shown in the figure :

Play the screenshot as follows:

9. Benefits: Acquisition of engineering codes

Benefits: Obtaining the engineering code

The code is too large to be sent by email. It will be sent via a certain network disk link, and

the data acquisition method: the V business card at the end of the article.

The network disk information is as follows: