Article Directory

ARM architecture and processor

-

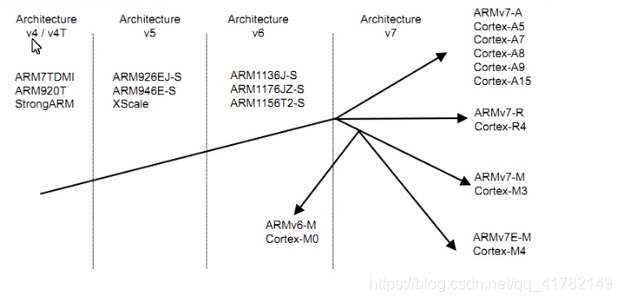

ARM series processors:

-

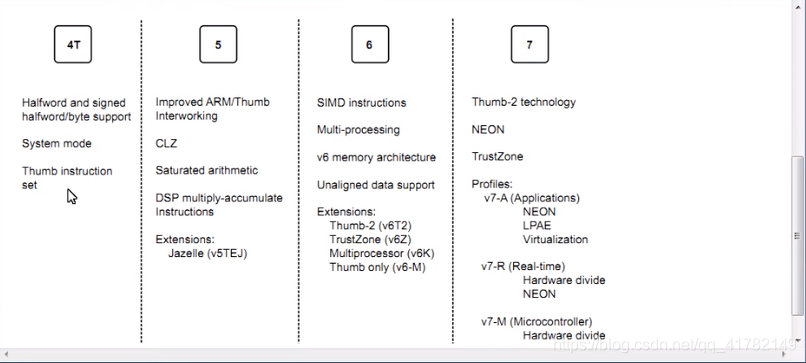

Different series and function evolution

-

Introduction to related terms

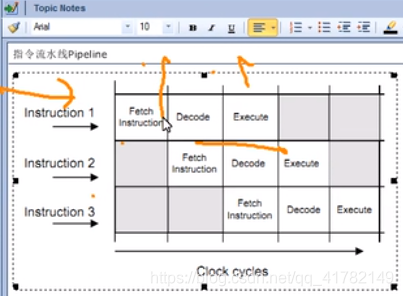

(1) Pipeline : CPU operation mechanism: instruction fetch (F) —> instruction translation (D) —> execution (E) three-stage pipeline, and multi-stage pipeline

(2) DSP : data signal processing

(3) Jazelle : Programming model for JAVA in ARM

(4) ThumbEE : Environment variables of Thumb instructions (16-bit instructions that assist ARM instructions)

(5) Thumb-2 : (16-bit and 32-bit instructions coexist)

(6) TrustZone : ARM Security architecture in the architecture

(7) VFP : Vector Floating-Point (vector floating-point calculation mechanism)

(8) Advanced SIMD (NEON)

(9) Lararge Physical Address Extension (LPAE)

(10) Virtualization

(11) Big LITTLE : For example Main processor: A15, co-processor: A8, solve energy consumption problems -

The key technical points of the ARM v7-A series

(1) 32-bit RISC processor, with 16 32-bit visible registers

(2) Haval structure (not Princeton structure) (instruction and data are stored separately)

(3) Thumb-2 instruction support

( 4) VFP and NEON optional

(5) Backward compatibility

(6) 4GB virtual address size and minimum 4GB physical address (4GB addressing)

(7) Large and small data access support

Some common tools

-

QEMU

QEMU is a set of free software for analog processors written by Fabrice BElla. It is similar to Brochs and PearPC, but it has some features that the latter two do not have, such as high speed and cross-platform features. Through kqemu, an open source accelerator, QEMU can simulate speeds close to real computers -

BusyBox

BusyBox is a software that integrates more than one hundred commonly used Linux commands and tools. Also known as the Swiss Army Knife in Linux tools. It integrates many tools and commands of compression theory linux, and also includes Sheel that comes with the Andriod system. -

Scratchbox

Scratchbox is a collection of tools to help cross-platform compilation of embedded Linux. Its main purpose is to make the development of embedded Linux applications easier. It also provides a complete integrated tool chain for cross-platform compilation and integration of a Linux distribution. -

U-Boot

U-Boot, the famous open source BootLoader -

UEFI and Tianocore

UEFI Unified Extensible Component Interface

ARM software tool chain

GNU-includes gcc and ARM-includes armcc

The process of generating an Image with the toolchain is as follows:

-

The GNU toolchain can be used to develop kernels and applications , including the following components:

– GNU make

– GNU Compiler Collection (GCC)

– GNU binutils linker, assembler and other object/library manipulation tools

– GNU Debugger(GDB)

– GNU build system (autotools)

– GNU C library (glibc or eglibc) -

Ubuntu install standard tool chain

sudo apt-get install gcc g+±doc -

Ubuntu install cross tool chain :

sudo apt-get install gcc-arm-linux-gnueabi

ARM registers, processor mode and instruction set

-

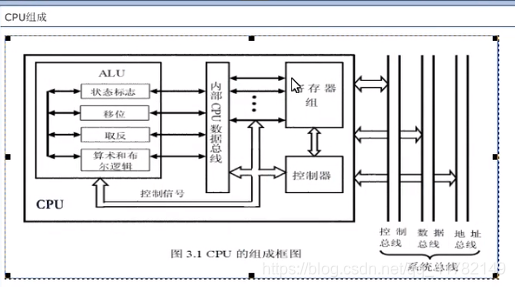

CPU composition

-

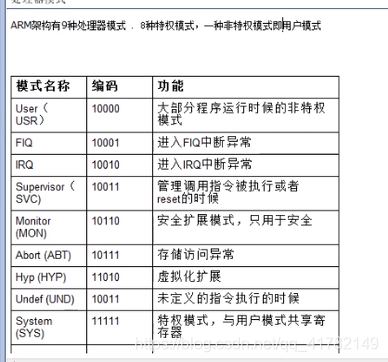

The processor mode

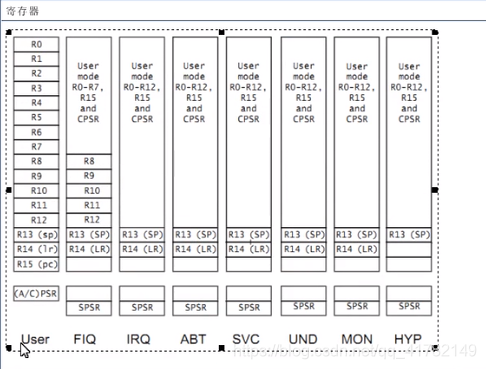

Cortex-A series includes: ARM architecture has 9 processor modes , 8 privileged modes , one non-privileged mode is the user mode,

among which User mode is called non-privileged mode, and the other 8 are called privileged mode -

Cortex-A series registers

R0-R12 13 general purpose registers and four special registers: the user mode

under FIQ other privileged mode: R0-R7 register user-mode R0-R7 of register sharing (of other modes (according to the figure can be obtained Out) -

Register summary :

(1) R0-R12 general purpose register, square general data, 32BIT

(2 ) R0-R12 and USER mode of each mode are shared (processing FIQ, R8-R12), PC, CPSR shared

(3) USER Mode without SPSRExplanation :

(1) SP - stack pointer (store stack address)

(2) LR - link register, store the return address of the subroutine

(3) PC - program counter

(4) APSR/CPSR - application status register, Current program status register

(5) SPSR-stored program status register -

Example sample :

(1) The program returns, which is actually MOV PC LR

(2) Jump to BL -

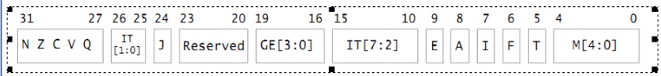

CPST instruction format:

where:

N — ALU negative number

Z — ALU zero

C — ALU carry operation

V — ALU operation overflow

Q — cumulative saturation instructions

J — Jaelle state

GE[3:0] — SIMD instruction uses

IT[7:2 ] — If, then conditional execution of Thumb-2 instruction

E — Operation storage byte order

A — Whether to disable Asynchronous abort

I — Disable IRQ Whether to disable IRQ

F — Disables FIQ, whether to disable FIQ -

Little-endian storage and big-endian storage

(1) Big-endian storage : means that the high byte of data is stored in the low address of the memory, and the low byte of data is stored in the high address of the memory. This storage mode is somewhat similar To treat the data as a string in order: the address increases from small to large, and the data is placed from high to low.

(2) Little-endian storage : It means that the high byte of data is stored in the high address of the memory, and the low byte of data is stored in the low address of the memory . This storage mode effectively reduces the high and low of the address and the data bit weight. In combination, the higher address part has a higher weight, and the lower address part has a lower weight, which is consistent with our logic method.

If a 32-bit integer 0x12345678 is stored in an integer variable (int), the storage of this integer variable in the memory in big-endian or little-endian mode is shown in the following table.

Little-endian: the higher effective byte is stored At higher memory addresses, the lower valid bytes are stored at lower memory addresses.

Big endian: The higher effective byte is stored in the lower memory address, and the lower effective byte is stored in the higher memory address. -

The instruction pipeline Pipeline is

extended to 5 stages of pipeline

The process of decomposing instructions:

(1) Instruction pre-fetch: Decide where to fetch instructions from the memory PreFetch

(2) Instruction read: Fetch instructions from the memory system

(3) Instruction decoding: interpret instructions and generate control signals

(4) ) Register read: Provide register value for operation unit execution

(5) Allocation: Assign instruction to execution unit

(6) Execution: Actual ALU unit processing

(7) Memory access: Data access

(8) Register write-back: Update running result to register