ARM register

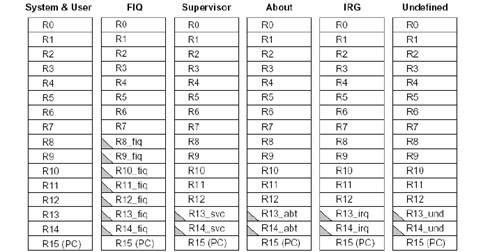

ARM total of 37 32-bit physical registers, the seven modes accessible registers in the table below, User, and System using the exact same physical register.

2.1 R0 ~ R7

all operating modes, R0-R7 respectively point to the same physical register (total of eight physical registers), they are not used for special purpose systems. When an interrupt or exception processing mode of conversion, due to the different operating modes use the same physical register, it may damage the data register.

2.2 R8 ~ R12

Visit in User & System, IRQ, Svc, Abt and Und mode R8 ~ R12 are the same physical register (Total physical registers); in FIQ mode, R8_fiq access ~ R12_fiq another separate physical register (Total physical registers).

2.3 R13 and R14

Independently at R13_ ~ R14 are each mode User & System, IRQ, FIQ, Svc, Abt and Und access physical registers (12 total physical registers).

R13 in ARM instructions commonly used for stack pointer (SP), but this is only an idiom, the user may also be used as a stack pointer register other. In the Thumb instruction set, some instructions require the use of R13 as a mandatory stack pointer.

Since each operating mode of the processor has its own separate physical register R13, the part of the user application initialization, the initialization R13 generally required in each mode, so that the stack space pointing mode of operation. Thus, when the program enters the abnormal mode may be placed in register R13 to be protected pointed stack, and when the program returns from exception mode, recovery from the corresponding stack, in this way ensures that the program exception occurs the normal execution.

R14 called a link register (Link Register), when executed subroutine call instruction (BL), R14 can be obtained R15 (the program counter PC) backup. In each mode, they are available R14 holds subroutine return address when a subroutine call with a BL or BLX instruction, the current value of the PC copy to R14, after executing a subroutine, in turn copy the value of R14 back to the PC, to complete the call subroutine returns. Described above can be used to complete the instruction.

Do any one instruction:

MOV PC, LR

BX LR

use the following command in the subroutine stack into the entrance of the R14:

STMFD SP! , {, LR}

corresponding to the following complete subroutine return instruction:

LDMFD the SP! , {,} The PC

R14 may also be used as general purpose registers.

2.4 Program Counter the PC (R15)

R15 in all modes of access are the same physical register, since the ARM architecture using a multi-stage pipeline technology, for the purposes of the ARM instruction set, PC always points to the current instruction in two instruction address, i.e., the current instruction value PC address value plus 8 bytes.

In ARM state, R15 [1: 0] is 0, R15 [31: 2] is used to save the PC; Thumb state, R15 [0] is 0, R15 [31: 1] to save the PC.

2.5 CPSR and SPSR

R16 as CPSR (Current Program Status Register, the current program status register), the CPSR can be accessed in any mode, including the condition flag disable bit, the current processor mode flag, and other related control and status bits.

When another mode of operation in each of the physical state has a dedicated register called SPSR (Specified Program Status Register, the backup program status register), when an exception occurs, the SPSR is used to save the current values CPSR exit from the abnormal SPSR can be made to restore the CPSR.

User mode and System mode does not belong to an abnormal pattern, they do not SPSR, the SPSR when accessing both modes, the result is unknown.

2.6 CPSR flags Bit Meaning

| 31 | 30 | 29 | 28 | 27 | 26 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| N | WITH | C | V | Q | DNM (RAZ) | I | F | T | M4 | M3 | M2 | M1 | M0 |

N (Negative) --- set to the value of the current instruction computation result bit [31] is. When two signed integer operation, N = 1 the calculation result is negative, N = 0 The result is positive.

Z (Zero) --- Z = 1 operation is zero; Z = 0 The results are shown in operation is not zero. For CMP instruction, Z = 1 represents a number equal to the size of the two compared.

C (Carried out) --- four cases discussed points

1) In addition instruction (including comparing the CMP instruction), when the result of a carry, then C = 1, represents the unsigned arithmetic overflow occurs; otherwise C = 0.

2) the subtraction instruction (including the CMP subtraction instruction), when the operation occurred borrow, then C = 0, represents the unsigned arithmetic overflow occurs; otherwise C = 1.

3) For non-subtract instruction includes the shift operation, the value of C is included in the last bit overflow

4) other non-subtract instruction, the bit C is generally unaffected

V (oVerflow) --- For add and subtract instructions if the operands and the result is a signed, V = 1's complement binary symbol represented by overflow; other instructions typically do not affect the V bit.

In ARM V5 Q --- E series processors, the CPSR the bit [27] is called Q flag, for indicating whether mainly enhanced DSP instructions overflow occurs. Spsr the same bit [27] is also known as Q-bit flag, to save and restore the CPSR flag Q at the time abort occurs. In the ARM V5 previous non-E series processors and ARM V5 version of the, Q flag is not defined.

I and F --- when I = ban IRQ interrupts 1, when F = ban FIQ interrupts 1

For ARM V4 T --- T series to later ARM processor, T = 0 indicates executing ARM instruction; T = 1 indicates Thumb instructions executed

for the ARM V5 and later versions of non-T family of processors, T = 0 It represents ARM instruction execution; T = 1 indicates a command to force the execution instruction generated an interrupt pending

M [4: 0] --- defines the ARM mode of operation, see particularly Table 1 CSPR [4: 0] ARM mode of operation defined

3 ways to perform process control program 3

1) during normal execution, each executing an ARM instruction, the program counter (PC), plus 4 bytes; Thumb instructions each instruction execution, the program counter register (PC) plus 2 bytes. The whole process is executed sequentially.

2) jump instruction, the program may jump to perform a specific address, or jump to a specific execution of subroutine. Wherein, B instructions for performing the jump operation; BL instruction in jumping operation performed at the same time, saving subroutine return address; BX instruction perform a jump operation at the same time, the program may be switched according to the target address to the Thumb state; instruction BLX, Back perform three operations, execution jumps to the target address, the address stored subroutine, the program may be switched according to the target address to the Thumb state.