The Principles of Computer Organization Chapter 3 Knowledge Summary

(It is summarized based on the class of teacher Liu Hongwei of Harbin Institute of Technology)

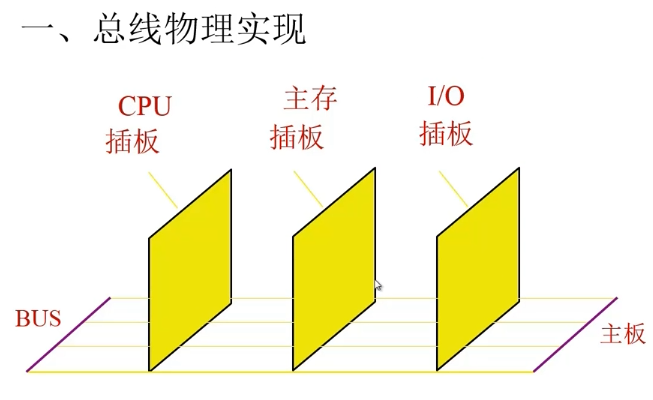

The basic concept of the bus

Causing the information transmission bus to the various components of the various components of the shared transmission medium

The bus does not allow two or more components to send information to it at the same time, because it will cause signal conflicts and invalid transmission.

Information transfer on the bus

- Serial

- parallel

Bus structure

-

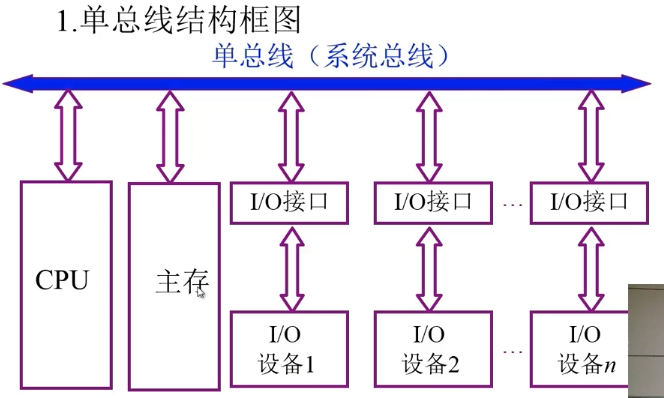

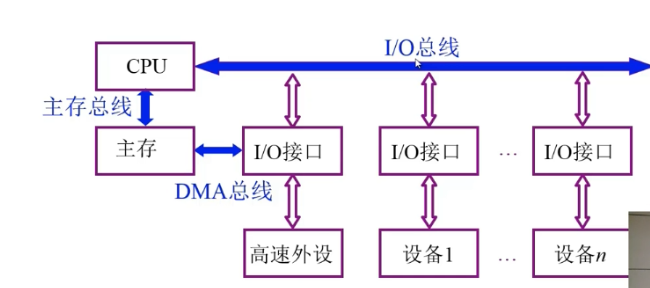

Single bus structure block diagram

Disadvantages: There is only one bus, and it is easy to conflict when multiple components send requests at the same time, so the priority of the components must be set.

-

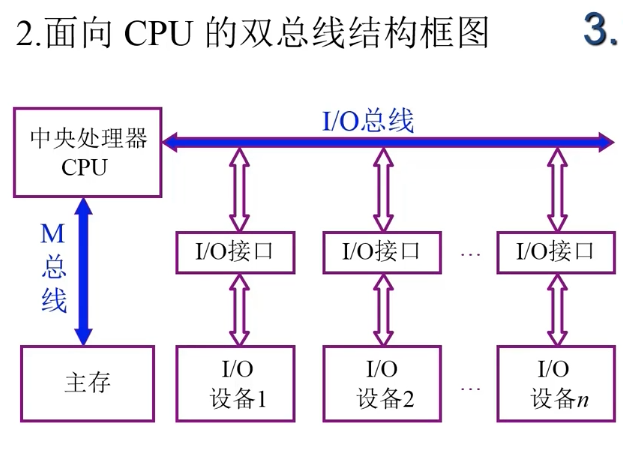

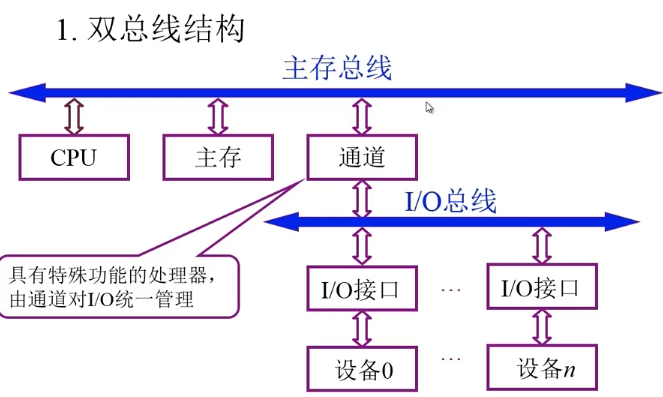

Double bus structure block diagram

-

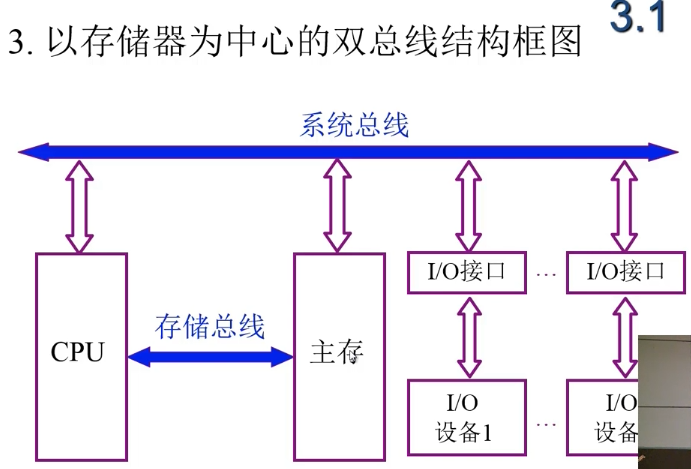

Memory-centric dual-bus structure block diagram

Disadvantages: This structure of I/O devices still occupy the CPU when exchanging information with the main memory, which will affect the work of the cpu.

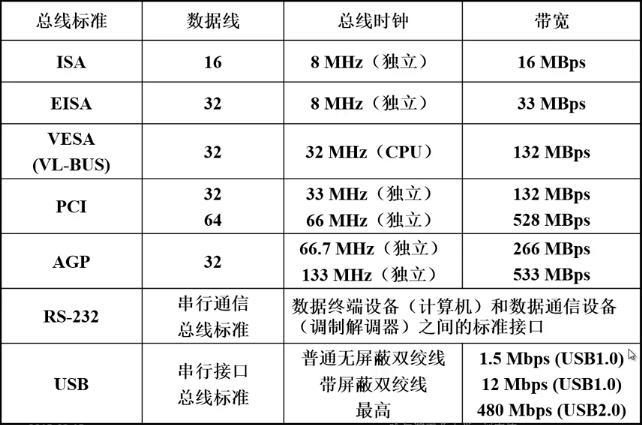

Bus classification

-

Chip bus chip bus

-

The system bus between the various components of the computer information transmission line

-

Communication bus

For between a computer system or a computer system with other systems of communication between

transfer method:

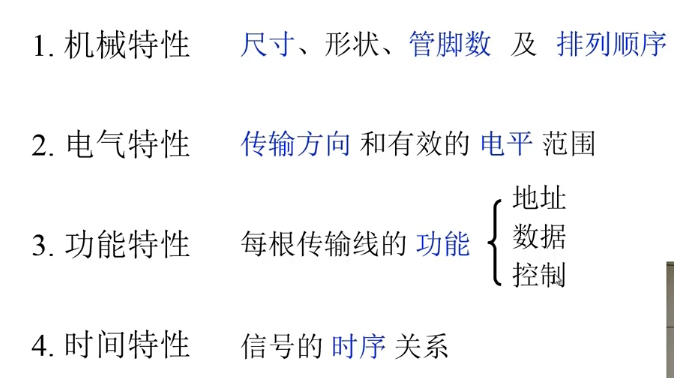

Bus characteristics and performance indicators

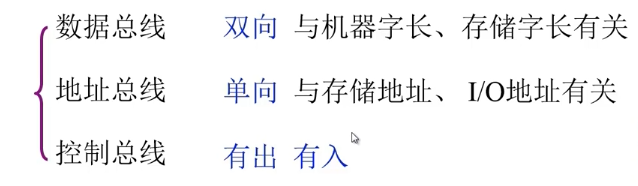

- The bus width of the data lines the number of

- The maximum number of bytes transferred per second at the standard transfer rate ( MBps )

- Clock synchronous / asynchronous synchronization , sync

- Multiplexed bus address lines and data lines multiplexed

- The number of signal lines of address lines, data lines and control lines of the sum

- Bus control mode: burst, automatic, arbitration, logic, counting

- Other indicators load capacity

Bus structure

-

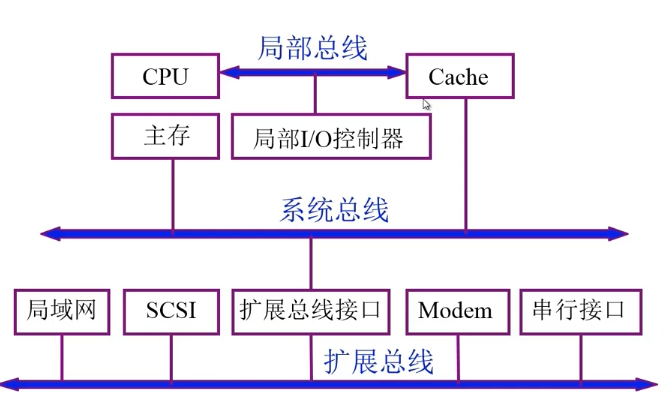

Dual bus structure

-

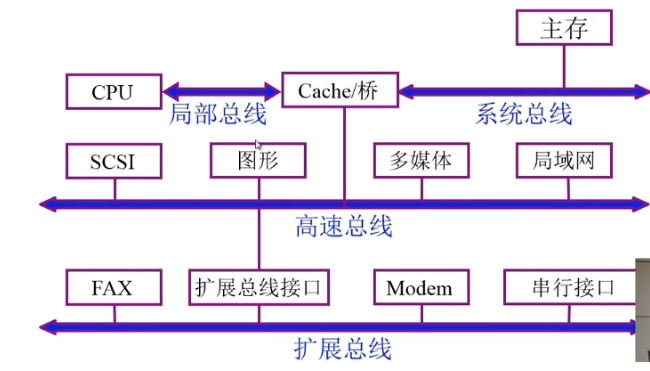

Multi-bus structure

Three bus structure

Another form of three-bus structure

Four bus structure

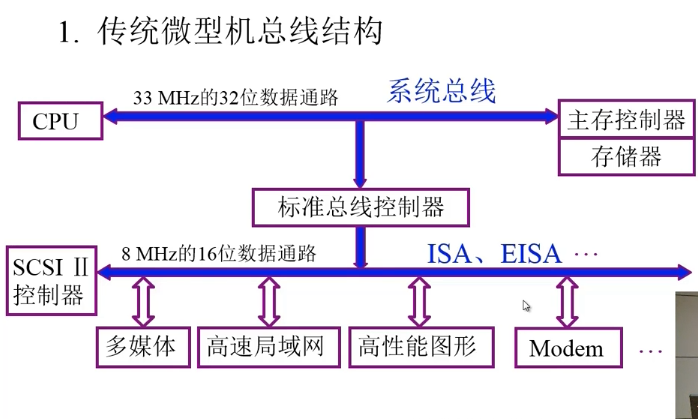

Example of bus structure

-

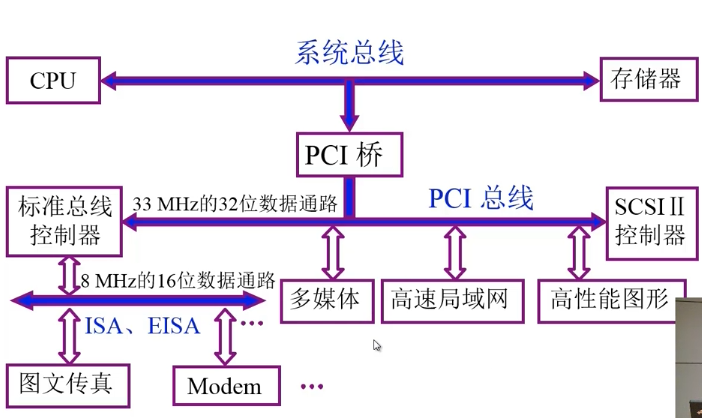

Traditional microbus structure

-

VL-BUS local bus structure

-

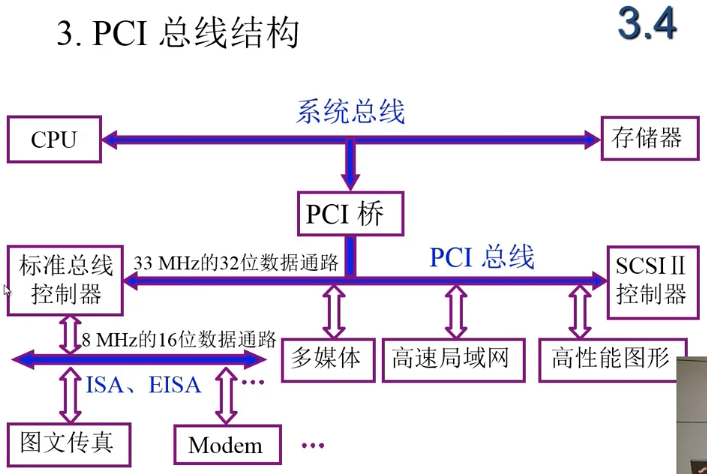

PCI bus structure

-

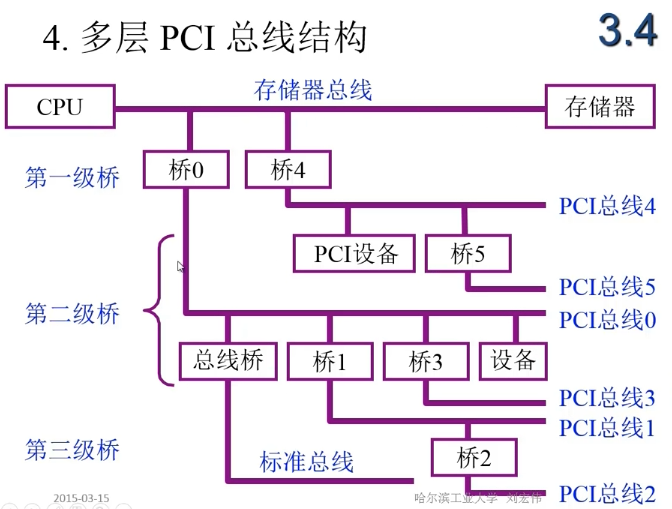

Multi-layer PCI bus structure

Bus control (emphasis)

Bus arbitration control

- basic concepts

- Master device (module) for Bus control

- The slave device (module) responds to the bus command sent from the master device

- Bus arbitration control

- Centralized

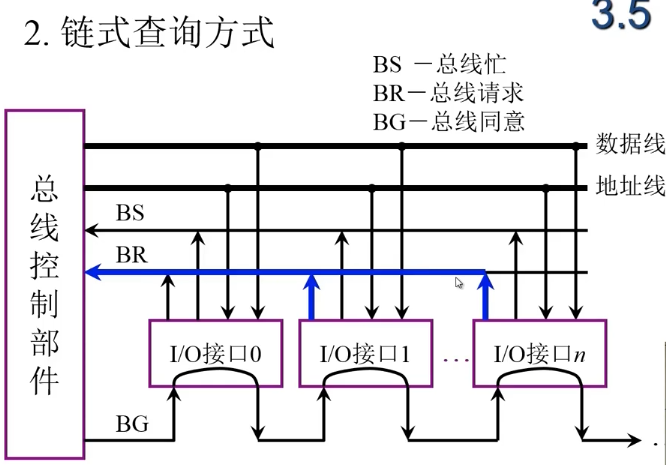

- Chain query

- Counter timing query

- Independent request query

- distributed

- Centralized

- Chain query

the way:

All I/O devices are connected to a BR line, so when a certain I/O device sends a request, it starts from the beginning (I/O as shown in the figure) and then queries until the first I sent the request is found. /O interface, the higher the priority, the higher the priority.

Disadvantages: Very sensitive to circuit failures. If the front equipment is broken, the latter will not work properly and will be slow.

Advantages: Only a few wires are needed to realize bus control according to a certain priority and easy to expand equipment.

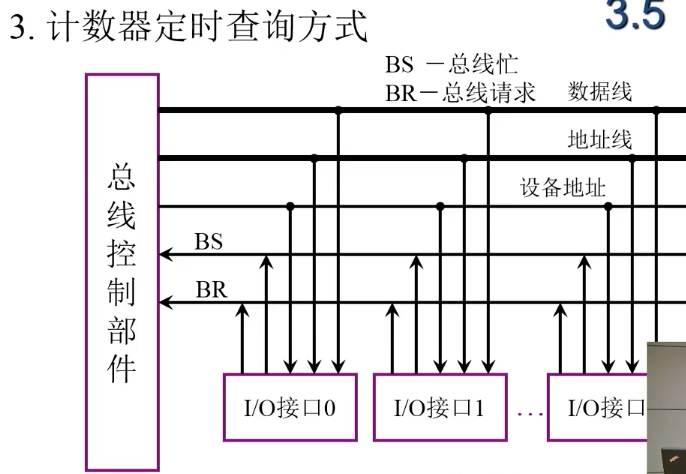

- Counter timing query mode

the way:

There is a counter in the bus control component, and the sequence of each query starts from the number in the counter. For example, if the counter is 0, then it starts from 0. The line judges whether 0 is the I/O device that sends the request, if not Then the counter is increased by one until the query is completed.

Advantages: It is possible to flexibly set high priority devices. For example, it can be started by the number that stopped counting last time, and it becomes a cyclic priority. It can also be set by software, and the circuit failure can be set every time. Kind of sensitivity.

Disadvantages: Increased the number of control lines, complicated control and slow speed.

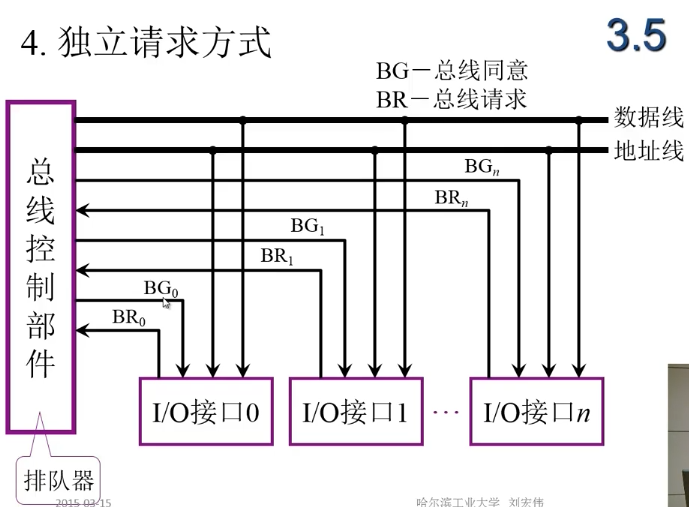

the way:

The priority can be set very flexibly, and the bus control component can assign priority to the requests sent from different devices according to the priority set by itself.

Advantages: fast speed, very flexible arbitration, and not very sensitive to circuit failures.

Disadvantages: many lines and complicated.

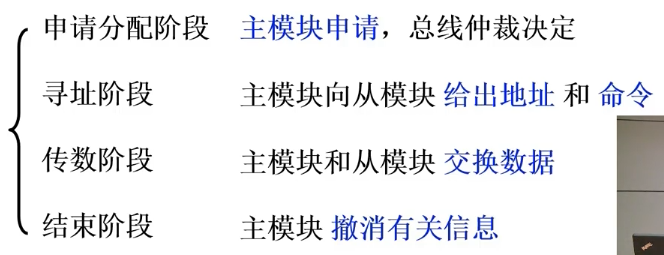

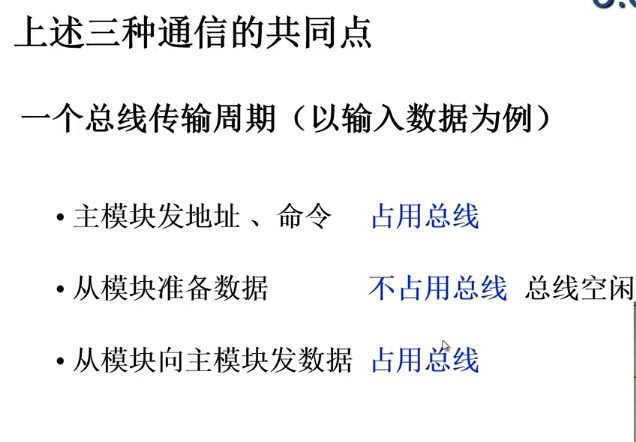

Bus communication control

-

The two sides aim to solve the communication coordination problem

-

Bus transmission cycle

-

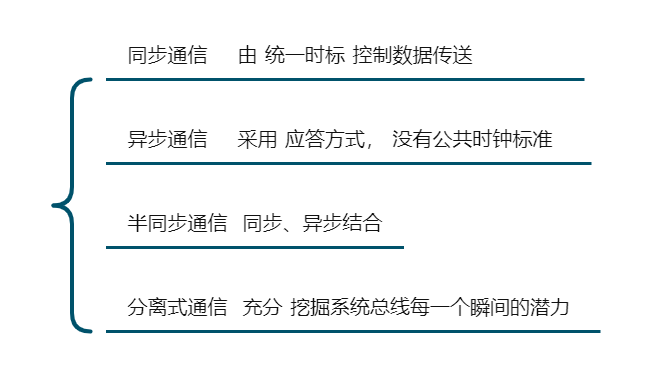

Four ways of bus communication

-

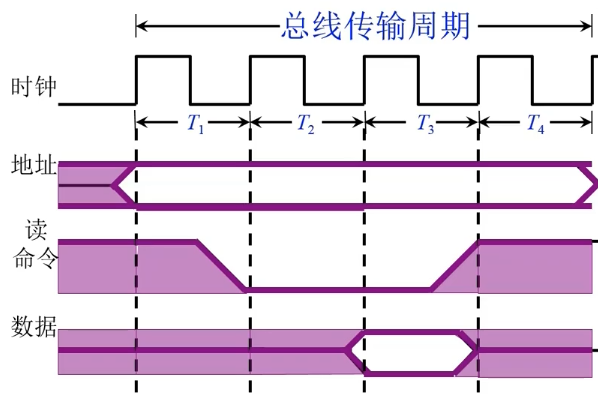

Synchronous data input

the way:

- Address information must be sent on the rising edge of T1;

- All commands are issued before the rising edge of T2, and the input device that matches the address information performs a series of internal operations according to the command;

- Send the data required by the CPU to the data bus before the rising edge of T3;

- In the T3 time period, send data from the bus to the internal registers of the CPU;

- The read command is cancelled at the rising edge of T4, the input device no longer transmits data to the data bus, and the drive to the data bus is cancelled.

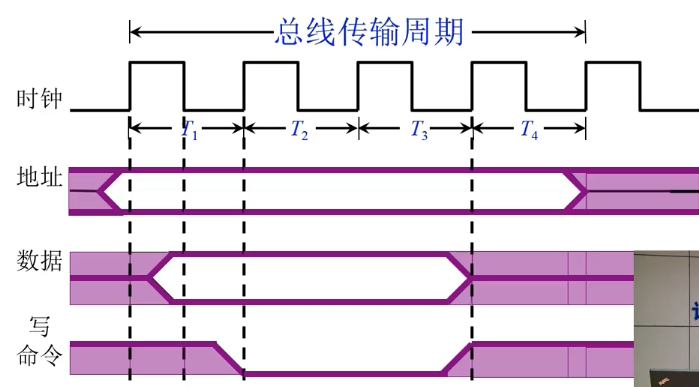

- Synchronous data input

The advantages of synchronous communication: clear and unified regulations, simple and consistent coordination between modules.

Disadvantages of synchronous communication: The time coordination of the slave master and slave modules is mandatory synchronization, and the specified requirements must be completed within a limited time, and there will be a short board effect, that is, the slowest device is used to design the common clock.

-

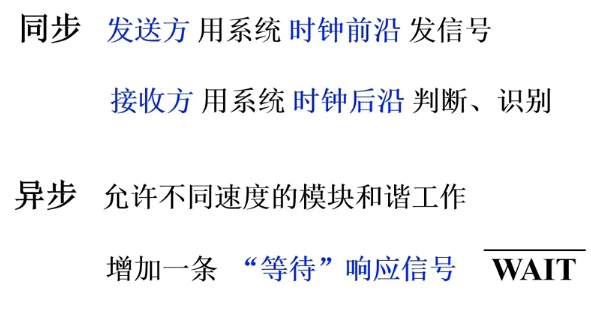

Asynchronous communication

-

Not interlocked

The master device sends a request to the slave device without the slave device's response. After a period of time is confirmed that the slave device receives the request signal, the request signal will be cancelled

-

Semi-interlock

The master device sends the request signal and must wait for the reply from the slave module to cancel its request signal. The slave device sends the reply signal after receiving the request signal. When there is no need to wait for the request signal of the master device to be cancelled, it is automatically cancelled after a period of time. It answers the signal.

-

Fully interlocked

The master device sends a request signal and must wait for the slave device to respond before canceling its request signal; the slave device sends a response signal, and must wait until the master device request signal has been cancelled before canceling the response signal itself.

-

-

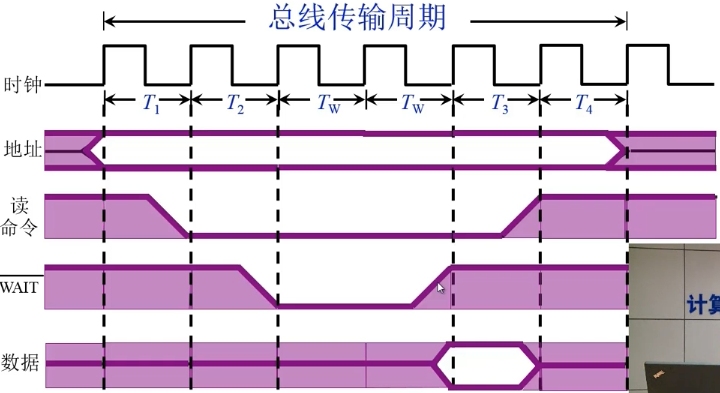

Semi-synchronous communication ( combination of synchronous and asynchronous )

The timing of semi-synchronous communication taking input data as an example:

The main module sends the address before the rising edge of T1

The main module sends a command before the rising edge of T2

Tw When WAIT is low, wait for a T

Tw When WAIT is low, wait for a T

.

.

.

(Until Tw is high, it means that the slave device is ready and enter T3)

Provide data from the module before the rising edge of T3

Data is withdrawn from the module before the rising edge of T4, and the command with the main module is cancelled

Disadvantage: The slave module does not occupy the bus when preparing data, causing waste.

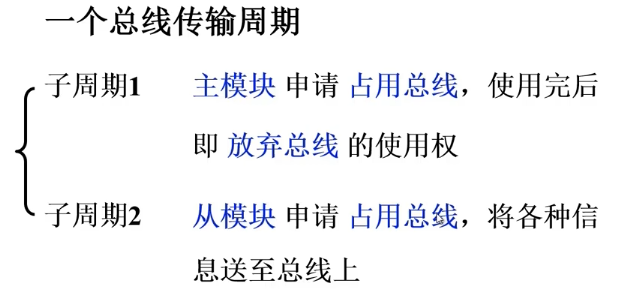

- Separate communication

Fully tap the potential of every moment of the system bus

Features of separated communication:

- Each module has the right to apply to occupy the bus

- Communicate synchronously without waiting for the answer from the other party

- When each module prepares data, it does not occupy the bus

- When the bus is occupied, no idle