18_PLL IP 核

1. 理论知识

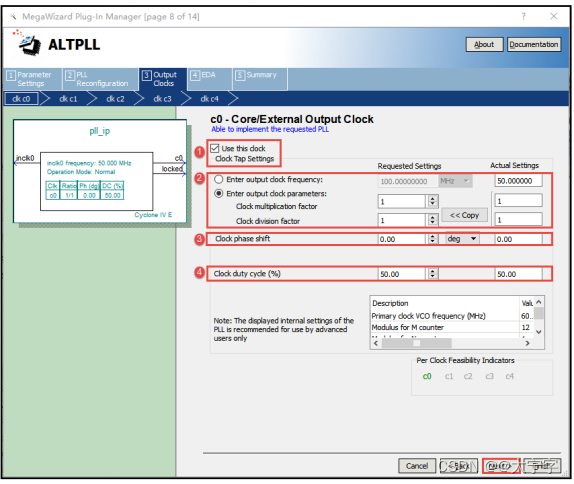

1)框 1 选项勾选是否使用当前的输出时钟,每个 PLL 最多有 5 个输出时钟,分别为 c0、c1、c2、c3、c4,其配置界面都相同。我们可以根据需要选择输出时钟的数量,c0 默认是选中的,保持该选项不变。

2)框 2 是配置输出时钟的频率,有两种方式:直接输入频率值(未选中的选项)和输入参数配置频率(当前选中的选项)。对于直接输入频率值的方式,直接在“Requested Settings”中输入想得到的输出频率即可;对于输入参数配置频率,需要输入倍频因子(Clock multiplication factor)和分频因子(Clock division factor),最后的输出频率计算方式为:输出频率=输入频率 *倍频因子/分频因子。另外需要注意的是:PLL IP 核的输出并非随心所欲的,受输入频率等因素影响,每个 PLL IP 核的输出频率会有一定的范围限制。

3)框 3 为设置输出时钟相对输入时钟的相移,默认设置是 0。

4)框 4 为输出时钟的占空比,默认设置是 50%。

2. 实验目标

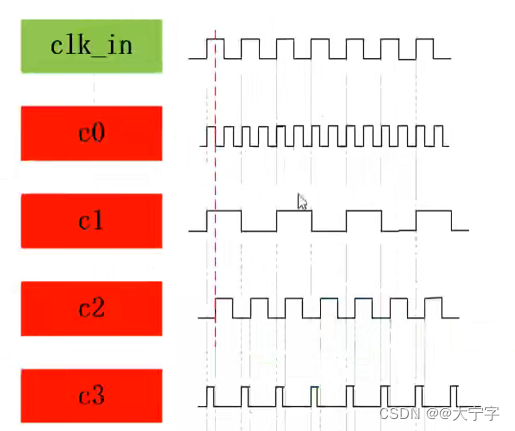

用PLL 实现下面得波形

3. PLL IP 核调用

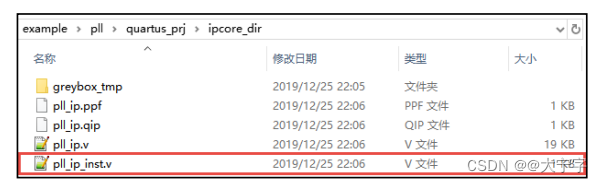

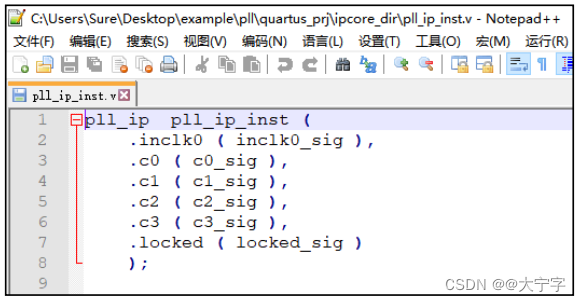

打开下图文件,查看里面得具体内容,具有哪些引用。

根据里面得内容设置参数。

4. RTL

module pll

(

input wire sys_clk , //系统时钟 50Mhz

output wire clk_mul_2 , //系统时钟经过 2 倍频后的时钟

output wire clk_div_2 , //系统时钟经过 2 分频后的时钟

output wire clk_phase_90 , //系统时钟经过相移 90°后的时钟

output wire clk_ducle_20 , //系统时钟变为占空比为 20%的时钟

output wire locked //检测锁相环是否已经锁定,

//只有该信号为高时输出的时钟才是稳定的

);

pll_ip pll_ip_inst

(

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div_2 ),

.c2 ( clk_phase_90 ),

.c3 ( clk_ducle_20 ),

.locked ( locked )

);

endmodule

5. testbench

`timescale 1ns/1ns

module tb_pll();

//reg define

reg sys_clk;

//wire define

wire clk_mul_2;//系统时钟经过 2 倍频后的时钟

wire clk_div_2; //系统时钟经过 2 分频后的时钟

wire clk_phase_90; //系统时钟经过相移 90°后的时钟

wire clk_ducle_20; //系统时钟变为占空比为 20%的时钟

wire locked; //检测锁相环是否已经锁定, //只有该信号为高时输出的时钟才是稳定的

//初始化系统时钟

initial sys_clk = 1'b1;

//sys_clk:模拟系统时钟,每 10ns 电平翻转一次,周期为 20ns,频率为 50Mhz

always #10 sys_clk = ~sys_clk;

pll pll_inst

(

.sys_clk ( sys_clk ),

.clk_mul_2 ( clk_mul_2 ),

.clk_div_2 ( clk_div_2 ),

.clk_phase_90 ( clk_phase_90 ),

.clk_ducle_20 ( clk_ducle_20 ),

.locked ( locked )

);

endmodule

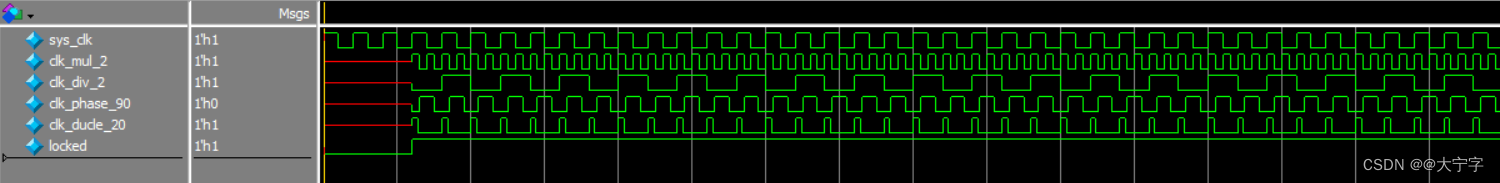

6. 结果