文章目录

前言

这几天在学习FPGA的IP核的知识,里面涉及了许多方法于是写博客方便后续的复习等。IP核在我目前的理解来说就像我们学习c语言的头函数一样,是别人已经实现封装的一个方法,我们需要进行引入并了解他的接口,具体看下面。

一、IP核是什么?

1、定义

IP(Intellectual Property) 即知识产权。在半导体产业将IP核定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。简而言之,这里的IP即电路功能模块。

在数字电路中,将常用的且比较复杂的功能模块设计成参数可修改的模块,让其他用户可以直接调用这些模块,这就是IP核。

2、优点

1、随着FPGA的规模越来越大,它的设计也是越来越复杂。

2、随着设计规模增大,复杂度提高,使用IP核可以提高开发效率,减少设计和调试时间,加速开发进程,降低开发成本,是业界的发展趋势。

3、IP核存在形式(依据产品交付方式)

1、HDL语言形式 — 软核

硬件描述语言; 可进行参数调整、复用性强;布局、布线灵活;设计周期短、设计投入少。

2、网表形式 — 固核

完成了综合的功能块;可预布线特定信号或分配特定的布线资源。

3、版图形式 — 硬核

硬核是完成提供设计的最终阶段产品-掩膜(Mask),缺乏灵活性、可移植性差;更易于实现IP核的保护。

4、缺点

1、IP核往往不能跨平台使用

2、IP核不透明,看不到内部核心代码

3、定制IP需额外收费

5、调用IP核的几种方式

1、Mega Wizard插件管理器(常用)

2、SOPC构造器

3、DSP构造器(仅支持部分IP核的例化使用)

4、Qsys设计系统例化(仅支持部分IP核的例化使用)

二、PLL-IP核

1.PLL-IP核简介

PLL (Phase Locked Loop,即锁相环)是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。

- 在Altera中,使用的锁相环是模拟锁相环,对应的还有数字锁相环。相对于数字锁相环,我们的模拟锁相环输出的信号稳定度高、相位连续可调、延时连续可调。但当温度过高或电池辐射过强会导致失锁。

1、工作原理

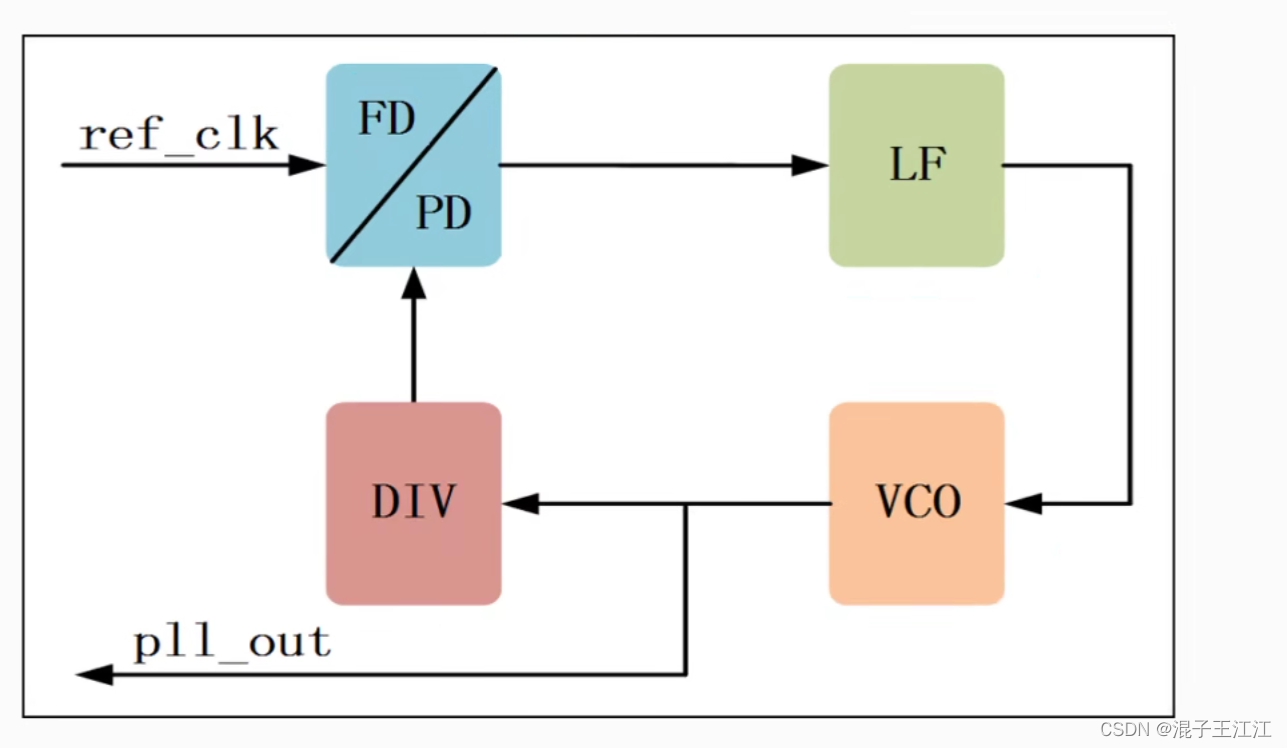

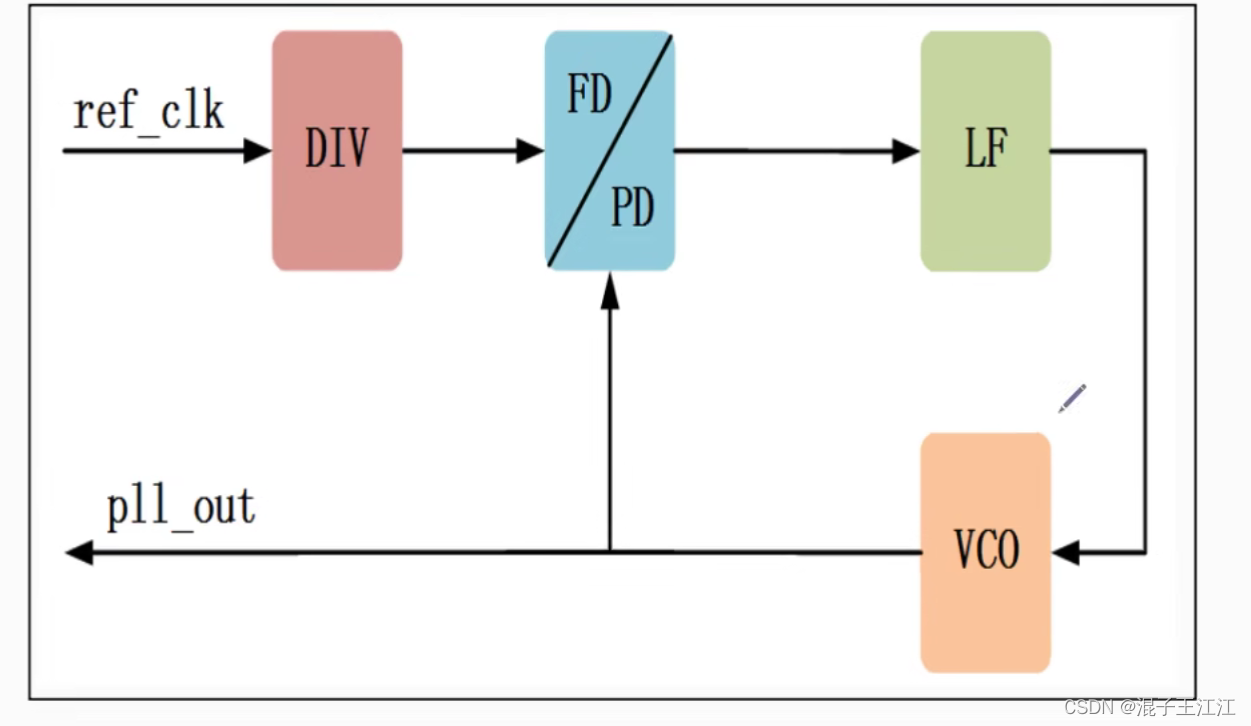

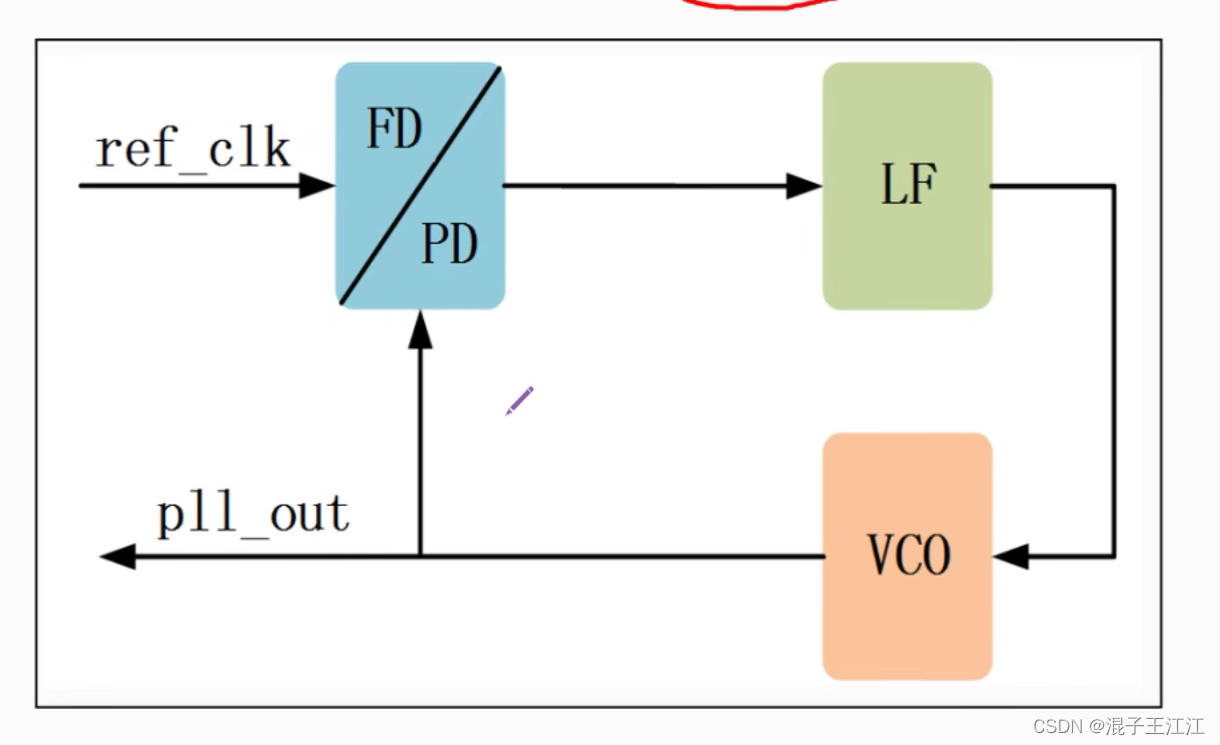

首先,我们的锁相环是一个反馈系统。输入到锁相环中的ref_clk是一个参考时钟,输入到鉴频鉴相器,FD是鉴频,PD是鉴相,此外输入鉴频鉴相器中的还有一个比较时钟,就是反馈的时钟。如果输入的参考时钟与比较时钟对比大小一致则输出0,表示相等,输出一个变大的成正比的一个值,表示大于,输出一个变小的成正比的,表示小于。鉴频鉴相器的信号输出到LF(环路滤波器),LF根据输入的不同值输出不同电压幅值。接着来到 VCO(压控振荡器),输入到压控振荡器的电压越高,输出信号的频率越高。在经过多次对比调节,参考时钟频率会与比较时钟频率相等,最后输出。

2、倍频

因为输入鉴频鉴相器的两个信号会趋于相等,那么在反馈时进行一个div,那么就会使的输出的信号增大几倍。那么你是否会想到,分频的话,div应该位于哪里?

3、分频

直接对输入的参考时钟进行分频的信号输入鉴频鉴相器,最终输出的信号与反馈信号一致,并且在鉴频鉴相器的中,反馈信号会与分频后的信号一致,便实现了分频。

2、PLL-IP核配置

首先,我们需要新建文件体系,四个文件夹sim、rtl、prj、doc。在prj中新建工程,参考:

https://blog.csdn.net/qq_52215423/article/details/128006883

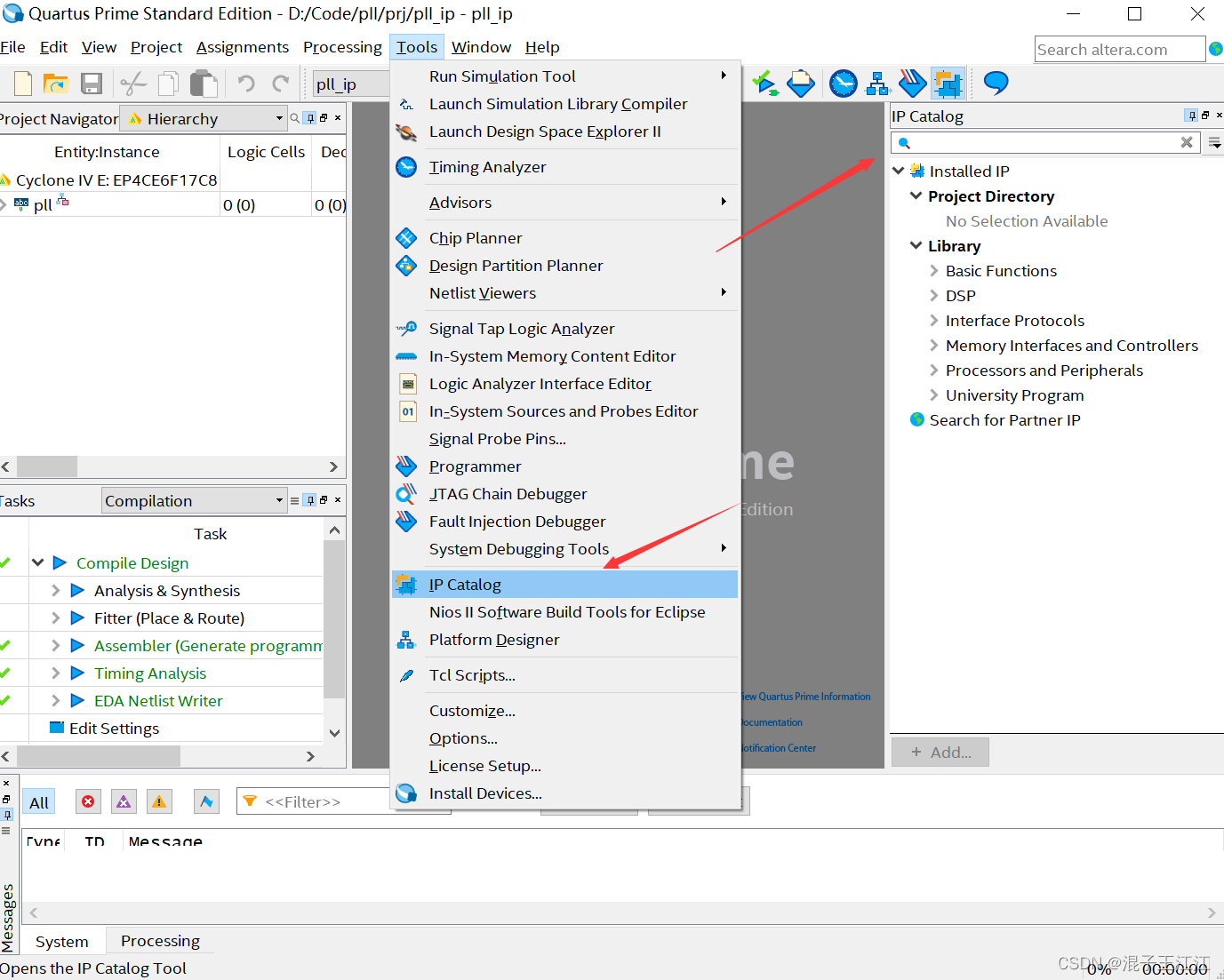

- 选择IP核:

- 搜索IP核并双击点击进行配置:

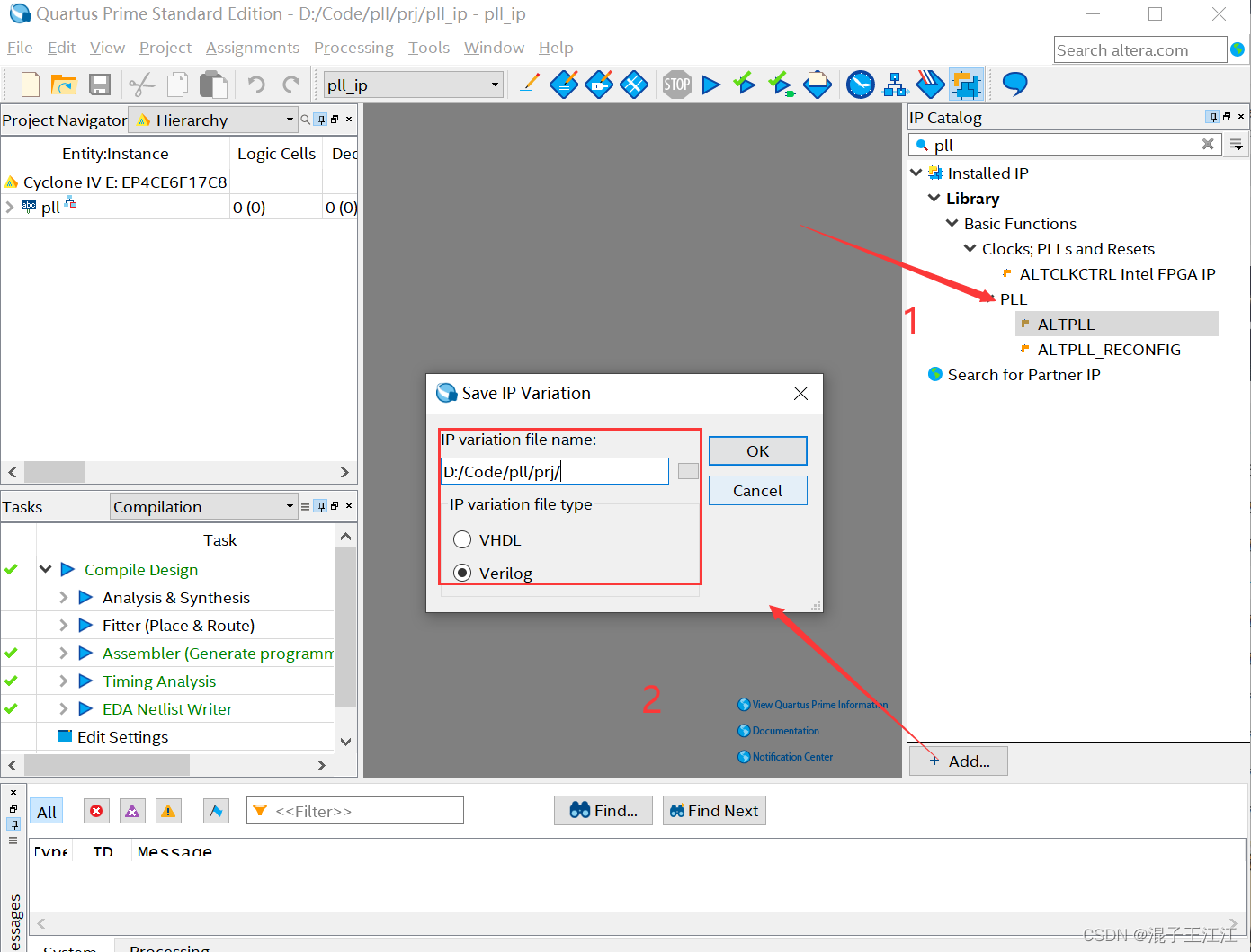

- 设置IP核存放位置

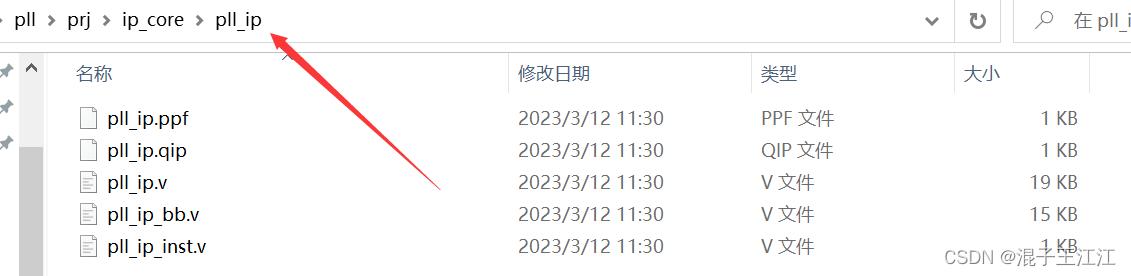

在prj文件夹下新建ip_core文件夹用于存放IP文件,在之下又新建子文件pll_ip用于存放我们的目标ip。

-

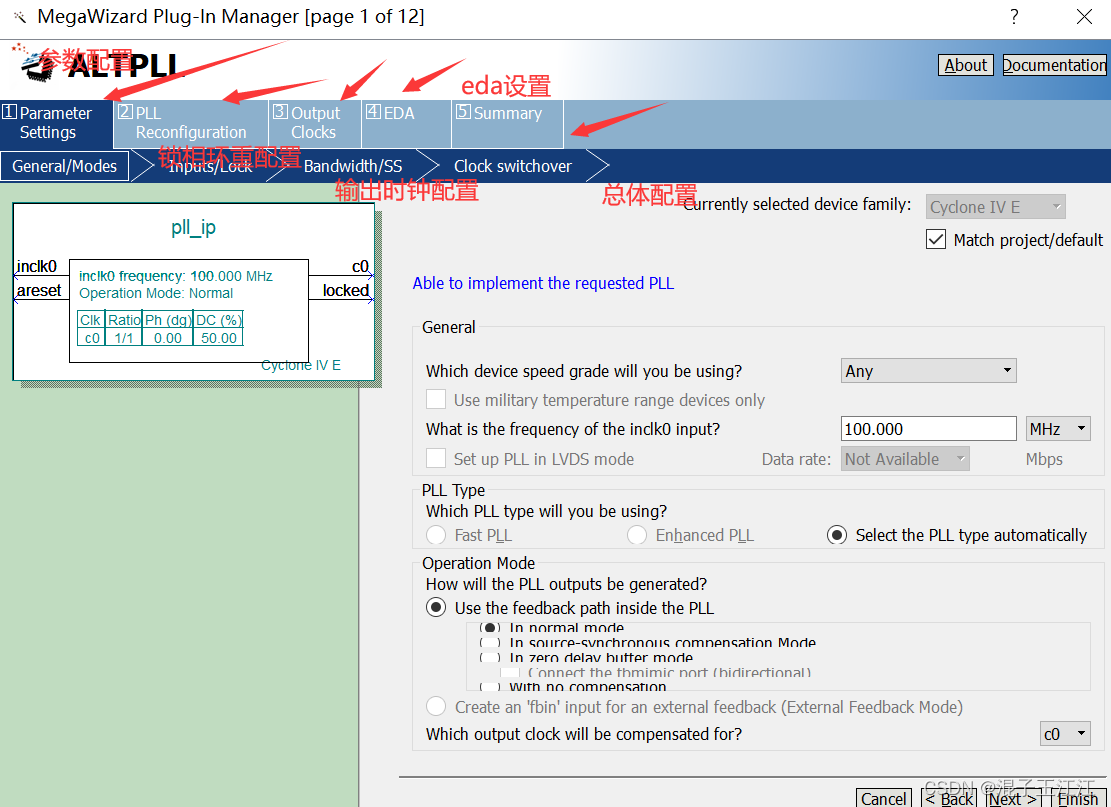

弹出设置界面:

-

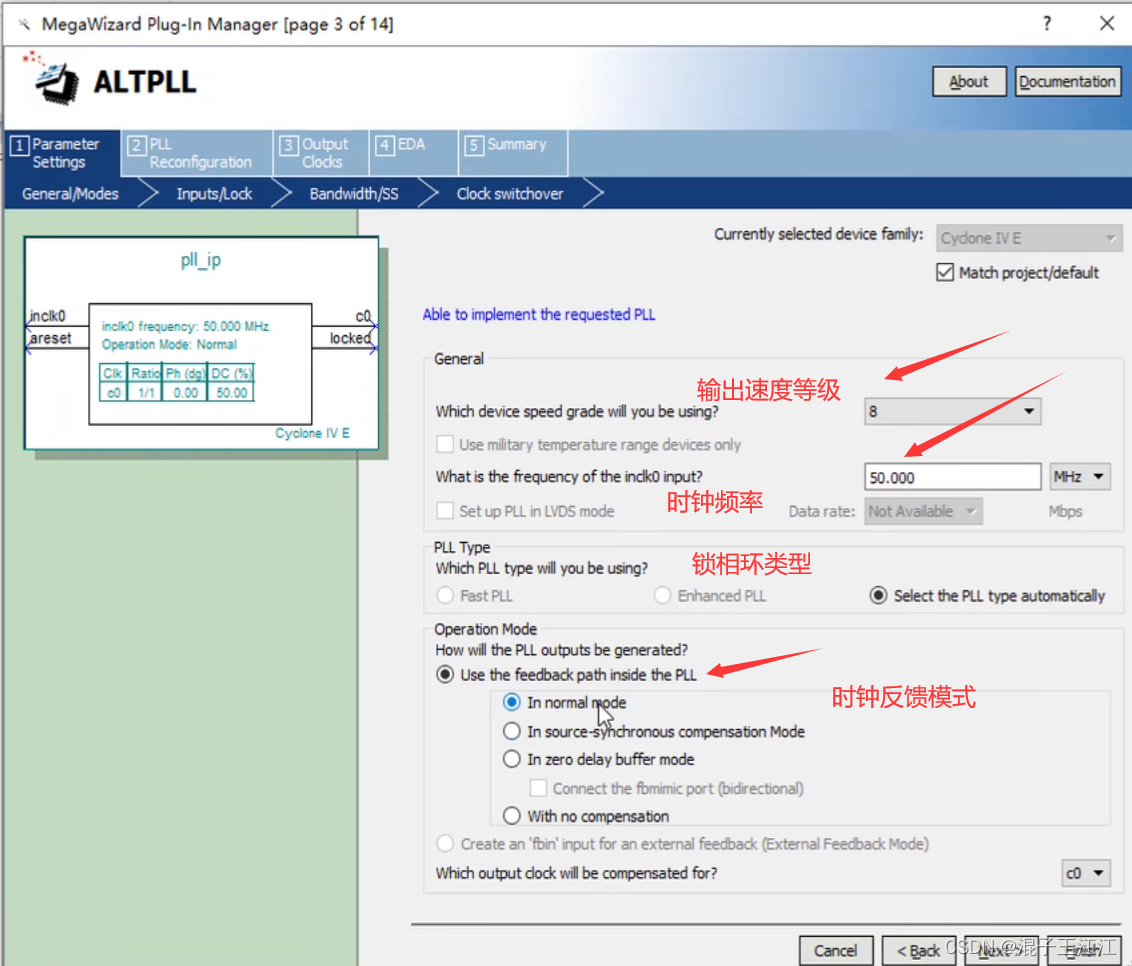

参数配置:

这里的时钟反馈模式有:

1、源同步模式

2、无补偿模式

3、标准模式

4、零延迟缓冲模式

5、确定性延迟补偿模式

Altera PLL IP核四种工作模式介绍

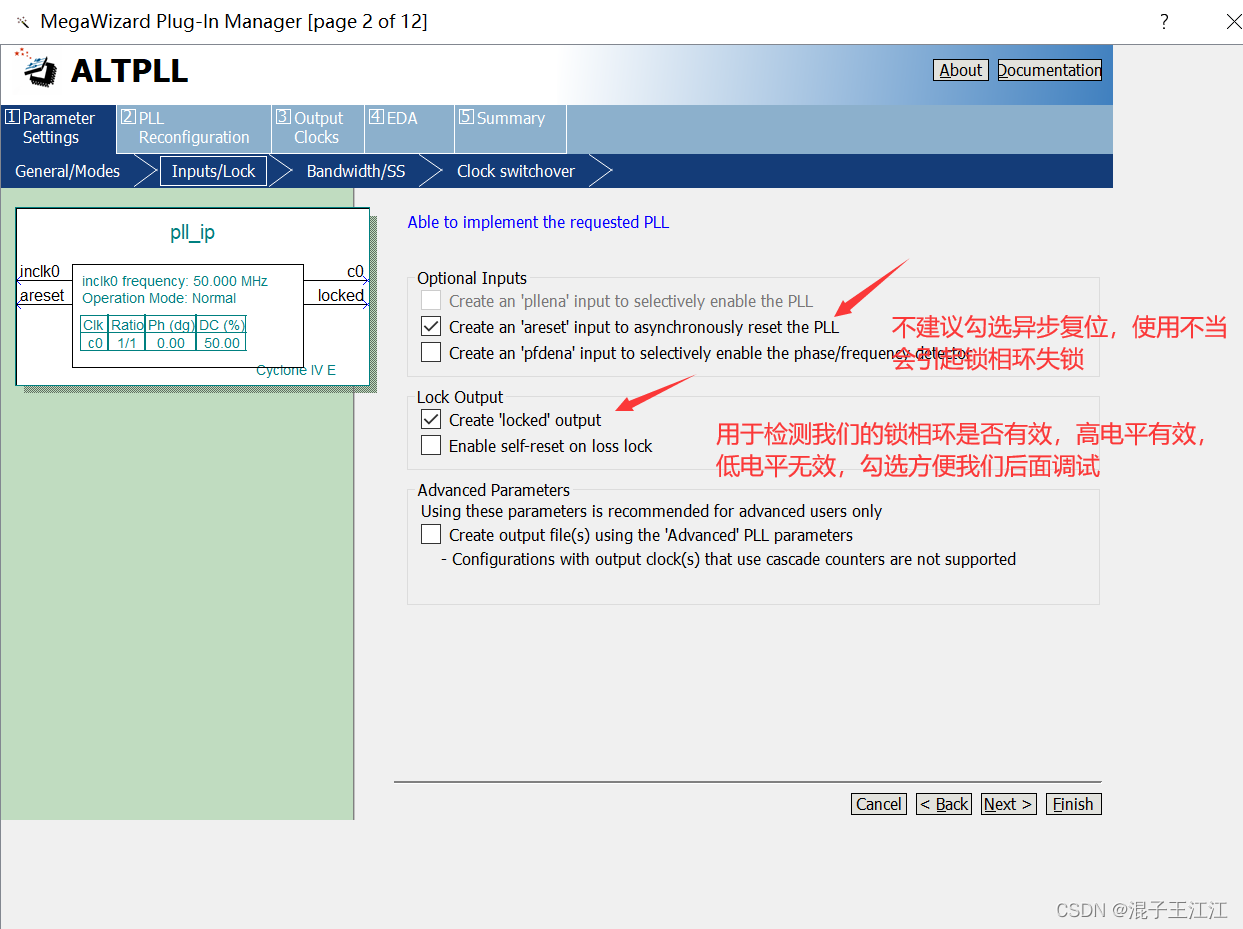

- 点击next:

- 继续next:

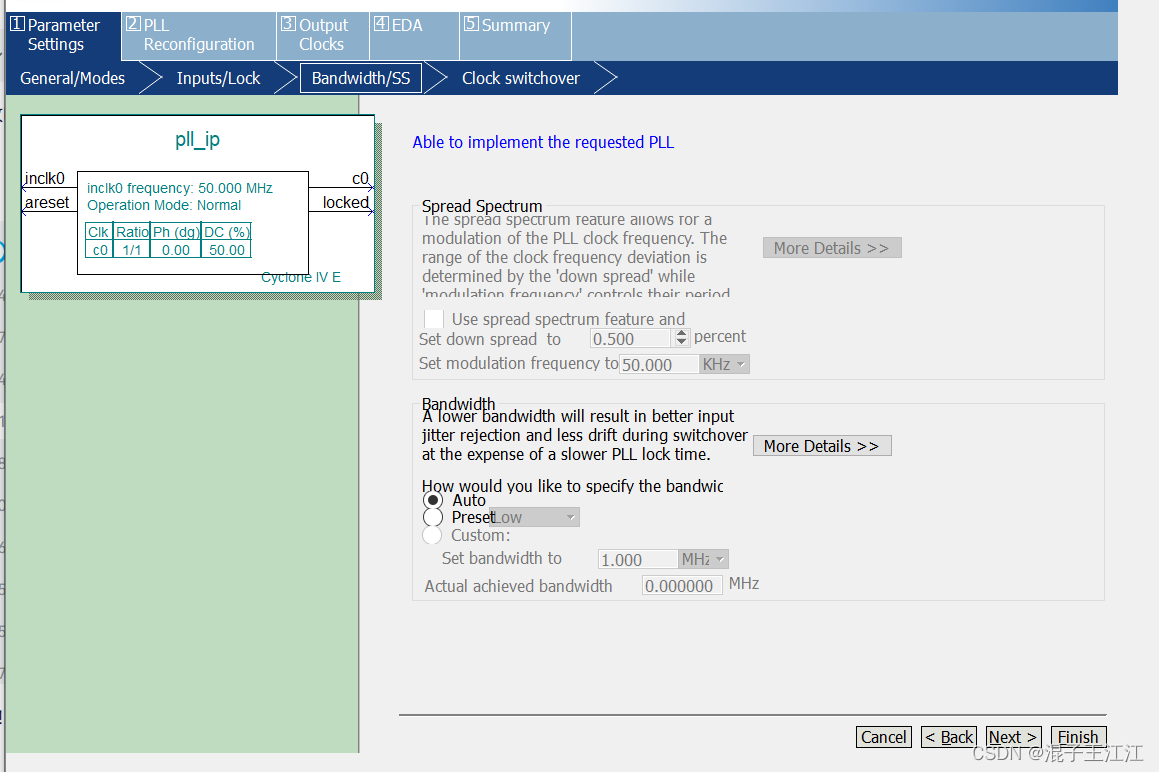

这个界面主要是拓展频谱时钟和带宽可编程功能,属于锁相环高级特性,我们先不进行操作。

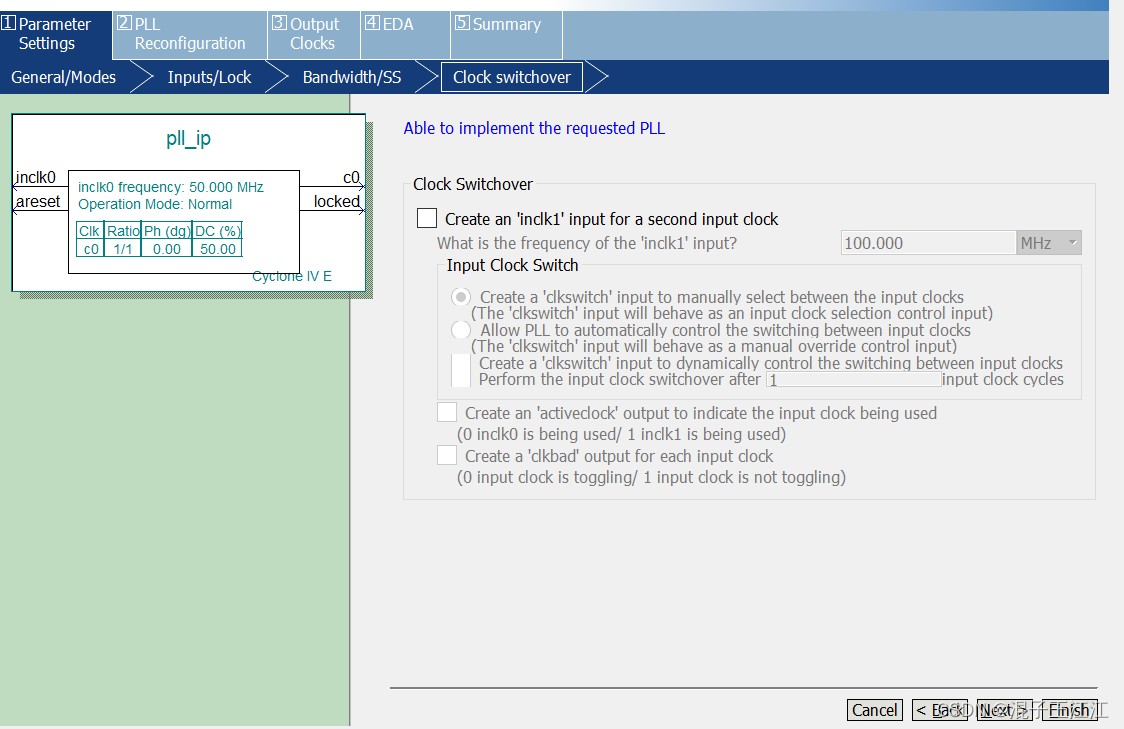

- 继续next:

这里也是高级属性,不进行使用。

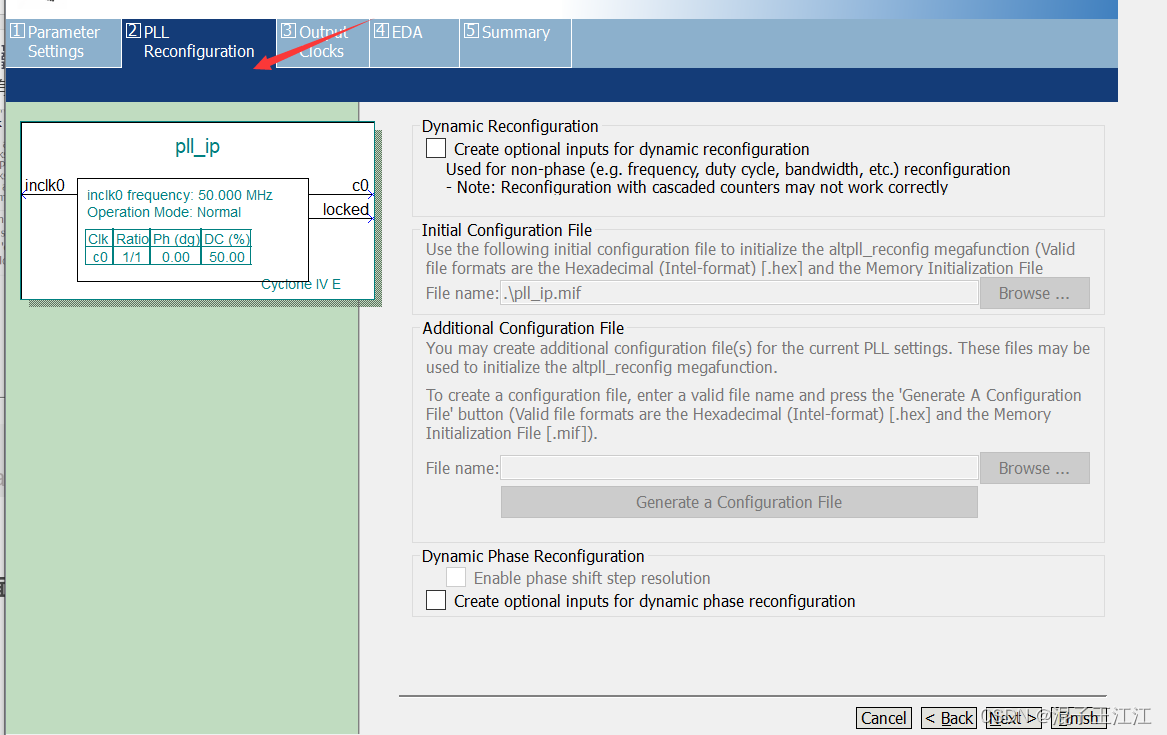

- 继续next,进入第二个设置界面:

这个界面是锁相环的重配置,主要用于锁相环动态重配置和动态相位重配置,也属于高级属性,我们不能进行使用,选择默认。

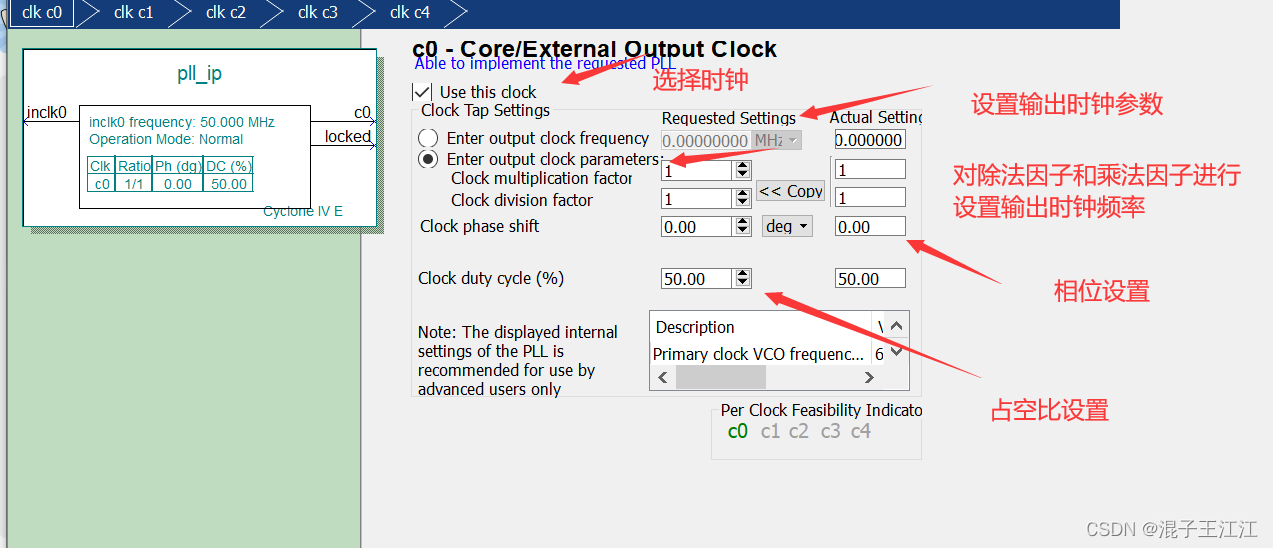

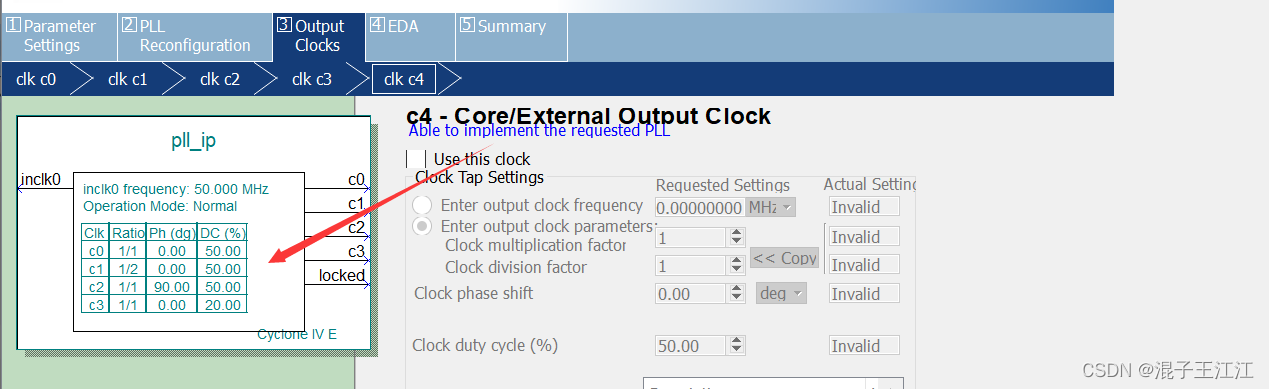

- 继续next来到输出时钟的设置:

每个锁相环可以输出五个时钟,对应下面有五个子选项。

- 下面是设置完的参数:

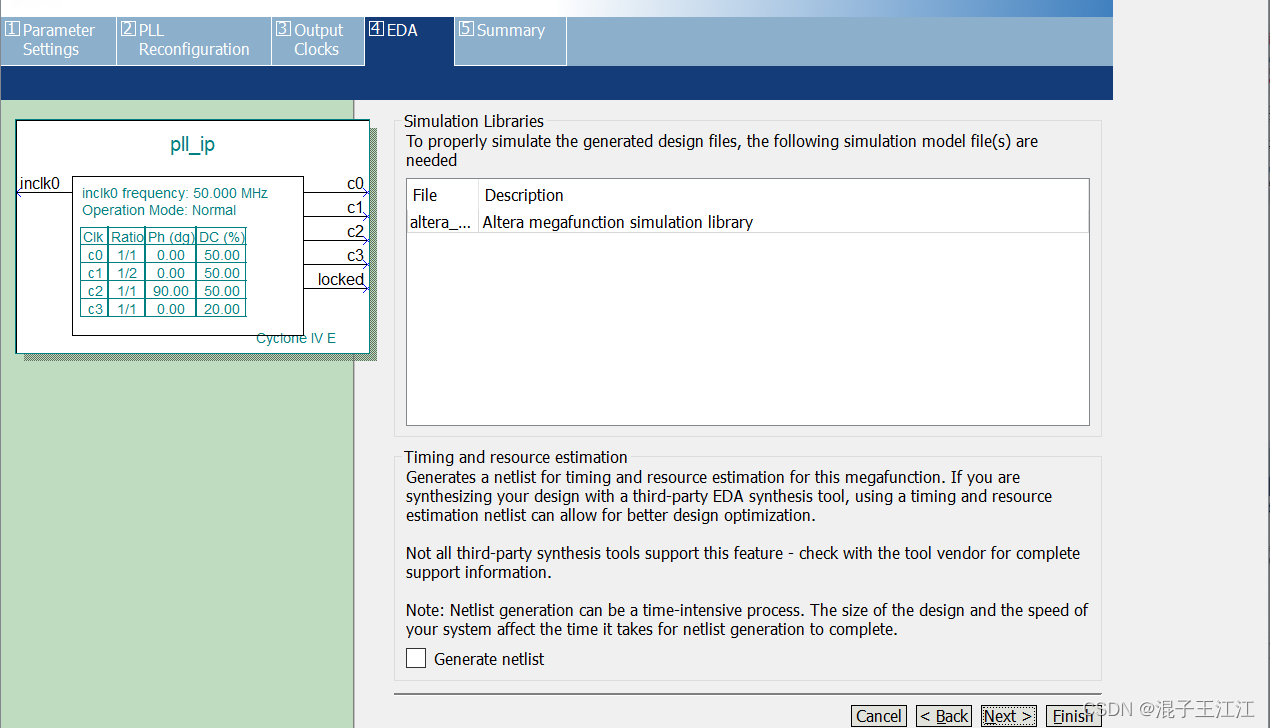

- 继续next进入eda设置界面:

这里没有我们需要设置的界面,继续next。

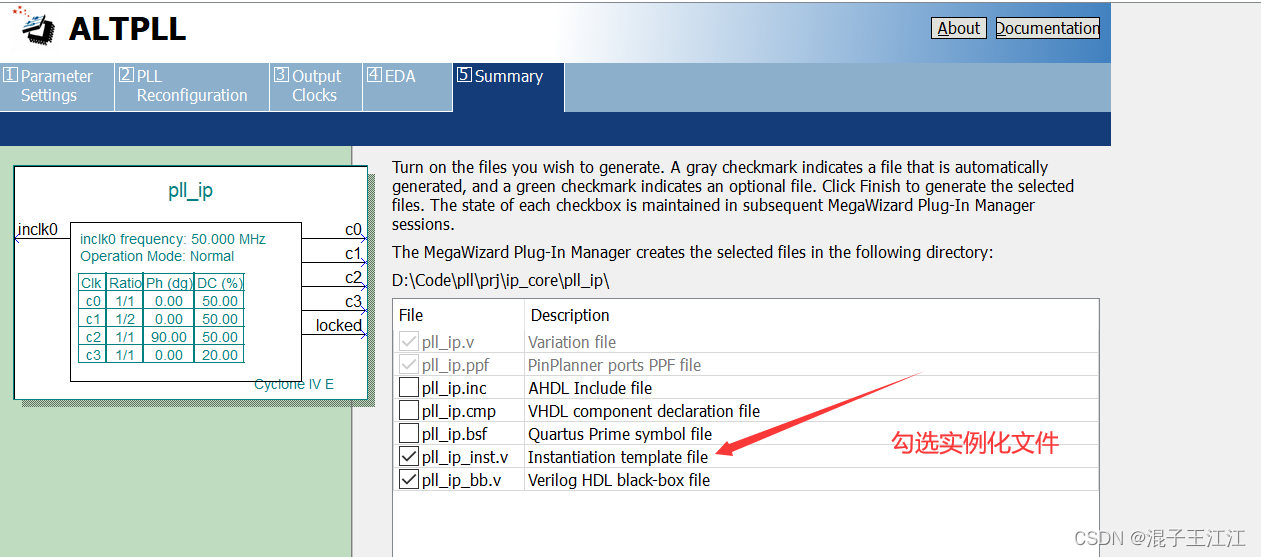

- Summary设置界面:

点击finish,完成配置。

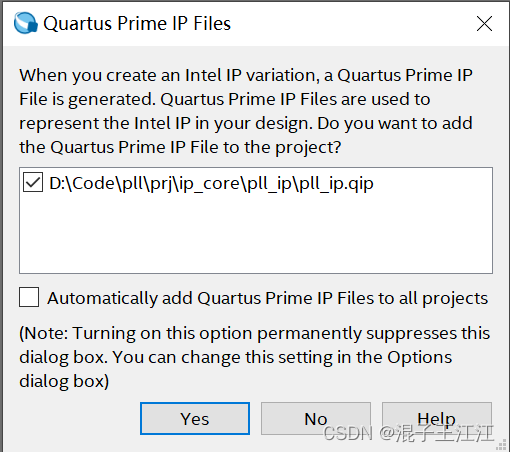

选择yes,完成ip核的设置。

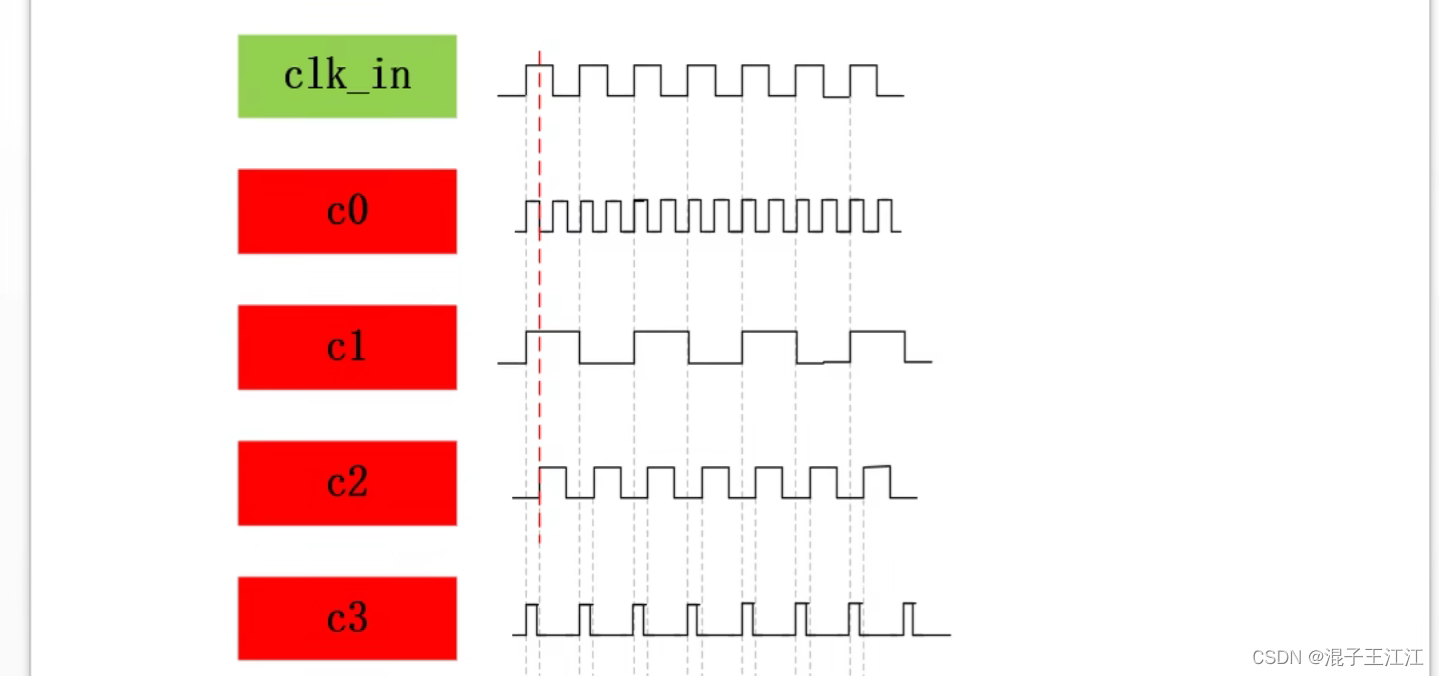

- 绘制波形图:

- 查看pll_ip文件夹下是否生成ip文件:

3、PLL-IP核调用

- 查看ip核的实例化文件(pll_ip_inst):

pll_ip pll_ip_inst (

.inclk0 ( inclk0_sig ),

.c0 ( c0_sig ),

.c1 ( c1_sig ),

.c2 ( c2_sig ),

.c3 ( c3_sig ),

.locked ( locked_sig )

);

- 编写顶层文件:

module pll (

input wire sys_clk,

output wire clk_mul_2,

output wire clk_div,

output wire clk_pha_90,

output wire clk_duc_20,

output wire locked

);

pll_ip pll_ip_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div ),

.c2 ( clk_pha_90 ),

.c3 ( clk_duc_20 ),

.locked ( locked )

);

endmodule

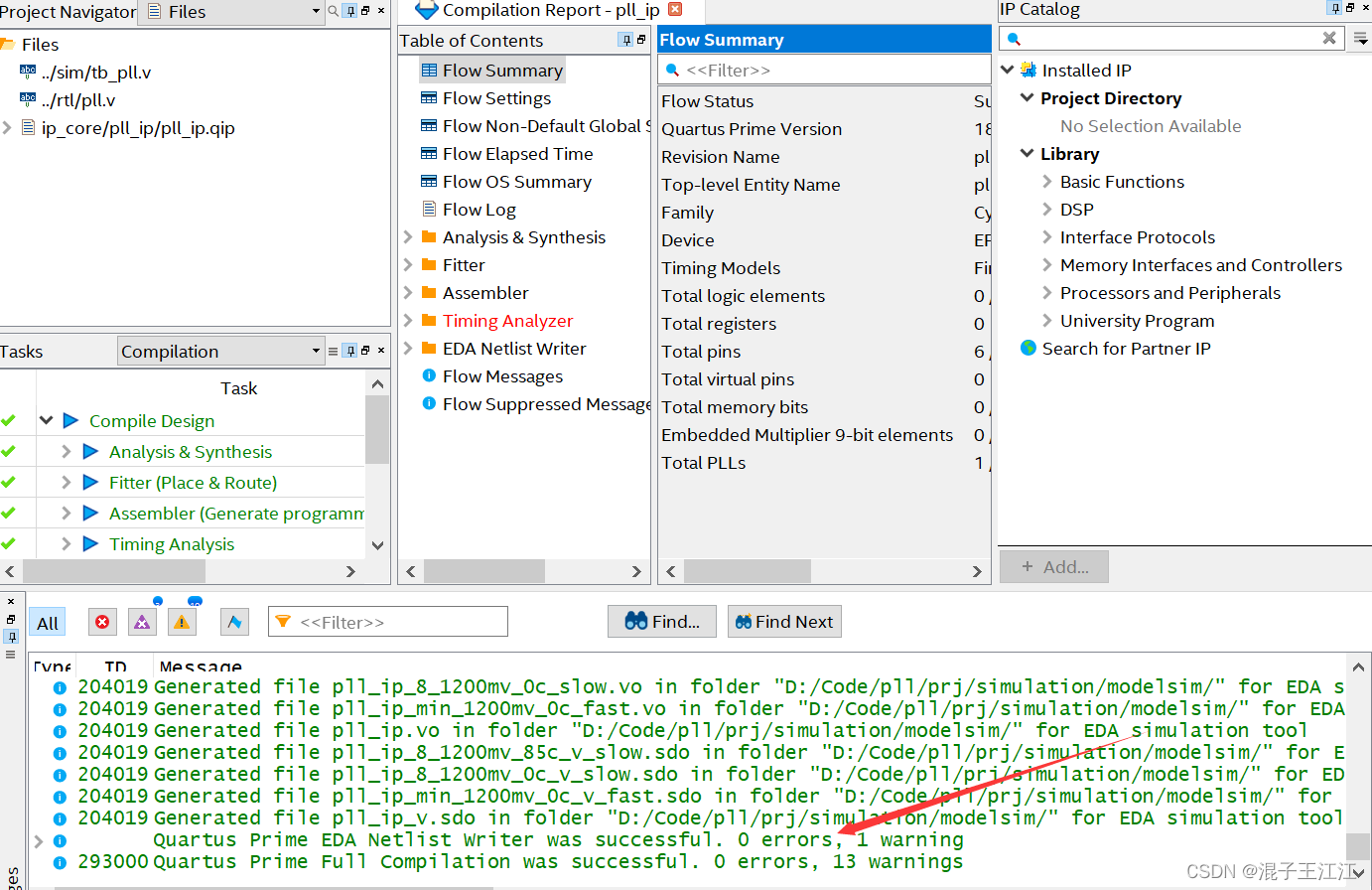

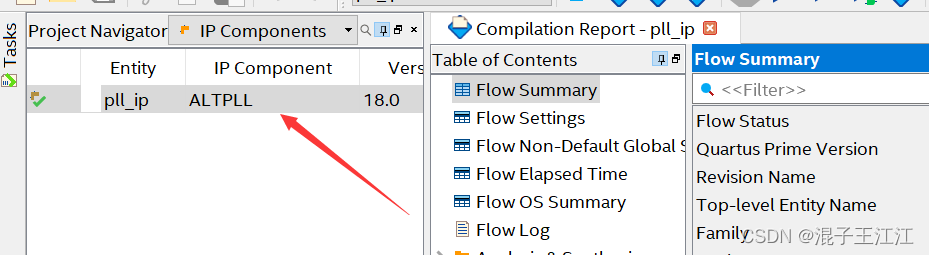

- 引入顶层文件后进行全编译:

编译通过。

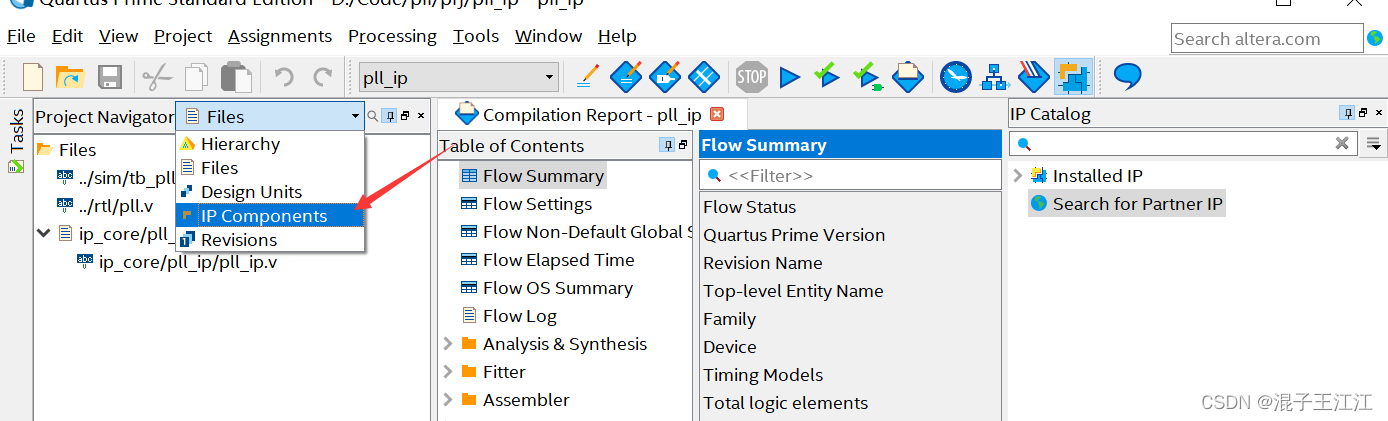

- 补充:临时想对ip核进行重新的设置:

勾选IP_Component

双击进行修改:

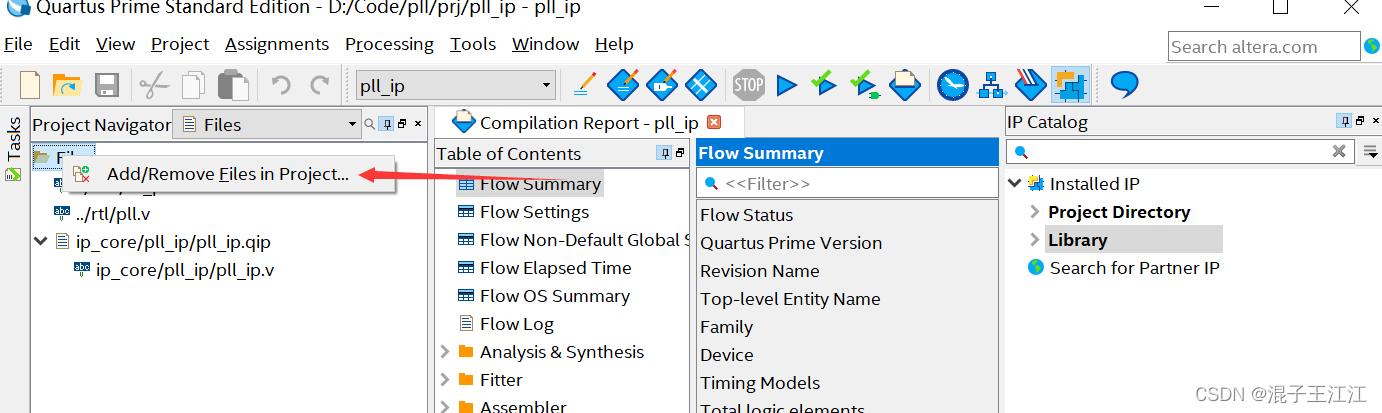

- 不小心把IP核文件删除:

右击将文件进行添加即可

4、PLL-IP仿真

- 仿真文件:

`timescale 1ns/1ns

module tb_pll();

reg sys_clk;

wire clk_mul_2;

wire clk_div;

wire clk_pha_90;

wire clk_duc_20;

wire locked;

initial begin

sys_clk=1'b1;

end

always #10 sys_clk=~sys_clk;

pll pll_inst(

.sys_clk (sys_clk),

.clk_mul_2 (clk_mul_2),

.clk_div (clk_div),

.clk_pha_90 (clk_pha_90),

.clk_duc_20 (clk_duc_20),

.locked (locked)

);

endmodule

将仿真文件添加,然后进行全编译,然后进行仿真设置(忽略),接着就是仿真。

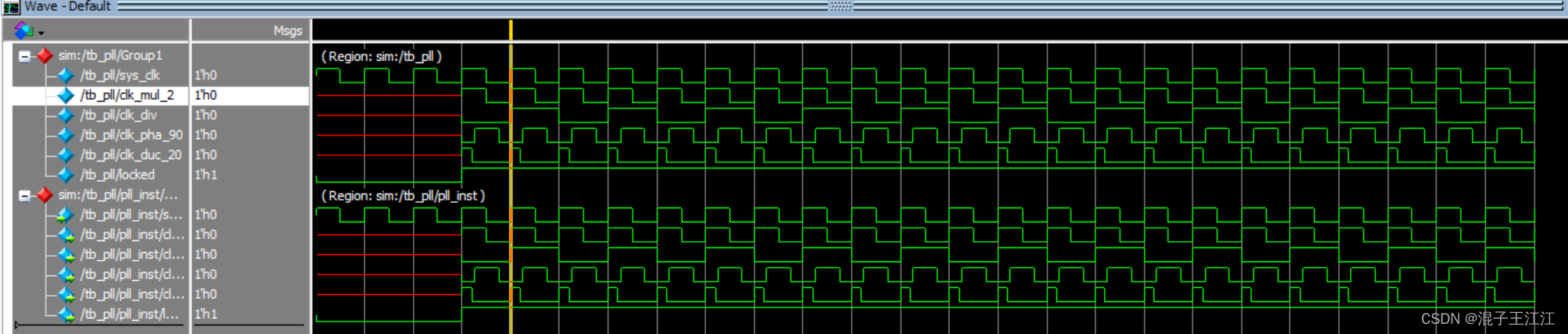

- 仿真波形图:

仔细对照绘制的波形图或查看波形图的频率、相位以及占空比与设置的一致,仿真通过。

三、总结

这篇文章主要介绍了IP核以及它的一些用法,此外了解了PLL (Phase Locked Loop,即锁相环)是最常用的IP核之一,可以通过PLL_IP获得期望的时钟。后续会继续更新其他IP核的内容。