一、基础知识

1.1了解IP核

- IP核介绍:如果你写过简单的51程序,那么IP核就相当于调试好的模块化程序,只要平台合适就可以直接使用的,只不过IP核是硬件而已。VHDL、verilog不是程序,是硬件描述语言。(此段来源于网络,通俗易懂)<另详细介绍>

- 7系列的FPGA使用了专用的全局(Global)和区域(Regional)时钟资源来管理和设计不同的时钟需求。

Clock Management Tiles(CMT)提供了时钟合成(Clock frequency synthesis),倾斜矫正(deskew),过滤抖动(jitter filtering)功能。 - 1个CMT包含1个MMCM和1个PLL。

- BUFG:全局时钟缓冲器(可以到时钟区域的任何地方)

BUFH:水平时钟缓冲器(通过HROW在左右相邻时钟区域内工作)

BUFIO:iO时钟缓冲器(只能作用IO)

BUFR:区域时钟缓冲器(只能作用本区域)

BUFMR:多区域时钟缓冲器(不仅可以在本区域还可以通过CMT backbone作用于相邻时钟区域)

MMCM:混合模式时钟管理器

PXLL:锁相环 - PLL和MMCM可以消除延时,消除抖动,产生不同频率时钟

- CC是时钟专用引脚

- MMCM比PLL功能多。

1.2硬件配置

二、程序

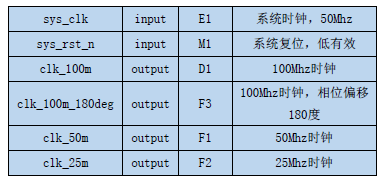

module ip_clk_wiz(

input sys_clk,

input sys_rst_n,

output clk_100m,

output clk_100m_180deg,

output clk_50m,

output clk_25m

);

wire locked;

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1_100m(clk_100m), // output clk_out1_100

.clk_out2_100m_180(clk_100m_180deg), // output clk_out2_100_180

.clk_out3_50m(clk_50m), // output clk_out3_50

.clk_out4_25m(clk_25m), // output clk_out4_25

// Status and control signals

.reset(~sys_rst_n), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(sys_clk)); // input clk_in1

endmodule

三、总结

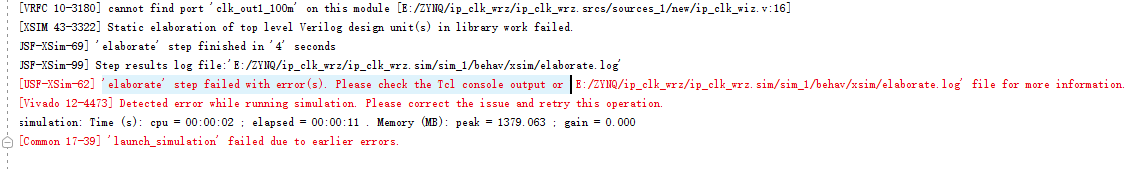

- 程序有错误,待解决