0 本章目录

1)软件环境

2)PLL IP核仿真流程

3)结束语

1 软件环境

1)vivado 2016.1

2)modelsim10.4c

2 PLL IP核仿真流程

PLL IP核仿真流程如下:

1)vivado 关联modelsim仿真软件;

2)PLL IP核配置;IP配置,输入时钟clk_in1为100MHz,输出时钟clk_out1为50MHz, clk_out1为100MHz。

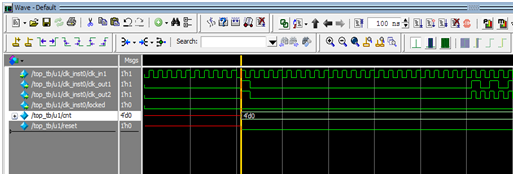

3)仿真刚开始时,两个输出时钟会产生一个时钟周期的电平如图1所示。

图1 仿真毛刺

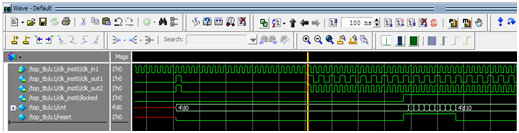

4)接着仿真,产生输出时钟且locked信号为低,代表这时产生的输出时钟不稳定还不能用它去驱动其他逻辑如图2所示。

图2 仿真截图

5)只有当locked信号为高时,输出时钟才会稳定,可以用它去驱动其他逻辑如图3所示。

图3 仿真截图