一,RapidIO被定义为三层架构层次结构。

•逻辑层:指定端点处理事务所需的协议,包括数据包格式。

•传输层:定义寻址方案以在系统内正确路由信息包。

•物理层:包含设备级接口信息,例如电气特性,错误管理数据和基本流量控制数据。

1,逻辑层协议

逻辑层定义了操作协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息传递(Message Passing)。

直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。从功能上讲,这一特点和德州仪器DSP的传统的主机接口(HPI, Host Port Interface)类似。但和HPI口相比,SRIO(Serial RapidIO)带宽大,管脚少,传输方式更灵活。

对上层应用来说,发起直接IO/DMA传输主要需提供以下参数:目地器件ID、数据长度、数据在目地器件存储器中的地址。

直接IO/DMA模式又可进一步分为以下几种传输格式:

(1) NWRITE: 写操作,不要求接收端响应。

(2)NWRITE_R: 带响应的NWRITE(NWRITE with Response),要求接收端响应。

(3)SWRITE:流写(Stream Write),数据长度必须是8字节的整数倍,不要求接收端响应。

(4)NREAD: 读操作。

SWRITE是最高效的传输格式;带响应的写操作或读操作效率则较低,一般只能达到不带响应的传输的效率的一半。

消息传递(Message Passing)模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。

对上层应用来说,发起消息传递主要需提供以下参数:目地器件ID、数据长度、邮箱号。

2,传输层协议

RapidIO是基于包交换的互连技术,传输层定义了包交换的路由和寻址机制。

RapidIO网络主要由两种器件,终端器件(End Point)和交换器件(Switch)组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。RapidIO支持8 bits 或 16 bits器件ID,因此一个RapidIO网络最多可容纳256或65536个终端器件。与以太网类似,RapidIO也支持广播或组播,每个终端器件除了独有的器件ID外,还可配置广播或组播ID。交换器件根据包的目地器件ID进行包的转发,交换器件本身没有器件ID。

RapidIO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。

3,物理层接口协议

8/16 LP-LVDS规范是点对点同步时钟源DDR接口

1x / 4x LP-Serial规范是一种点对点交流耦合时钟恢复接口。(SerDes 串行器/解码器技术)

RapidIO物理层1x / 4x LP-Serial规范目前涵盖四个频率点:1.25,2.5,3.125和5 Gbps。这定义了每个差分对I / O信号的总带宽。一个8位/ 10位编码方案确保时钟恢复电路有足够的数据转换。由于8位/ 10位编码开销,每个差分对的有效数据带宽分别为1.0,2.0,2.5和4 Gbps。串行RapidIO仅为1x和4x端口指定这些速率。1x端口定义为一个TX和一个RX差分对。4x端口是这些对中的四个的组合。本文档描述了一个4x RapidIO端口,也可以配置为4个1x端口;这提供了一个可扩展的接口,能够支持1到16 Gbps的数据带宽。

二,SRIO 功能支持

符合LP-Serial规范REV2.1.1

•具有4X Serial RapidIO

- 1X端口,(4)1X端口的可选操作

- 2X端口,(2)2X端口的可选操作

- 2X端口和1X端口操作,(1)2X端口和(2)1X端口的可选操作

- 4个端口,操作(1)4x端口

•采用TI SerDes的集成时钟恢复 ?

•能够以不同的波特率运行不同的端口(仅支持整数倍速率:支持2.5G和5G,不支持3.125G和5G)

•硬件错误处理,包括CRC

•支持AC和DC耦合的差分CML信号

•支持1.25,2.5,3.125和5 Gbps速率

•未使用端口的Powerdown选项

•读取,写入,写入响应,流式写入,外出的Atomic,维护操作 //Atomic??

•CPU的中断生成(Doorbell数据包和内部调度)

•支持8b和16b设备ID

•支持接收34b地址

•支持生成34b,50b和66b地址

•支持数据大小:字节,半字,字,双字

•定义为Big Endian

•直接IO传输

•消息传递传输

•数据有效负载为256B

•单个消息生成最多16个数据包

•用于时钟域切换的弹性存储FIFO

•符合短期运行和长期运行

•支持错误管理扩展

•支持拥塞控制扩展

•支持多播ID

•支持短控制符号和长控制符号

•支持IDLE1序列,最大波特率为5 Gbps

•基于优先级和CRF,跨协议单元进行严格的优先级段交织

以下功能不支持

•符合全球共享内存规范(GSM)

•兼容8/16 LP-LVDS

•RapidIO原子操作的目标支持

三,SRIO IP核配置

1,basic

2,logic layer

3,IO

4,buffer layer

5,logical registers

6,physical registers

四,SRIO IP核例化

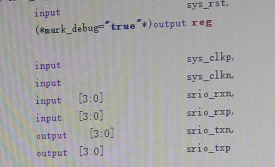

输入输出: