文章目录

前言

在我们进行FPGA项目设计中,简单的工程我们可以自己手动去设计与编写,但是如果工程较为复杂,我们完全自己去设计编写的话效率就太低了。所以在进行FPGA设计当中,常常会用到IP核,IP核也就是知识产权核或知识产权模块,是将一些特定的功能封装成一些可以根据需求进行修改的模块,来减轻FPGA工程师的负担和提高工作效率。

利用IP核设计电子系统,引用方便,修改基本原件的功能简单,正是由于这些优点,IP核在数字电路设计中的地位也越来越高。

本文就基于Quartus II 软件简单的讲解一下FPGA设计中常用到的IP核,以锁相环(PLL)为例。

1、PLL简介

PLL(锁相环)的英文全称是Phase Locked Loop,是最常用的IP核之一,其性能十分强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输入需要的时钟信号。

对于一些简单的设计来说,FPGA整个系统使用一个时钟或者通过编写代码的方式来对时钟进行分频处理是可以完成的;但是对于复杂的设计来说,系统中往往需要用到多个不同频率、占空比、相位的时钟,并且编写代码不能够对时钟进行倍频处理,这时候我们利用PLL IP核进行设计,不仅可以节约芯片资源,减少开发者的工作量,还会得到稳定的时钟,保证设计的正确性。

即使在实际应用中我们不需要对输入的时钟信号进行处理,我们仍然可以使用PLL IP核,这是因为PLL IP核会对输入时钟进行优化处理,让输出时钟信号的抖动更小,更加稳定。

2、PLL工作原理

PLL的工作原理其实就是一个反馈系统,输出的信号会反馈回来与输入信号进行对比判断。PLL主要由以下几个部分组成:分频计数器、鉴频鉴相器、环路滤波器以及压控振荡器。

首先,输入到PLL中的时钟是一个参考时钟(clk),这个参考时钟经过分频计数器之后输入到鉴频鉴相器(FD/PD,FD表示鉴频,PD表示鉴相);其中,输入到鉴频鉴相器内的时钟除了参考时钟,还有一个比较时钟(反馈回来的时钟),鉴频鉴相器的作用就是对比参考时钟和反馈时钟两者的频率和相位差异;如果参考时钟和反馈时钟的频率相等,则鉴频鉴相器会输出0;如果参考时钟的频率大于反馈时钟的频率,则会输出一个较大的成正比的值;如果参考时钟频率小于反馈时钟频率,则会输出一个较小的成正比的值。鉴频鉴相器输出的值会输入到环路滤波器(LF),环路滤波器的作用就是过滤掉高频噪声,使输出的波形更加平滑,同时环路滤波器会根据输入值的不同而输出不同电伏值的信号,这个电压值会传到压控振荡器(VCO),压控振荡器的特点就是输入的电压值越高,输出信号的频率也就越高,最后就可以得到锁相环输出信号的频率了。

3、PLL实验

这里我们就来通过Quartus II这个EDA工具来做一个简单的PLL IP核的调用实验,实验包括时钟分频、倍频以及相位偏移等等。

3.1、PLL的调用

在开始PLL调用之前呢,我们需要建立一个Quartus工程(包括工程命名,器件选择等),然后在建立的工程中调用PLL的IP核,下面我们就来一起配置一个PLL IP核。

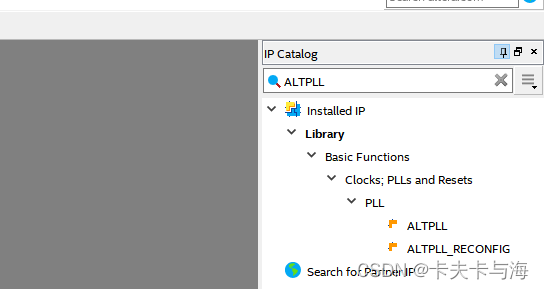

1、在Quartus II界面的右上角搜索ALTPLL,然后就会弹出PLL的IP核了。这里我用的是Quartus II18.1,不同版本的Quartus工具可能不一样。

2、然后双击ALTPLL选项卡,进入IP核的命名和保存界面;这里建议在工程文件夹下新建立一个文件夹来保存IP核,还要打上IP核的标签,不然进行大型设计的时候会用到多个IP核,每一个IP核对应一个文件夹,这样分类管理就不会把自己给弄糊涂。

3、现在就正式进入IP核的配置界面了,输入时钟频率:默认100MHZ,我们这里输入时钟为50MHZ;其他的默认即可。然后点击NEXT。

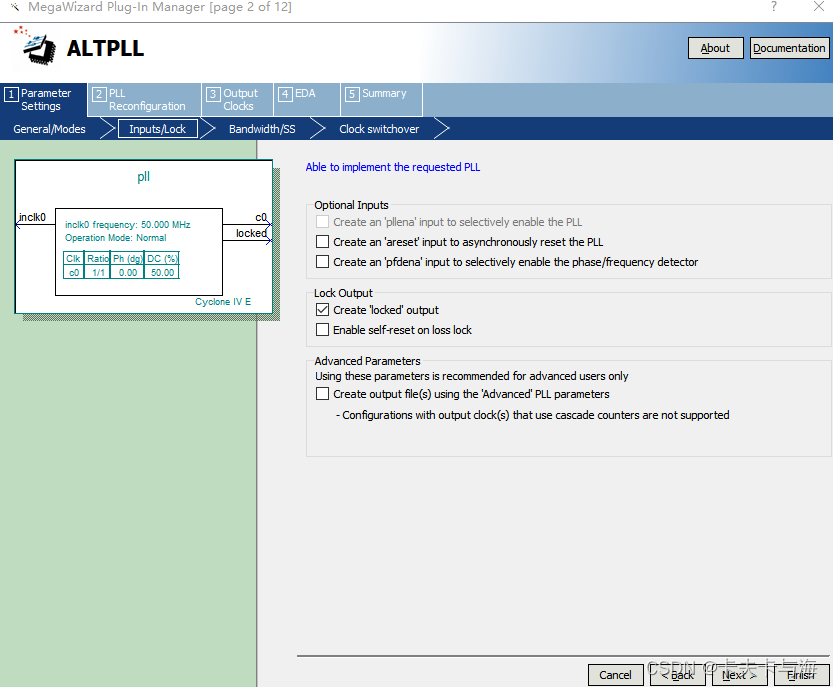

4、锁相环配置界面,取消勾选异步复位(areset),其余默认即可,点击NEXT。

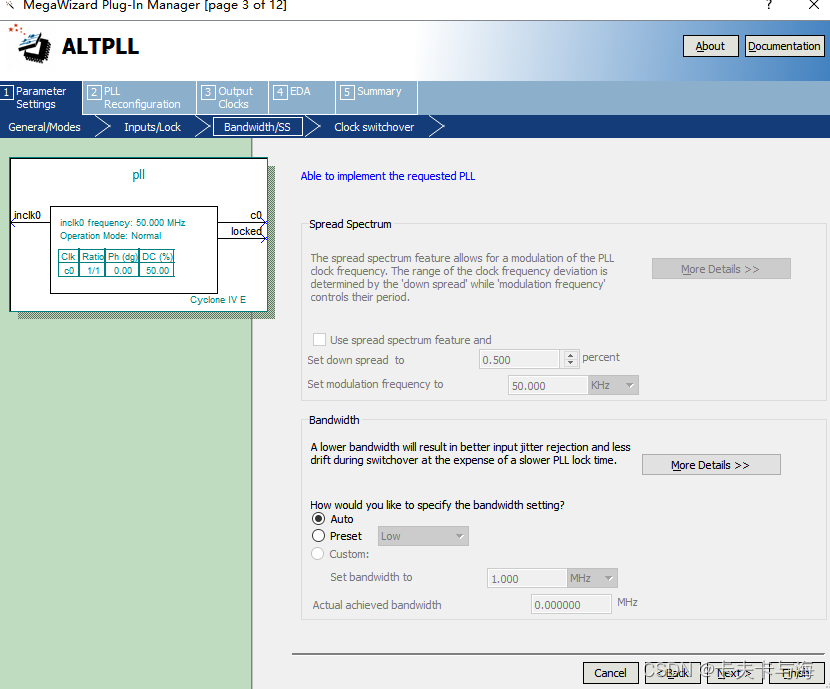

5、这里是配置一些锁相环的高级功能,这里不使用,点击NEXT。

6、这个界面是配置时钟切换,也是一个高级属性,这里用不上,点击NEXT。

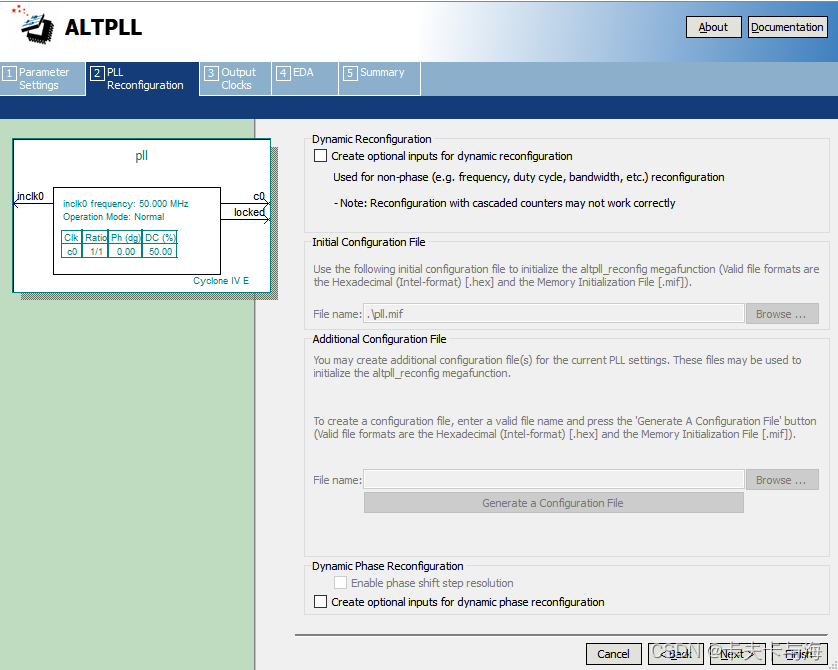

7、这个界面是锁相环的重配置,直接点击NEXT。

8、然后就进入了输出时钟配置,这里一个锁相环可以输出5个时钟,对应下面的5个配置选项卡,可根据需要进行配置。

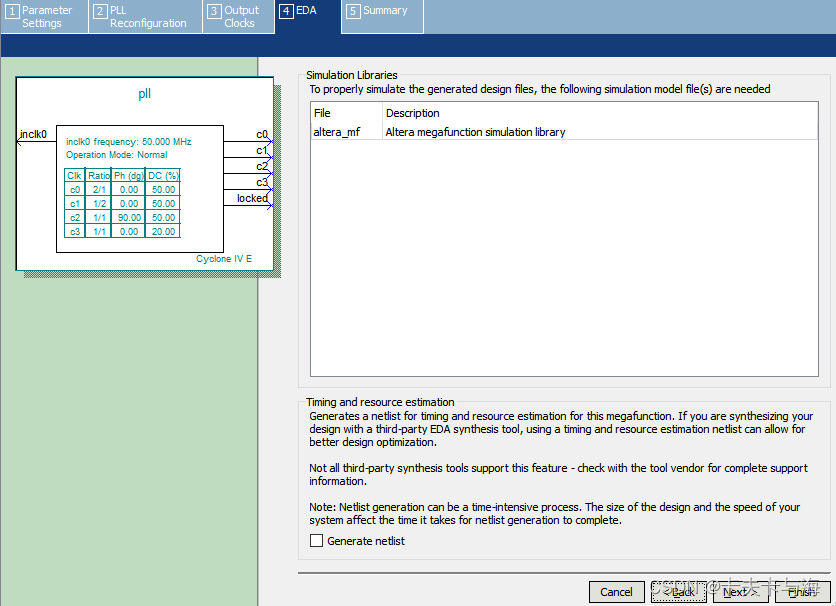

9、然后就是进入EDA参数设置,这里不需要做处理,直接NEXT。

9、然后就是进入EDA参数设置,这里不需要做处理,直接NEXT。

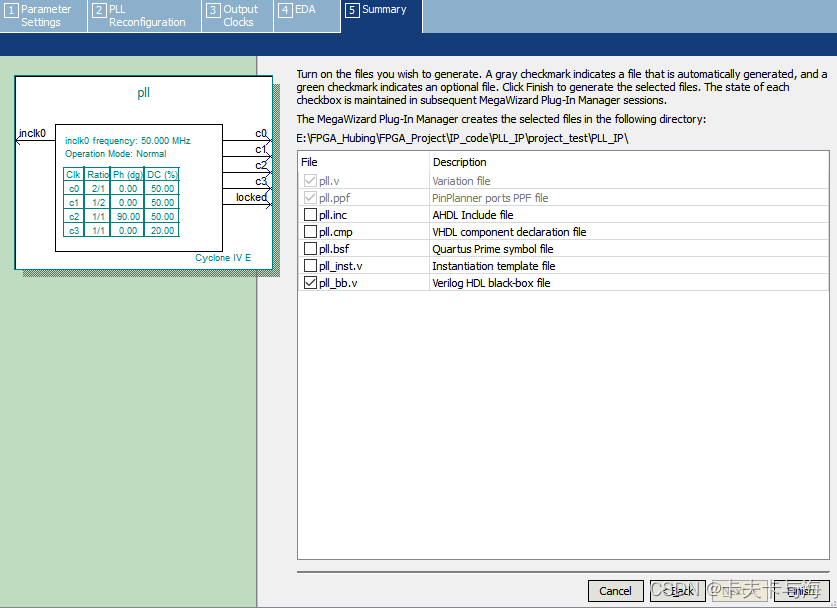

10、最后就是总体设置了,这里我们勾选_bb.v选项,这是生成例化文件,最后Finish。

到这里我们的锁相环IP核配置就完成了,接下来我们就写一个顶层文件,将IP核例化进去,通过仿真来验证我们的配置是否正确。

3.2、程序与仿真

程序代码:

/*========================================*

filename : pll_top.v

description : 锁相环配置实验

time : 2022-12-19

author : 卡夫卡与海

*========================================*/

module pll_top(

input clk ,

output clk_0 ,

output clk_1 ,

output clk_2 ,

output clk_3 ,

output locked

);

//例化IP核

pll_ip pll_ip_inst (

.inclk0 (clk ),

.c0 (clk_0 ),

.c1 (clk_1 ),

.c2 (clk_2 ),

.c3 (clk_3 ),

.locked (locked)

);

endmodule`timescale 1ns/1ns

/*========================================*

filename : pll_top_tb.v

description : 锁相环配置仿真文件

time : 2022-12-19

author : 卡夫卡与海

*========================================*/

module pll_top_tb();

reg clk ;

wire clk_0 ;

wire clk_1 ;

wire clk_2 ;

wire clk_3 ;

wire locked ;

initial clk = 1'b1;

always #10 clk = ~clk;

pll_top u_pll_top(

/*input */.clk (clk ),

/*output */.clk_0 (clk_0 ),

/*output */.clk_1 (clk_1 ),

/*output */.clk_2 (clk_2 ),

/*output */.clk_3 (clk_3 ),

/*output */.locked (locked)

);

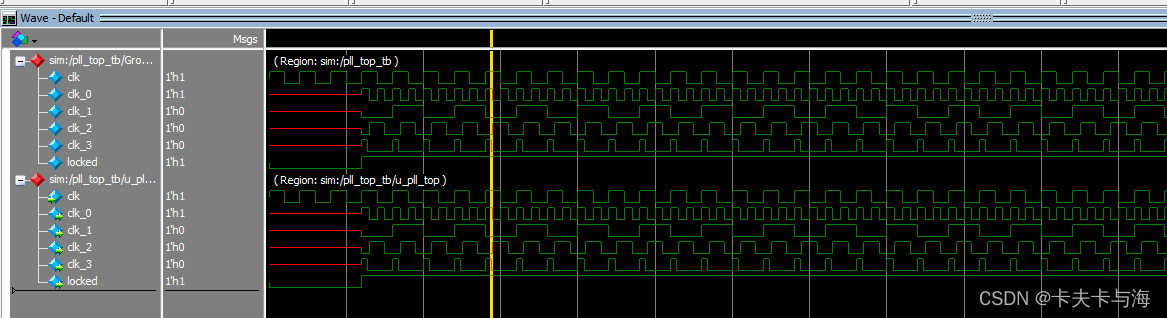

endmodule仿真波形图:

由仿真波形可以看出,这里的C0的频率是100MHZ,C1的频率是25MHZ,C2的频率是50MHZ,相位偏移90°,C3的频率是50MHZ,20%占空比。由此说明我们的IP核调用成功,输出的时钟频率,相位偏移以及占空比与预期一样。

总结

IP核的调用都是大同小异的,主要是要明白不同IP核的配置不同,如果是存储器类型的IP核还会有宽度和深度的配置,这些需要大家以后慢慢地熟悉。学会运用IP核进行FPGA的开发,不仅会使开发效率加快,还会使设计的项目的bug减少,这无疑是一个值得我们学习的点。

还有值得注意的是,不同的EDA工具的IP核的配置可能会存在差异,但是功能都是差不多的,只是可能会有一些特定的配置罢了。对于IP核的调用想要全面掌握,建议去看看官方文档,那里面介绍得已经很详细了,我这里只是简单提及一下罢了!!!