1 算法简述

OSTU:统计灰度直方图,然后计算thresh=cnt0cnt1(u0-u1)*(u0-u1);取方差最大作为阈值thresh。其中灰度图像大于thresh作为目标对象数量统计为cnt0,灰度均值为u0,反之则为背景,数量统计为cnt1,灰度值均值为u1。

2 fpga实现

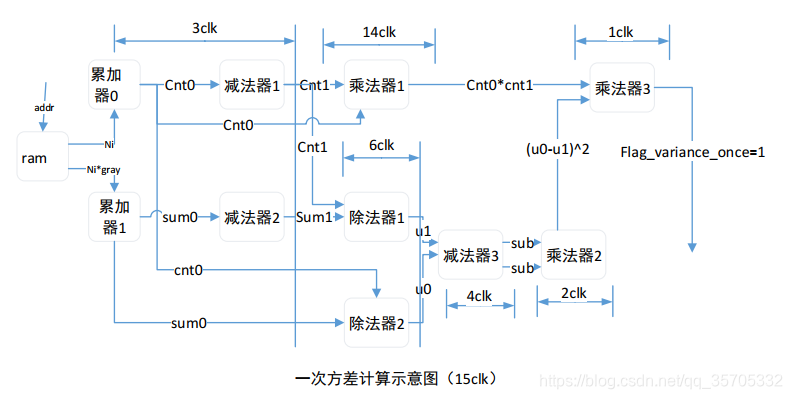

cnt0cnt1(乘法器1) need14clk;参考数据位宽17bit

u0=sum0/cnt0(除法器1)need 6clk;参考数据位宽为25bit/17bit

u1=sum1/cnt1(除法器2) need 6clk;参考数据位宽为25bit/17bit

(u0-u1)(u0-u1)(乘法器2) 在u0,u1计算出来后需要2clk。

一次计算如下图所示:

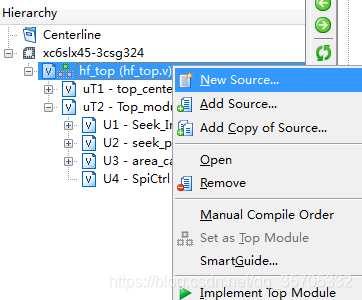

3 fpga调用ip核过程

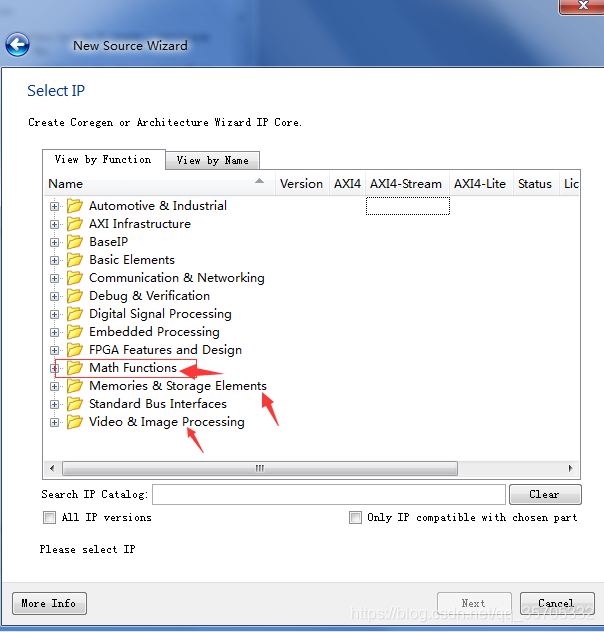

<1>右击你的工程项目-new source

<2>选择IP 输入名字随意

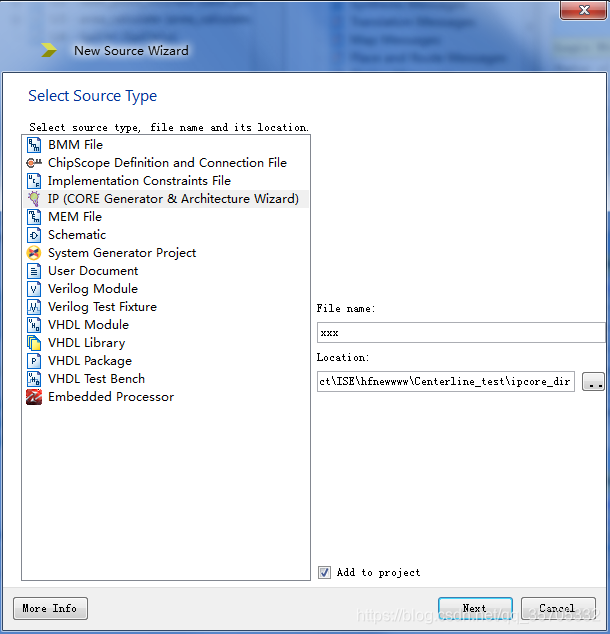

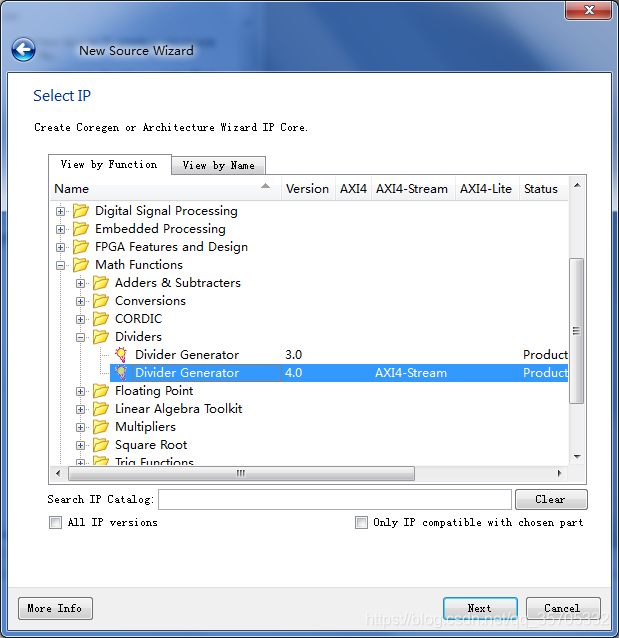

<3>选择你需要的IP核 -假设选择除法器

比如图像处理相关内容就在Image Processing;ram,rom,fifo在memory;加减乘除在math里。

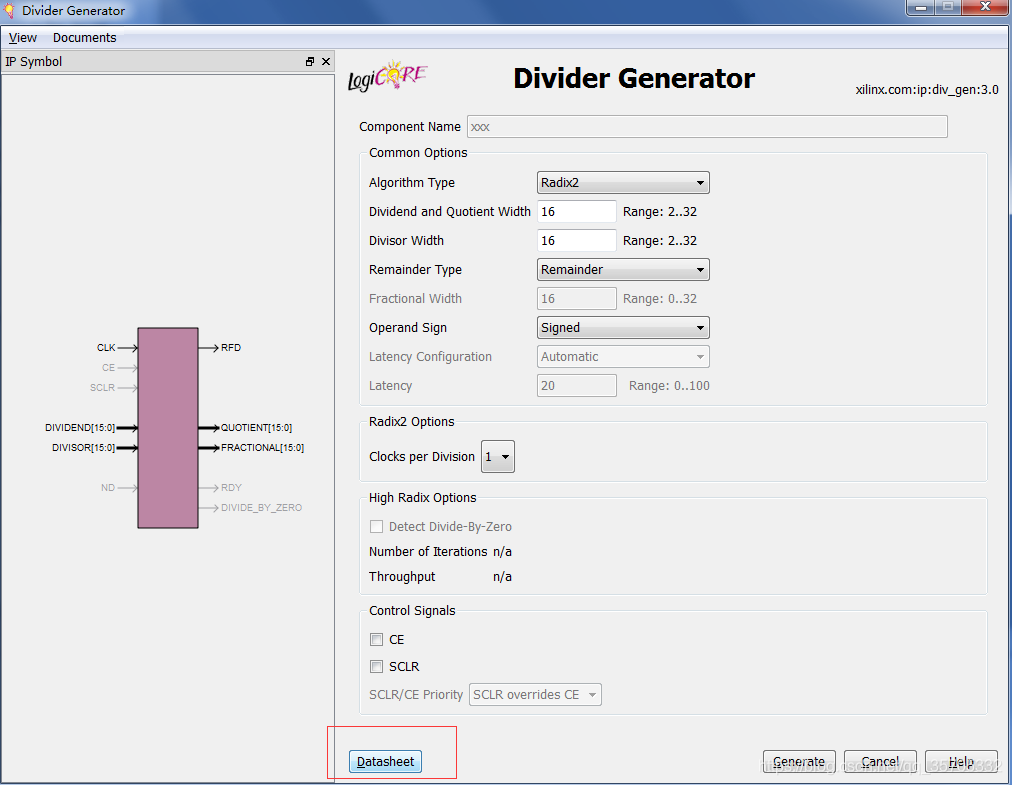

<4>除法器 -如图点击确定

<5>查看参考资料-datasheet

<6>参数填写-根据自己需求

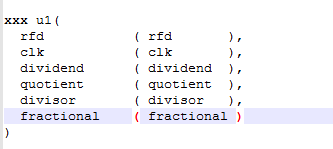

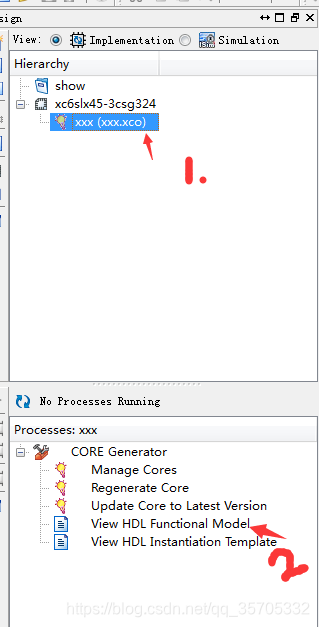

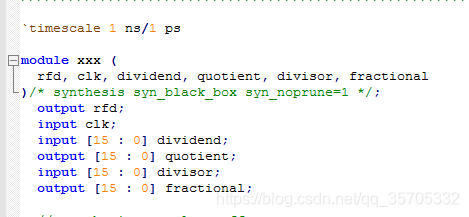

<7>查看ip核Verilog hdl

<8>例化

例化传入参数要为wire类型