Embedded knowledge -ARM bare metal - Study Notes (11): I2C bus communication

A, I2C bus

1. I2C bus Introduction

I2C (Inter-Integrated Circuit) of bus developed by Philips is a simple, two-wire bidirectional synchronous serial bus . It only requires two wires to transmit information between devices connected to the bus.

A bus master for initiating a data transfer and generates the clock to open transfer device, any slave device being addressed at this time is considered to be from the device. On the bus master and slave, and receiver on the relationship is not constant, but depends on the direction of data transfer at this time . If data to be transmitted from the host device, the host device from the first address, and then sends the data to the slave device, the final termination of the data transfer from the host; If you want to receive data from the host device, from the first device addressed by a master device, the host device receives the data transmitted from the host receives the final termination procedure.

2. I2C physical interface

Physical interface: the SCL the SDA + (use only two wires can be complex communication)

(. 1) the SCL (Serial Clock): a clock line CLK signal transmission, typically to provide a clock from the channel I2C master device.

(2) SDA (serial data) : line data, communication data are transmitted through the SDA line.

3. I2C communication features

I2C communication is a serial, synchronous, non-differential, low-rate communication mode.

(1) Serial: I2C serial communication belongs, all dataIn bits serially transmitted on the SDA line.

(2) Synchronous: synchronous communication is communication both work in the same clock , typically to the A-party B through a communication line for transmitting the signal CLK A own clock, the work B A transmission clock. Therefore, a significant feature of synchronous communication is:There communication line CLK.

(3) Non-Difference: because the I2C communication rate is not high, and the communication distance close to both sides, so that the communication using the signal level.

(4) low rate: I2C generally used inCommunication between the two boards on the same ICAnd the amount of data for transmission, the communication rate itself is low (typically a few hundred KHz, different chips I2C communication rate may be different, they are using the device depends on the time allowed in programming the highest communication I2C the rate can not exceed this rate).

+ From the master device

when I2C communication, communication parties are unequal status , but the sub-master and slave. Communication is initiated by the master device, the master device by a dominant, but the device according to the I2C protocol from passive acceptance of communication with the master device, and timely response.

Who is the master, who is from the device by communicating parties to a given (I2C protocol are not required), in general, a chip device can only call the shots, you can only do from the device, it is possible not only when the main device and when the energy from the device (But not at the same time when two)。

May be a plurality of devices on the bus (from device address)

the I2C communication may be one (1 master device from a device), it may be one to many (a plurality of slave devices to the master device).

Be responsible for scheduling bus master, decides that a communication time and from which device. Note: the same time, only a pair of communication information transmitting device on the I2C bus, at the same time only one master device from the communication device and the other device is in the "hibernation" state, it is not trouble, otherwise communication would hell broke loose.

Each I2C slave device has a communication I2C slave address , the device address of the device from the inherent properties, thenWhen the primary communication device needs to know that they were going to address the communication from the device, Then if the address is not in the communication from the device that they seek. (This address is only a circuit board, not globally unique).

4. I2C bus communication timing

Interpreted literally, the timing is the time sequence, the timing is actually the communication line level variations occur in time sequence, and significance of these changes is called a communication sequence in the communication.

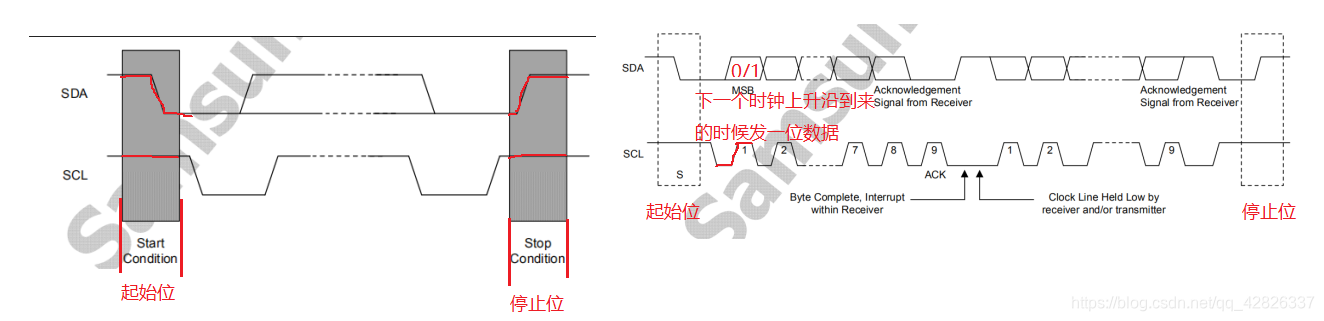

I2C bus idle state, the start bit, the end bit

There are a host device, n (n> = 1) slaves on the I2C bus. I2C bus has two states; idle state (and none of all devices from the communication master device, when the bus is idle) and Busy (wherein a and a communication device from the master device, to the bus is occupied at this time, other We must recover from the device). A communication cycle is divided into a whole cycle, two neighboring communication cycle idle state .Each communication cycle starts with a start bit, an end bit end, the intermediate data in this communication cycle。

Start bit is not a point in time, the start bit is a period of time , changes the state of the bus during this period is:CLK line maintains the high level, the SDA line is a high to low going edge。

Similar to the start bit, the end bit is a period of time . During this time the bus state changes are:SCL line maintains the high level, the rising edge of the SDA line from low to high a。

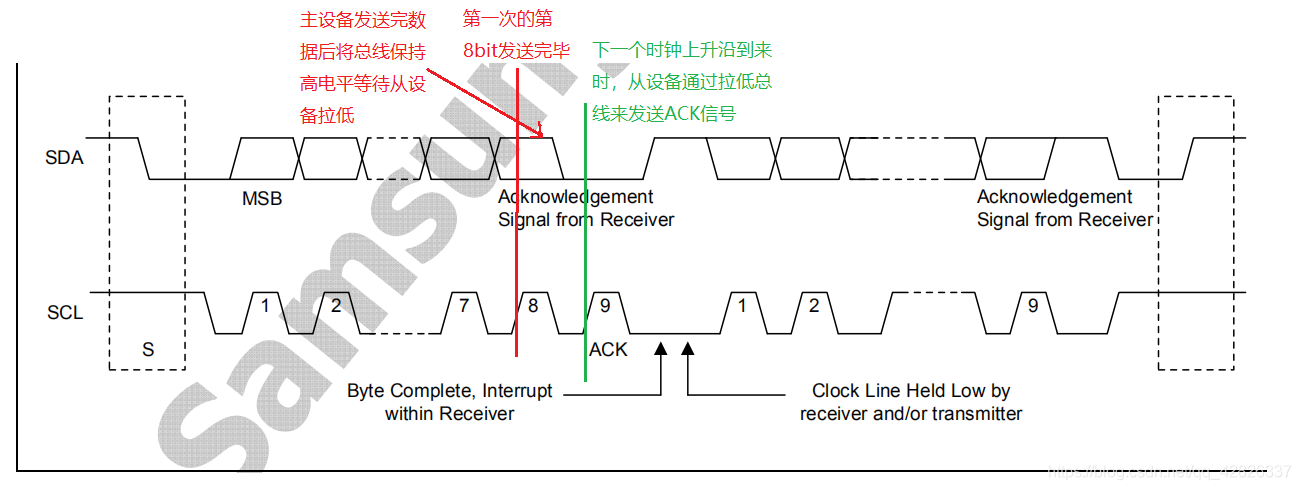

inThe next rising edge of the clock a start bit of data transmission may occurIt must be stabilized before the rising edge coming. Data transmission, data line from 0 to 1, prior to a rising edge of the next must be completed.

5. I2C data transfer format

Each initiate and end of the communication cycle is by the master to do , and only responds to the master device from a passive, unable to do anything themselves spontaneously. Master device in each communication period starting 8-bit slave address (in fact, only eight slave address is 7, and a front one below the device to be written or read) to the bus (host device is sent as broadcast, as long as all the devices on the bus can actually receive this information). Then the device can receive from this address, and the address of each received on the bus and their device address comparison for equality. If they are equal explain the master of this communication is to talk to me, if you do not want to explain this and other communication has nothing to do with me, not heard regardless.

The sender sends a piece of data, the recipient needs to respond to the ACK a . This response itself is only one bit position, does not carry useful information, only 2 represents mean (represented by either the received data, i.e. effective response; represents either not received data, invalid response).

At a certain moment a communication, the master device and the slave device can have only one after the (bus occupied, i.e. write to the bus), the other in the closed (from bus read). If at some time the master and slave are trying to write to the bus it finished, the communication went wrong.

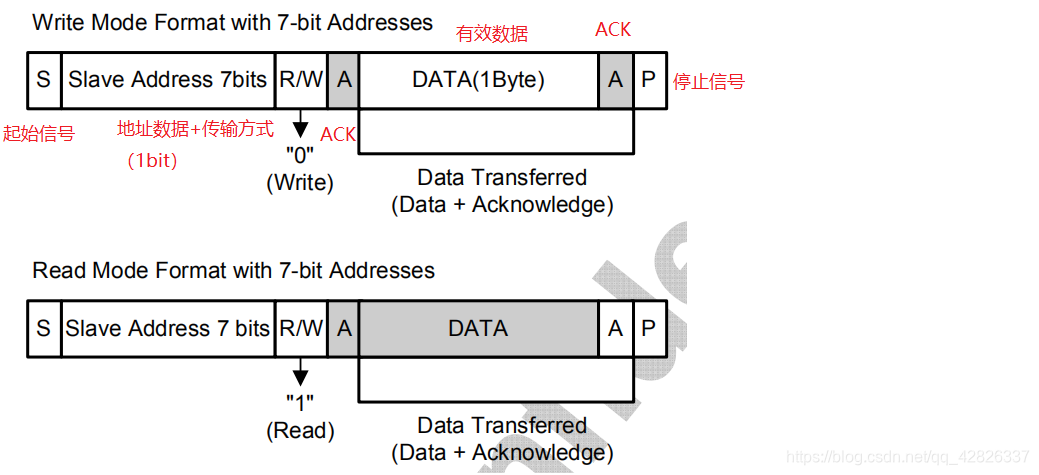

Below shows the output transmission format:

whereinWhite-based devices from the device, from gray to the master apparatus.

When the write mode when: The first sends a start signal from the master, followed by the next rising clock edge to a temporary address, is sent from the device through the bus (7 wherein the address data indicates a write mode) after receiving the address of each device on the bus from the own address contrast, if the corresponding were selected, then an ACK signal is transmitted from the device tells the master device is ready, the master sends 8 bit data received from the device to It sends an ACK signal to the data transmitted by the master device after the stop signal indicates the transfer is complete.

When the read mode when a situation: first transmitting a start signal from the master, followed by the next rising clock edge to a temporary address, is sent from the device through the bus (7 wherein the address data indicates a read mode) , from each device on the bus after the address received with its own address relative ratio, if the corresponding were selected, then an ACK signal is transmitted from the device tells the master device is ready, and then to start the transmission of 8bit data, the master device received after ACK to send a signal, and then sends a stop signal marks the end.

I2C communication unit when the basic data is in bytes ,Each effective data is one byte (8 bits).

8 clk and after the start bit are transmitted in the master device (the device that control bus), the bus at this time can be read from the device to the master device that the information sent from the reading apparatus via the bus; then to ninth cycle, in accordance with a predetermined protocol from a device needs to transmit an ACK to the master, so in this case the master device must release the bus (the bus master device is set to a high level and do not move, in fact, similar to the bus idle state), whileACK sent from the device tries to pull down the bus. If the bus down from equipment failure, or simply do not have the equipment down the bus, the master device is the bus to see the phenomenon still remains high in the ninth cycle, which is the master, it means I did not receive ACK, just considered the master device to the slave device sends 8 bytes wrong (reception failure) .

Two, S5PV210 I2C bus

1. I2C controller

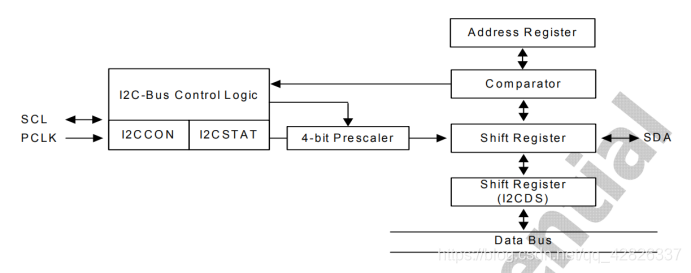

From the main communication device is essentially two sides by timing the work, but the timing would be more complicated SoC software is not conducive to completion, and thus the solution is internal SoC built-in hardware controller generates a communication timing . We only need to write software configuration values can be written in the register of the controller, the controller will generate the appropriate timing in communication lines and other communications.

(1) clock source is PCLK_PSYS (65MHz) , through the internal division level 2 finally obtained CLK I2C controller. The first fraction is the frequency of I2CCON bit6, can be an intermediate clock I2CCLK (equal PCLK / 16 or PCLK / 512); second fraction was the final frequency clock I2C controller works to I2CCLK the intermediate clock source, frequency division factor [1,16], because 4bit (corresponding to 15 plus 0 to 1). To obtain the final stage after the clock is divided by 2 clocks, such a setting is available: 65000KHz / 512/4 = 31KHz communication CLK will be passed from the device via the SCL line .

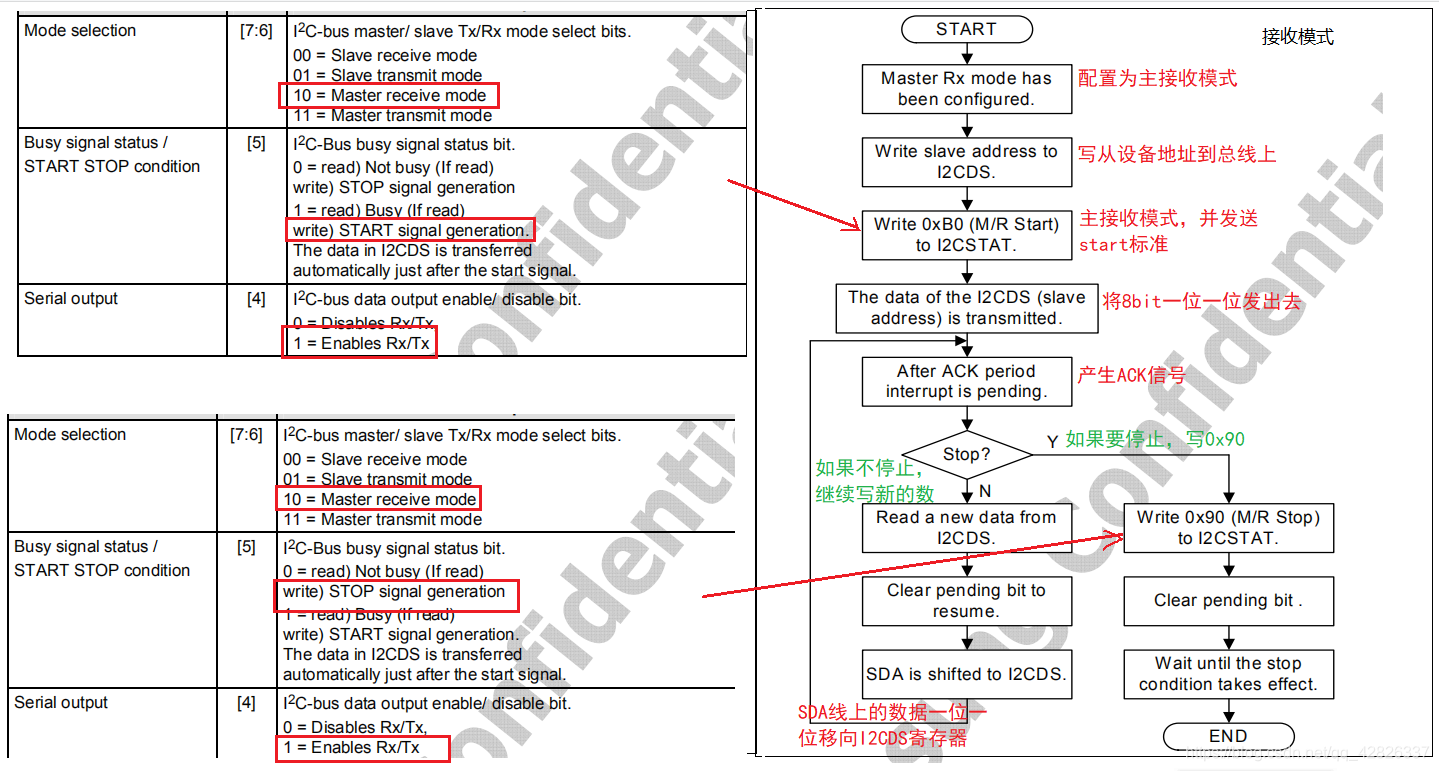

(2) I2C bus control logic (front representatives are I2CCON, I2CSTAT both registers), is mainly responsible for the I2C communication sequence. Actual programming to send a start bit, stop bits, etc. are received through the two ACK register (represented behind the circuit module) implemented.

(3) a shift register (shift register), the byte code data to be transmitted into one bit by one bit shift register threw the SDA line to the transmission / reception .

+ Register address comparators. I2C controller to do with the present time from the device.

(4) The I2CADD : to write their own slave address.

(. 5) I2CDS : transmitting / received data are placed here.

2. Process bus communication

Master / receive mode

add here that: that is, when 8bit address data transmission, in fact, is the direction of + 1bit 7bit address.

For example:

KXTE9 I2C address fixed 0b0001111, I2C slave address itself is 7 bits, but transmits an I2C communication I2C actually transmitted when the slave address is 8 bits, the 8 bits 7 bits (bit7-bit1 ) corresponding to the I2C slave address of the device 7, the lowest one (LSB) is stored in R / W information (that is to say the next dataWrite apparatus for reading from the master device (corresponding to 0), the master device reads from or write device (corresponding to 1)). Thus, for KXTE9 is, when the master device (SoC) issued gsensor information, the SAD should be: 0b00011110 (0x1E), while the master reads gsensor information, it should be 0b00011111 (0x1F).