Review of Principles of Computer Organization: Memory Systems

Storage includes:

Classification of memory

- Divided by storage medium:

semiconductor memory, magnetic surface memory, optical memory - According to the nature of reading and writing:

(1) Random read-write memory (RAM, volatile memory, power-off content disappears): static random access memory SRAM, dynamic random access memory DRAM

(2) read-only memory (ROM, non-volatile memory , the content will not disappear after power off): EPROM, EEPROM, Flash Memory - According to the hierarchical role in the computer

(1) main memory (memory)

(2) cache memory Cache

(3) auxiliary memory (external memory)

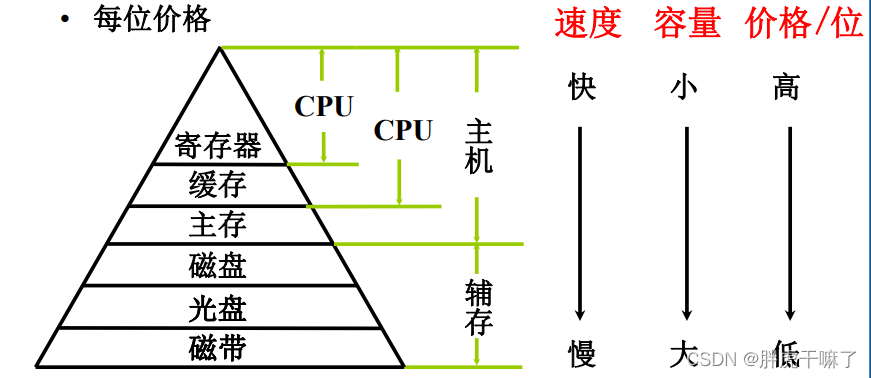

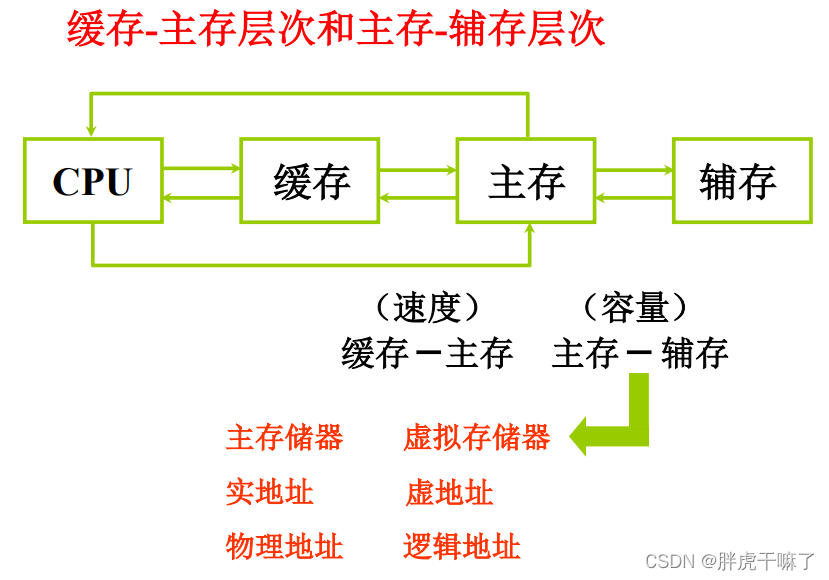

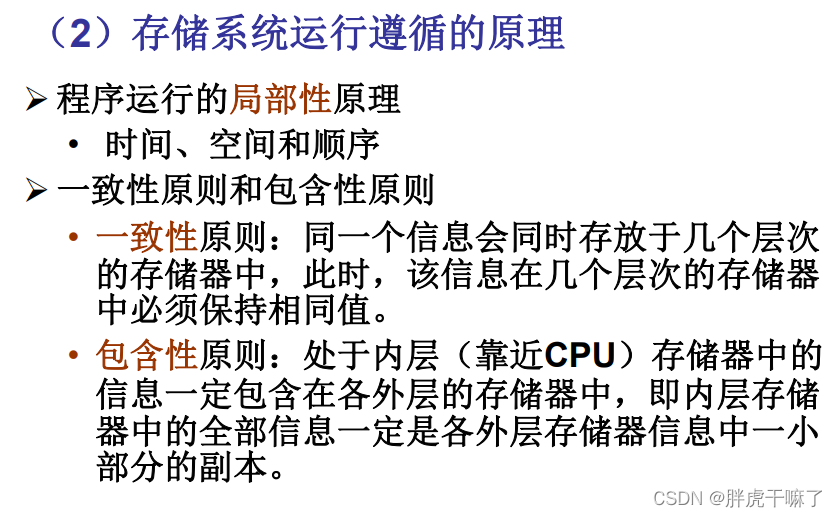

3.1 Hierarchical structure of memory

3.2 Semiconductor random access memory (RAM, volatile memory)

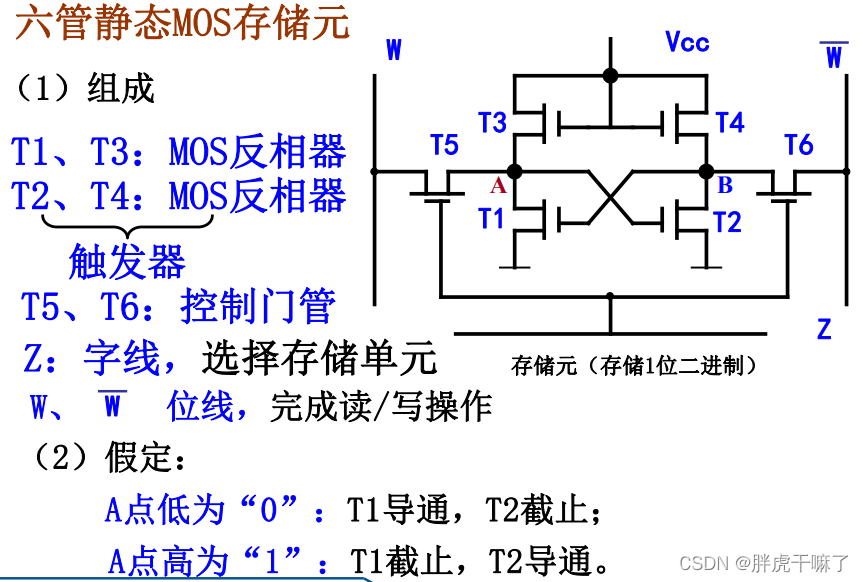

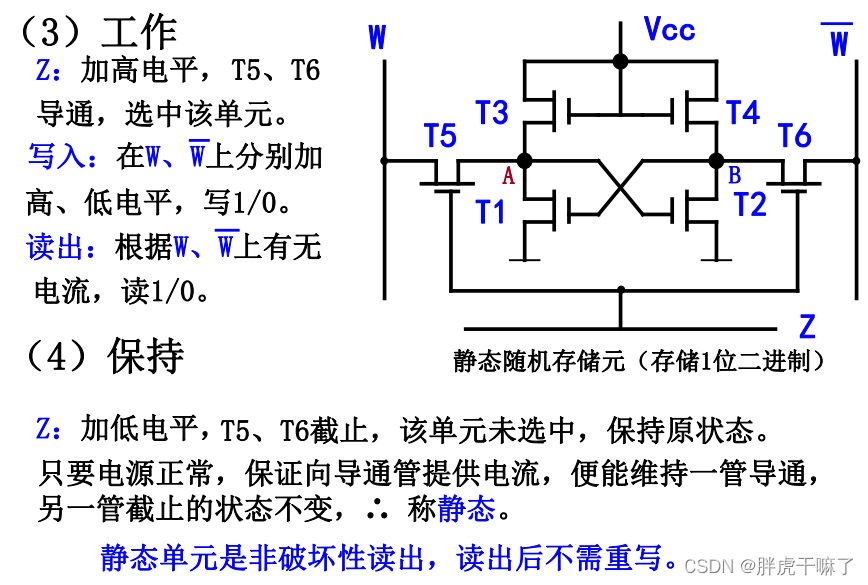

3.2.1 Static Random Access Memory (SRAM)

- The principle of SRAM storing information: relying on the internal cross-feedback mechanism of the bistable circuit to store information

- Storage features: fast speed, high power consumption, low integration, called Cache

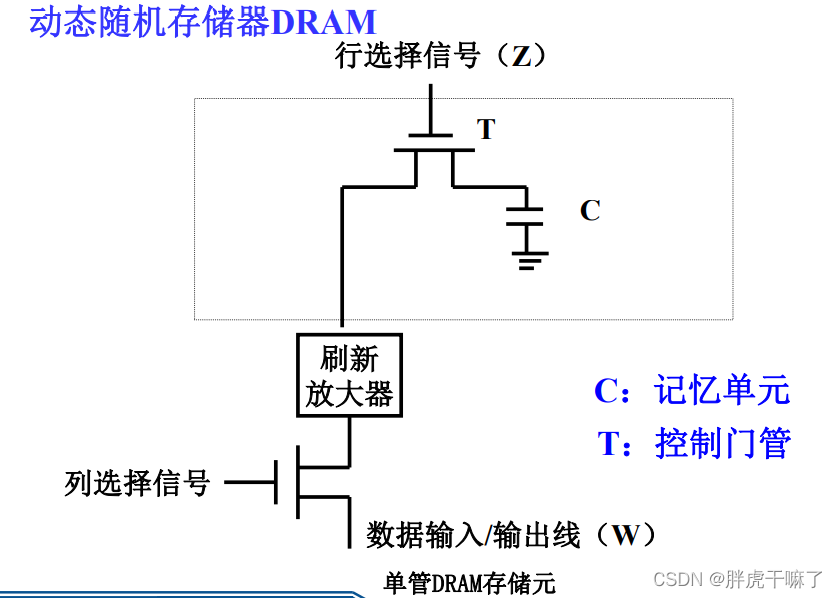

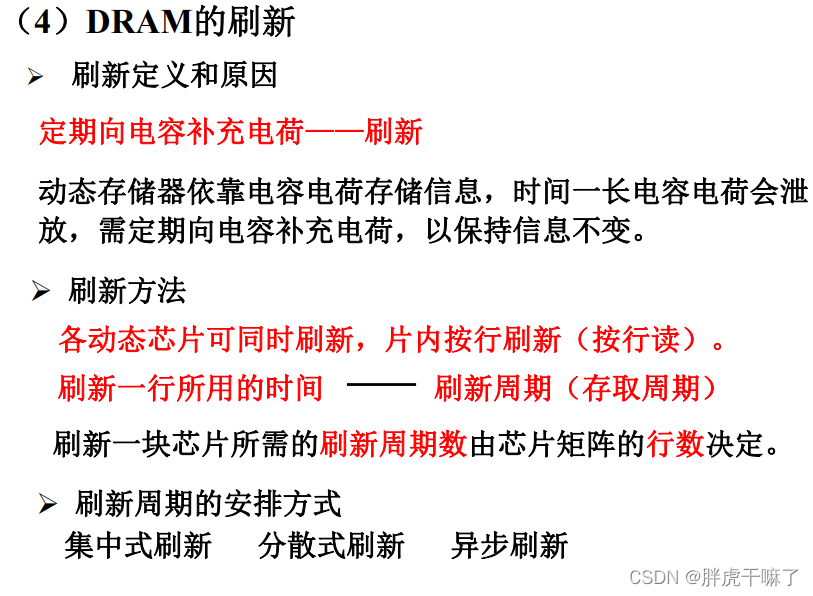

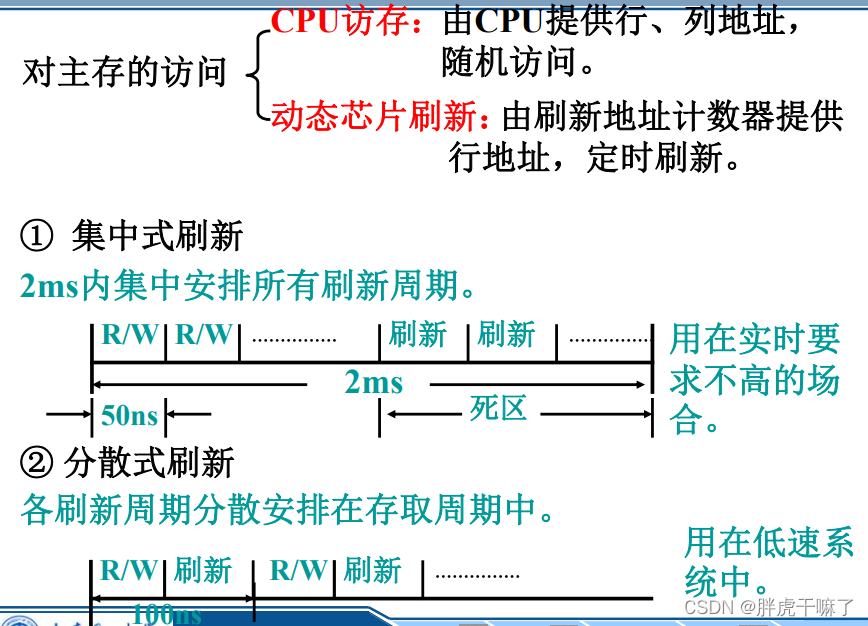

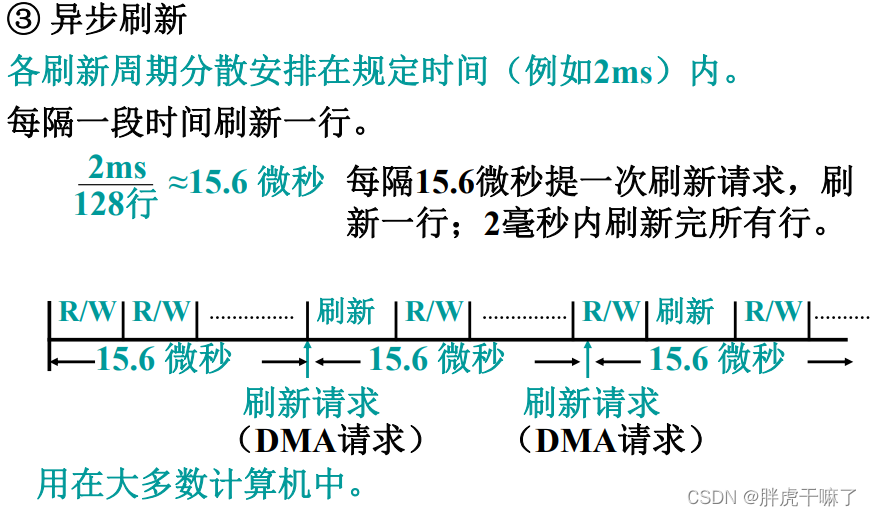

3.2.2 Dynamic Random Access Memory (DRAM)

- The principle of DRAM storing information: relying on the principle of capacitor storage charge to store information

- Features: low power consumption, high integration, fast speed. It is now used as main memory by various computers

3.2.3 Read Only Memory (DOM)

Features of ROM:

- Simple structure, higher bit density than memory that supports read and write, supports random access

- ROM is non-volatile and therefore highly reliable

- According to the manufacturing process, it can be divided into:

(1) Masked read-only memory MROM: written by the manufacturer, cannot be changed, reliable and cheap, high integration and poor flexibility

(2) One-time programmable read-only memory PROM

(3) Erasable programmable read-only memory EPROM

(4) Flash memory False Memory

fast read and write, easy to integrate

(5) Solid State Drives

Flash memory-based storage array

3.3 Connection of main memory machine and CPU

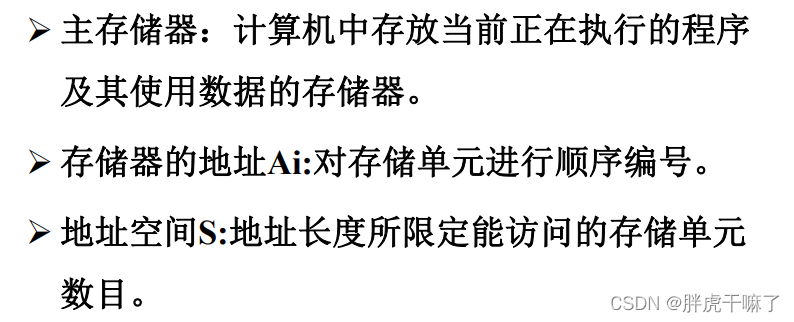

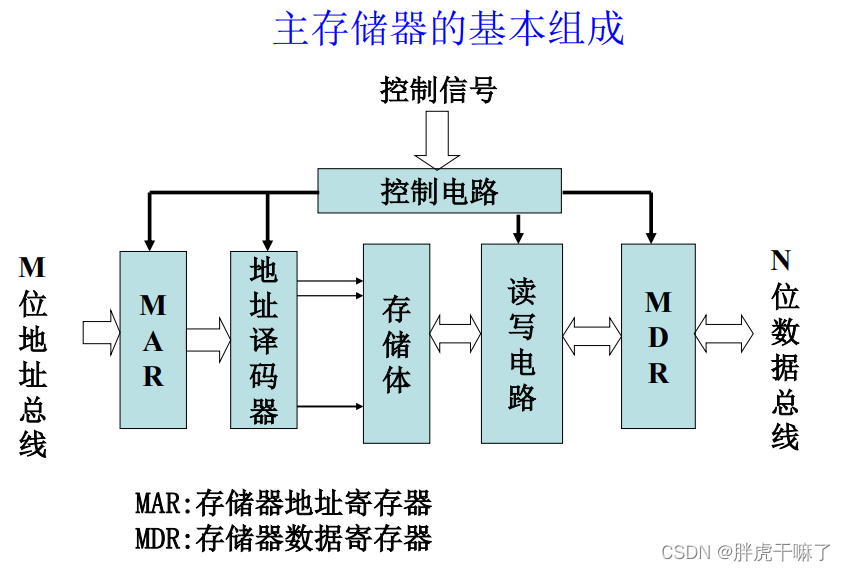

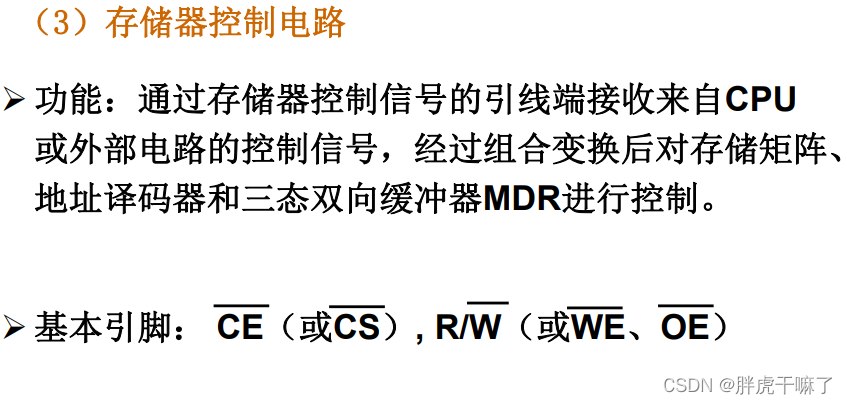

3.3.1 Composition and control of main memory

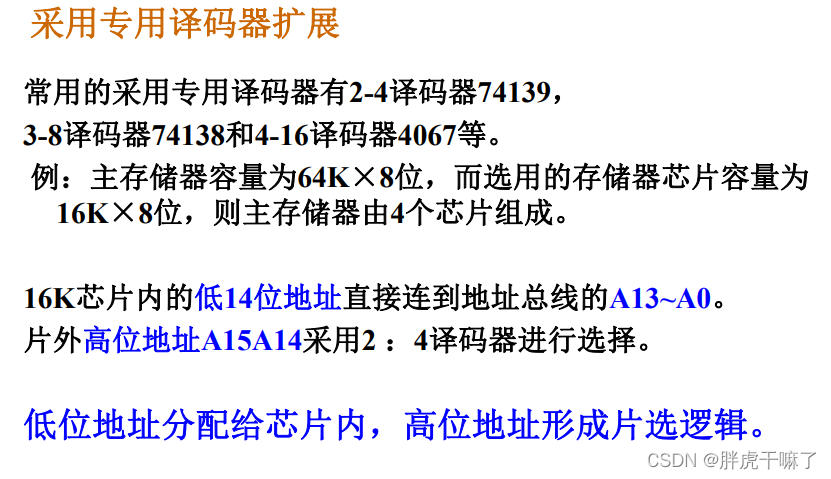

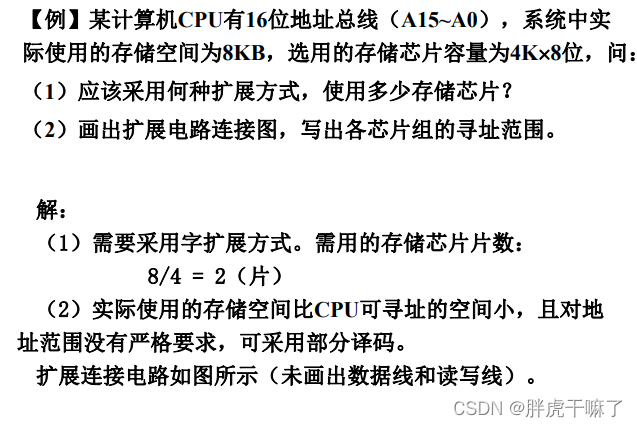

3.3.2 Main memory capacity expansion

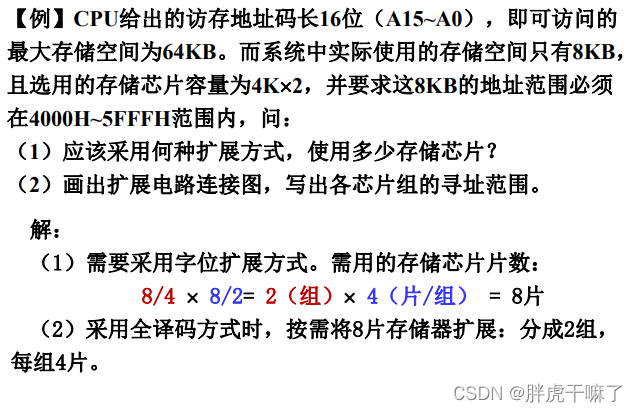

Storage capacity: the total number of stored information, capacity = number of stored words x word length, such as 1Kx4, the number of stored words is 1k, and the word length is 4 bits

Access time T A : the time it takes for the memory to start from the address code of the street storage unit to being alone or storing data

Storage cycle TM : The shortest time interval required by the CPU to access the memory twice in succession. The storage cycle includes the access time, so it should be slightly larger, T M > T A

Extension method:

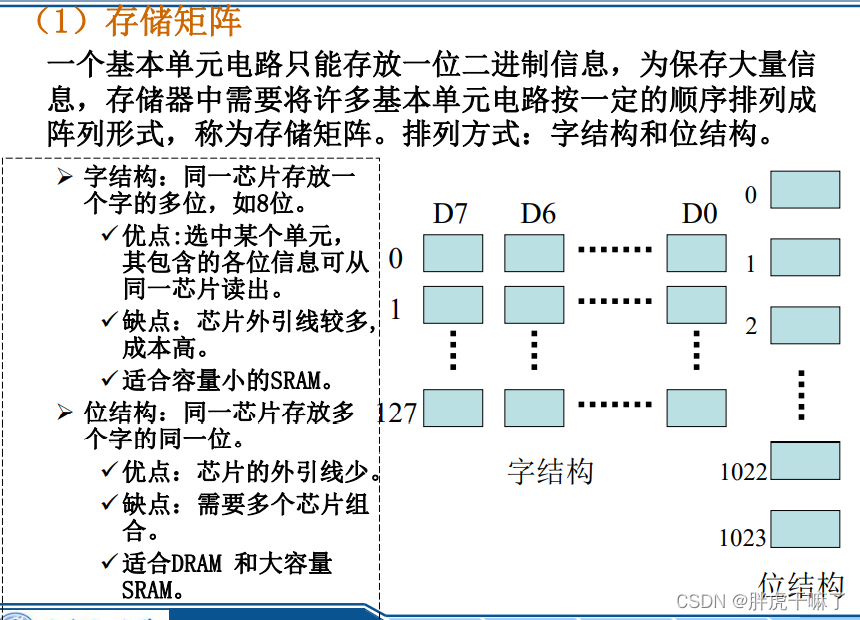

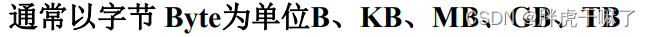

- Bit expansion: use multiple memory devices to expand the word length.

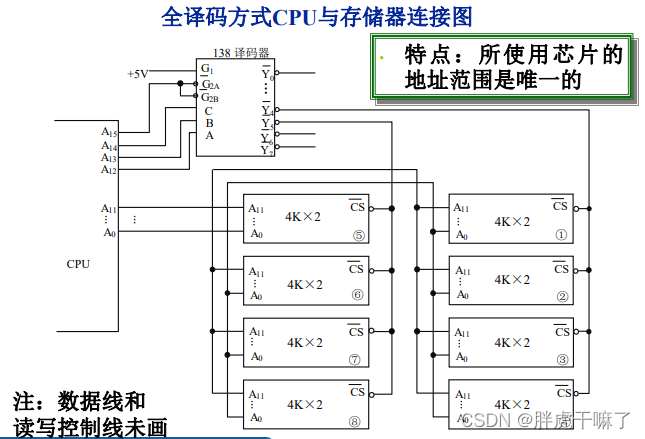

Connection method: connect the address lines, chip select terminals, and read-write control terminals of multiple memories in parallel, and lead out the data terminals separately. The data lines of multiple bit-expanded memory chips Connected to different bits of the system data bus, these chips are considered as a whole

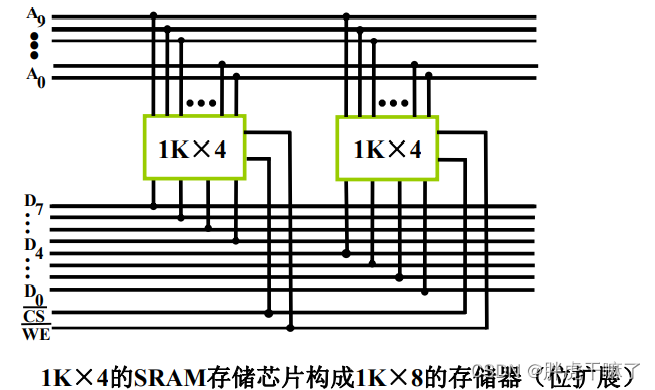

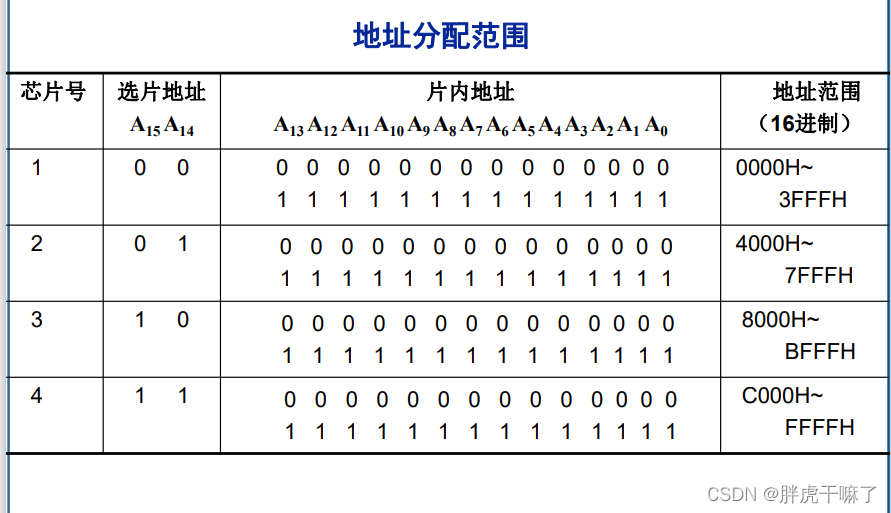

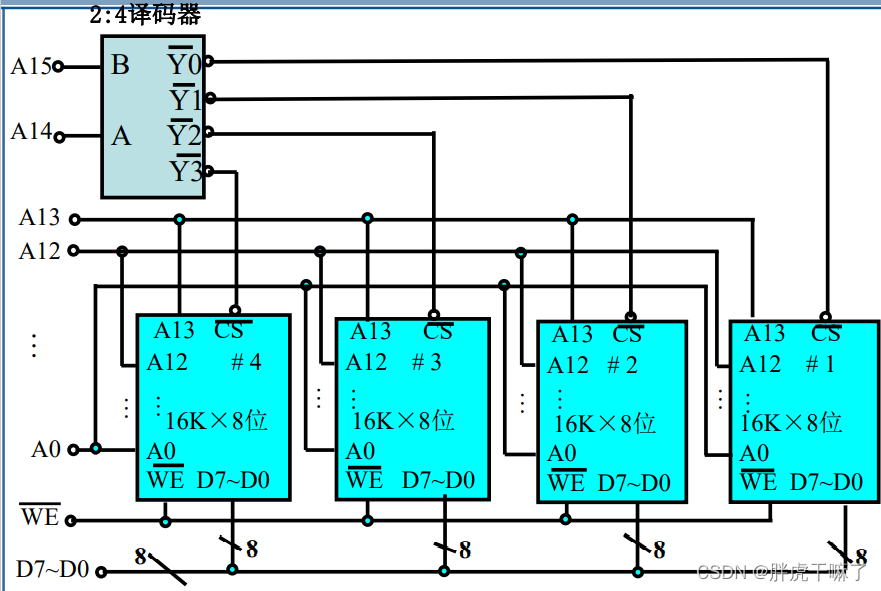

- Word expansion: increase the number of words in the memory.

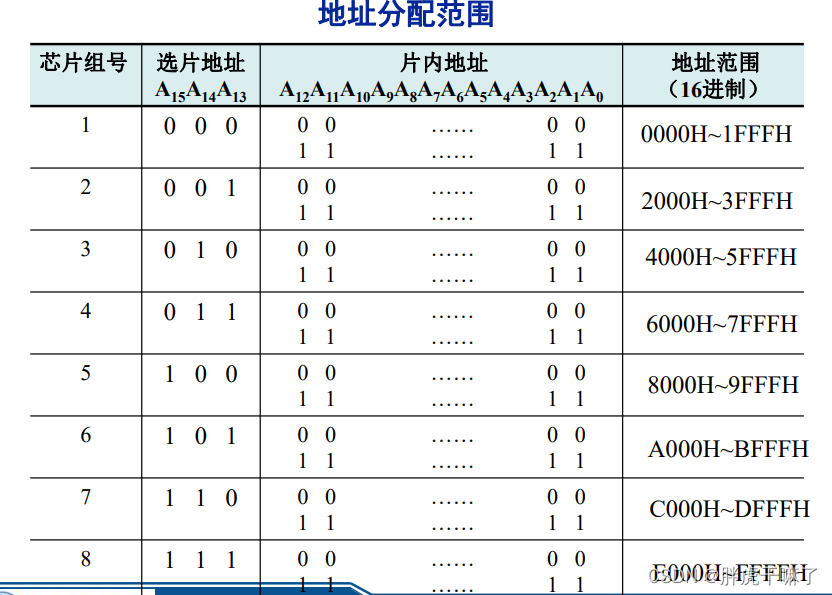

Connect the address lines, data lines (compared to bit expansion, word expansion adds data lines) and read and write control lines of each chip in parallel, and use the chip select signal to distinguish the address range of each chip

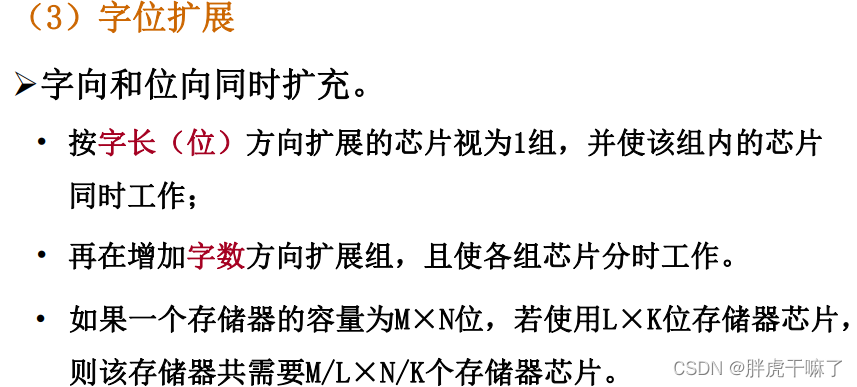

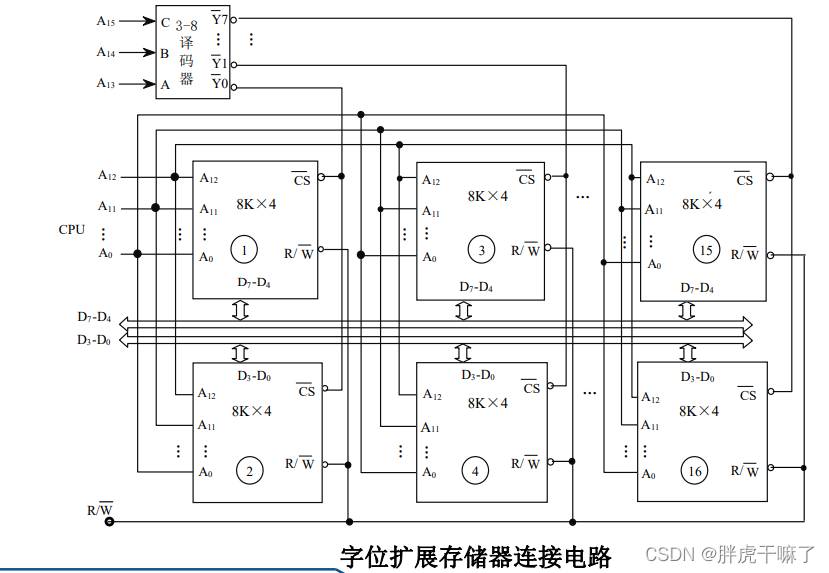

- character extension

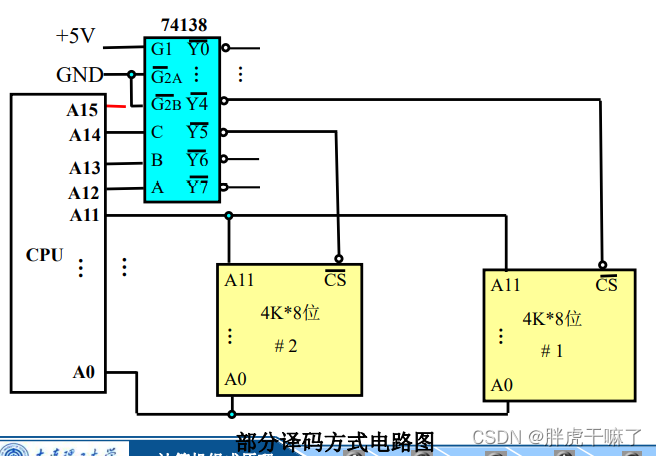

3.3.3 Connection between memory chip and CPU

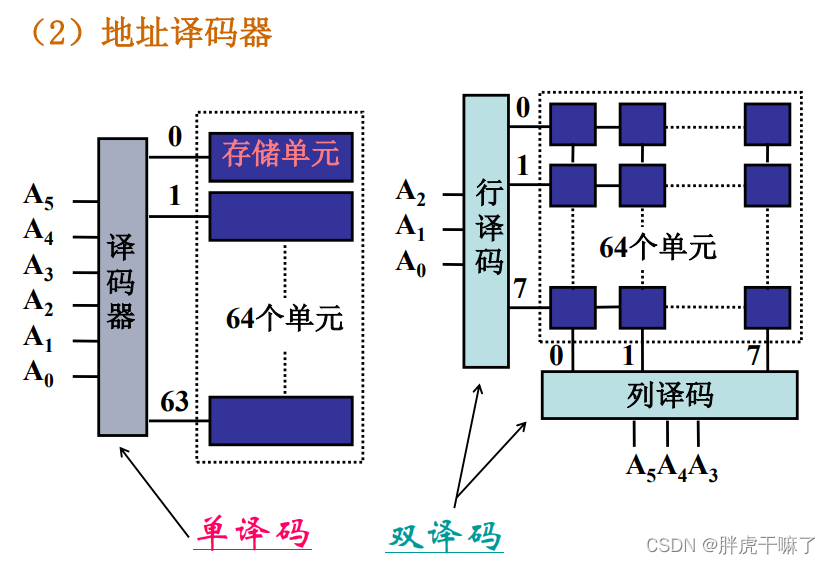

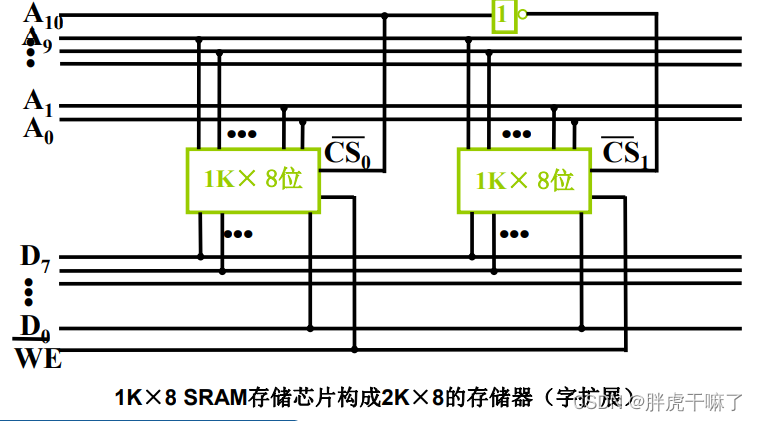

Decoding method:

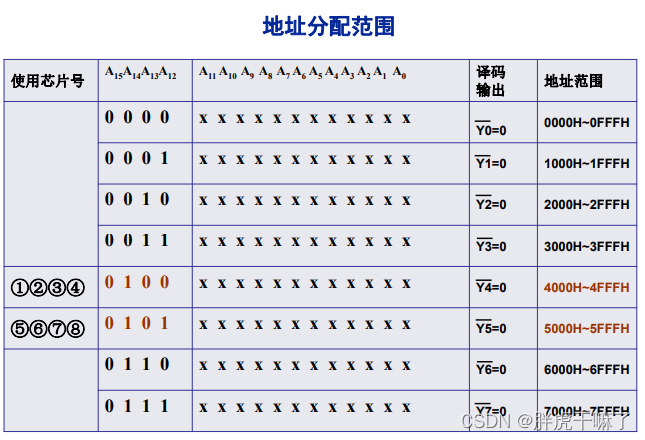

(1) Full decoding: All the selected film addresses participate in decoding.

There are two cases of full decoding:

- The actual storage space used is the same as the maximum storage space accessible by the CPU

- The actual storage space used is smaller than the maximum storage space accessible by the CPU, but there are strict requirements on the address range of the actual space

Features of full decoding: the address range of the chip used is unique

When A15~A12 is 0100, the Y4 bar of the 38 decoder is 0, the others are 1, and the CS bar enable terminals of the four cards on the right half are 1, power on, and extract the content in the 4Kx8 memory.

As for the classification of the CPU access address code length according to 4+12 channels, it is because a single card 4K is 2 12 , which requires 12 binary bits for encoding

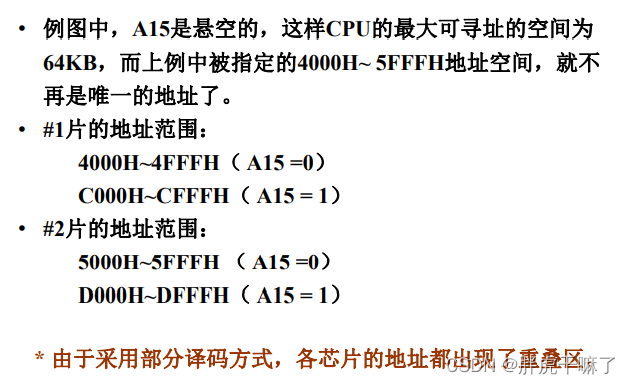

(2) Partial decoding

When the actual storage space used is smaller than the maximum storage space accessible by the CPU, and there are no strict requirements on other addresses, this decoding method can be used

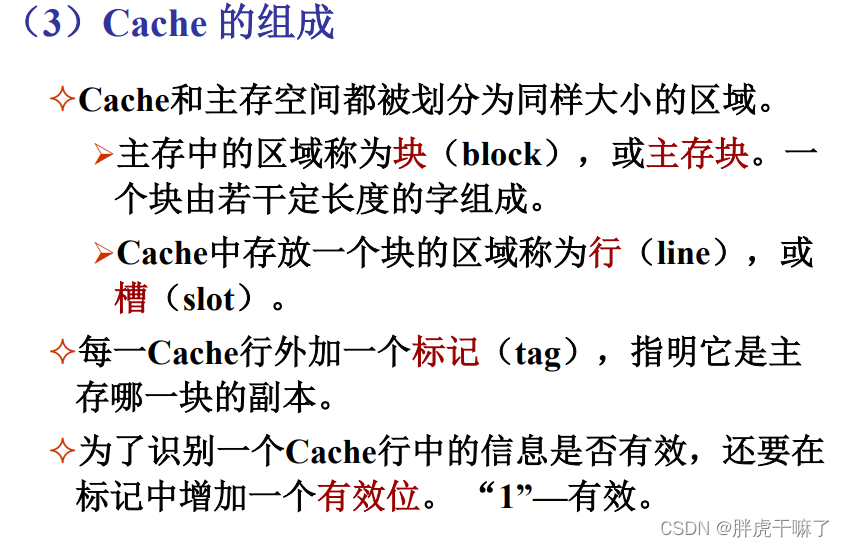

3.4 Cache memory Cache

Main content:

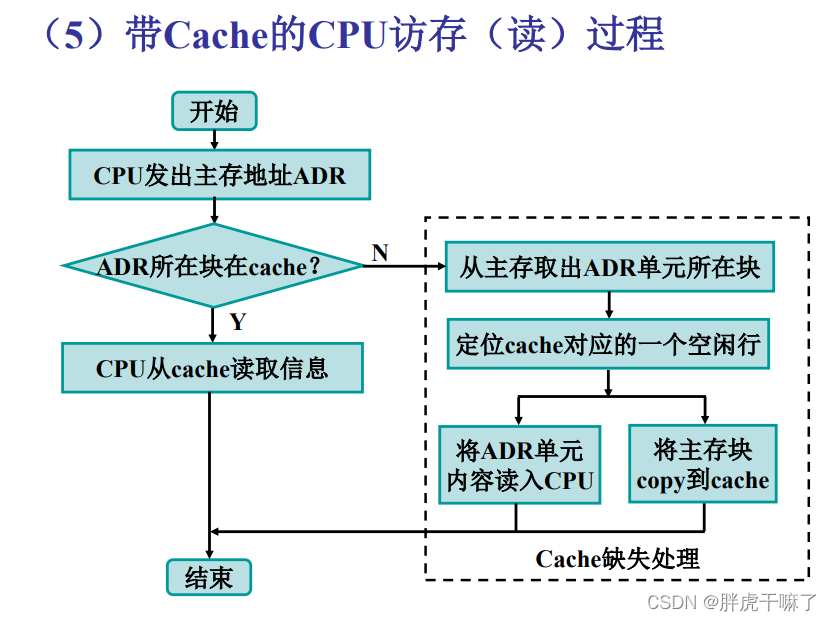

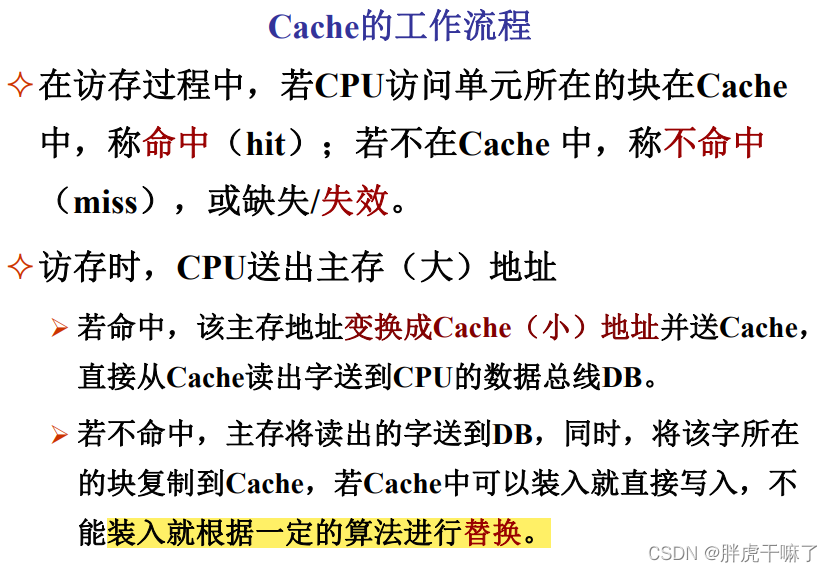

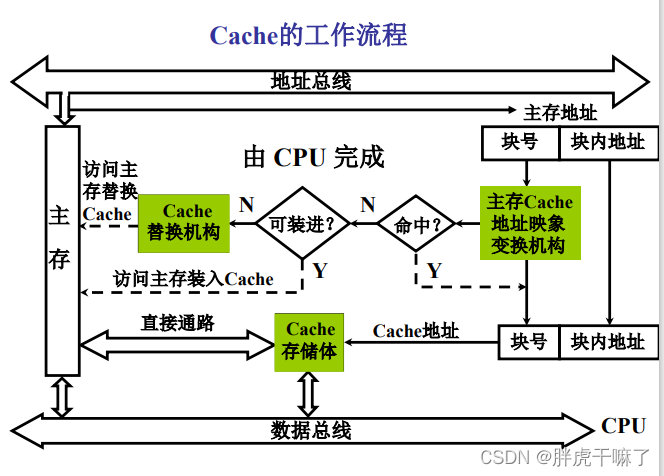

(1) Composition and working principle

(2) Basic image methods of Cache: full associative image, direct image, group associative image

(3) Replacement algorithm

(4) Hit rate and related calculations

3.4.1 Basic Working Principle of Cache

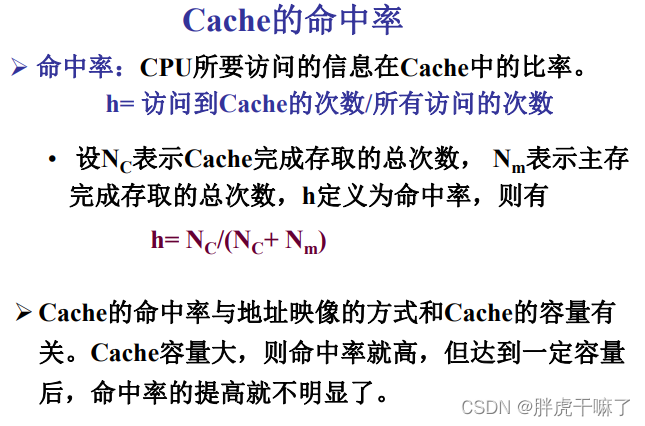

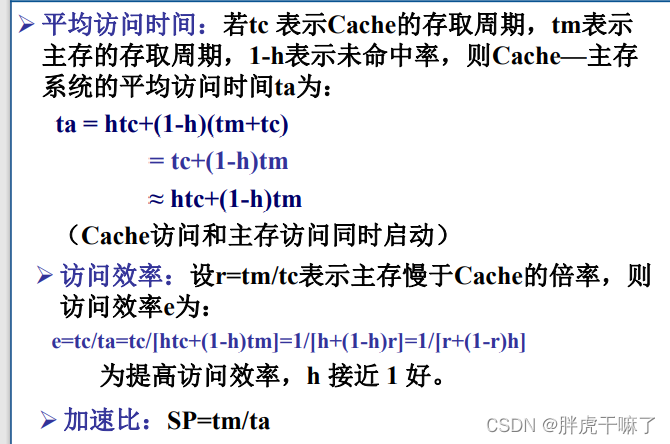

3.4.2 Cache hit rate

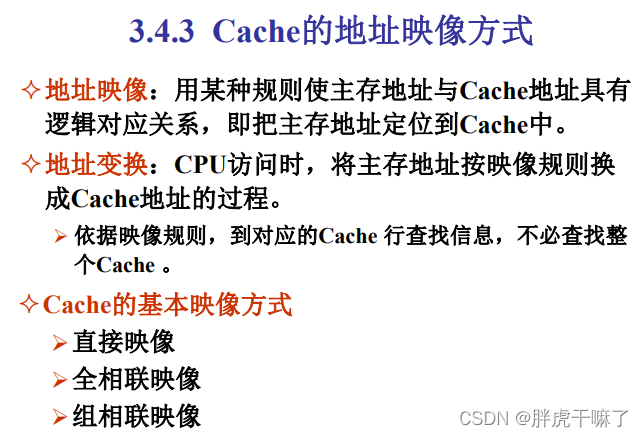

3.4.3 Cache address mapping method

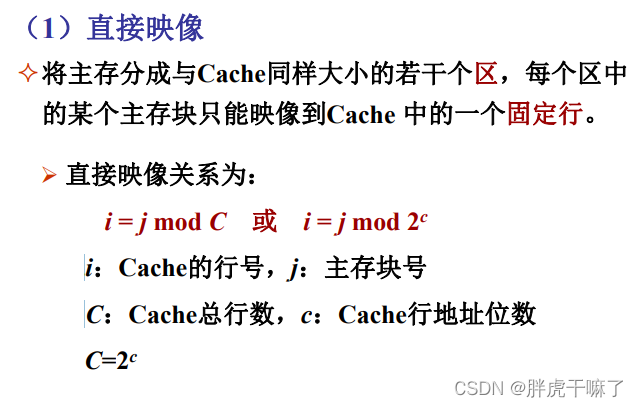

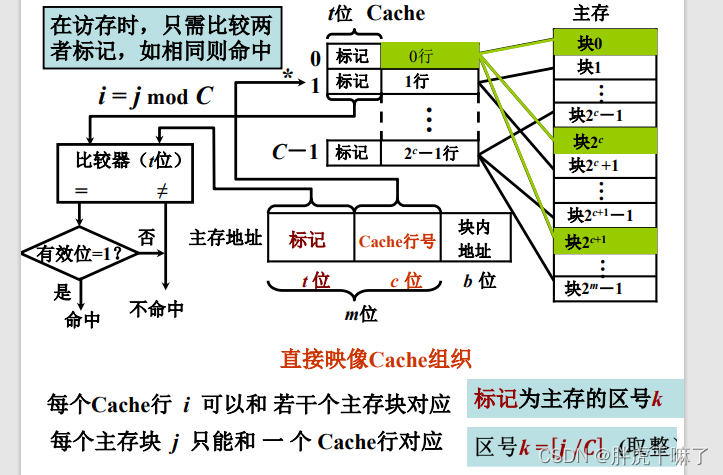

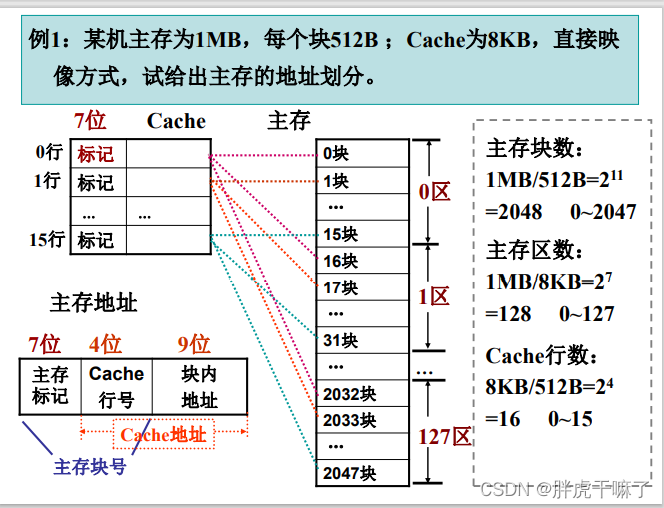

(1) Direct image

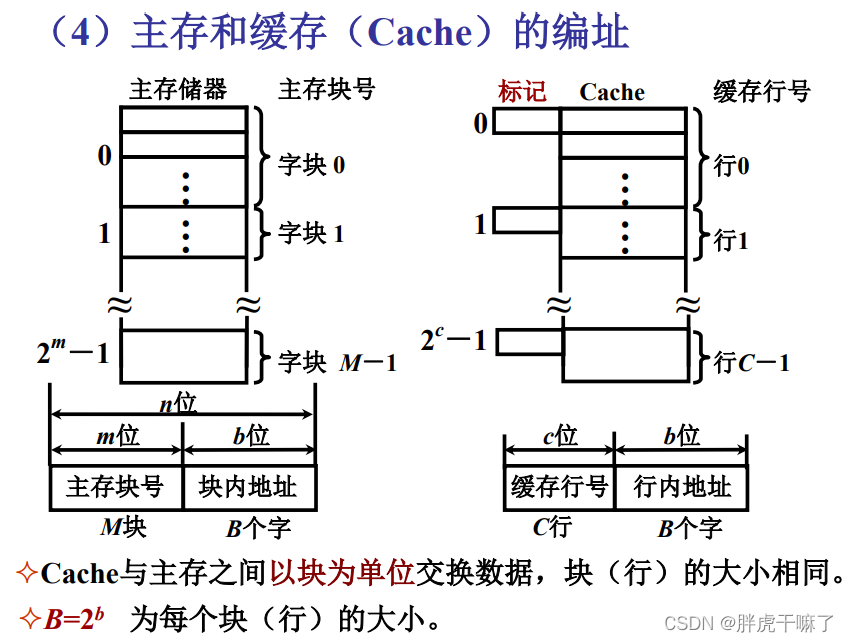

The main memory has 27 partitions, so 7-bit binary is required as the main memory mark first. For the Cache, there are 16 lines in total, and 4 bits are required as the Cache line number. The last line size (the size of each block) is 512B, so 9 bits are needed to describe

the address in the block The above-mentioned address division of the main memory

Features of direct mapping:

Advantages: Easy to implement, only need to use the address of the main memory, and directly judge according to certain fields, you can determine whether the required block is already in the Cache Disadvantages: Not

flexible enough, many blocks in the main memory can only correspond to the only one cache line. The storage space is not fully utilized and the hit rate is low

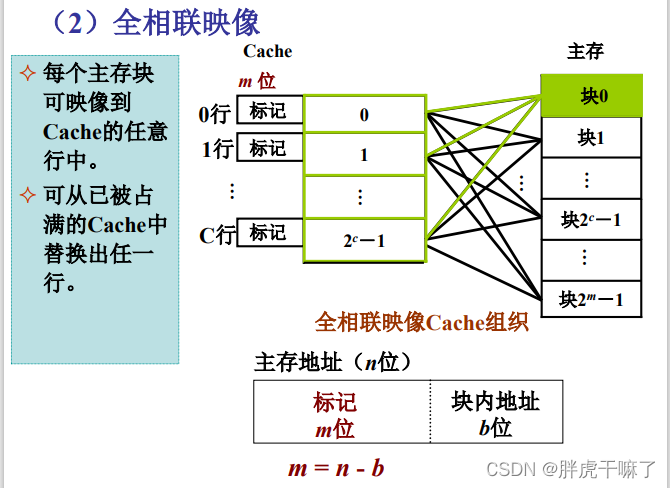

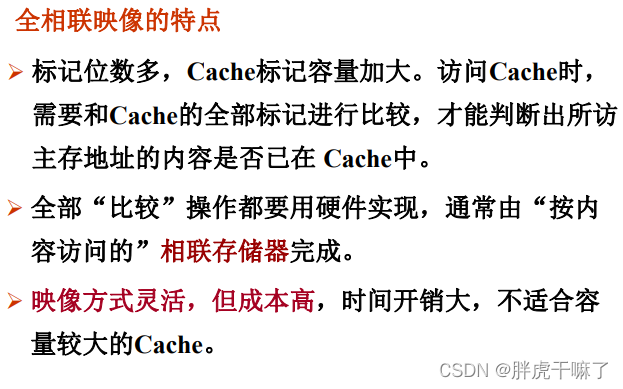

(2) Fully associative image

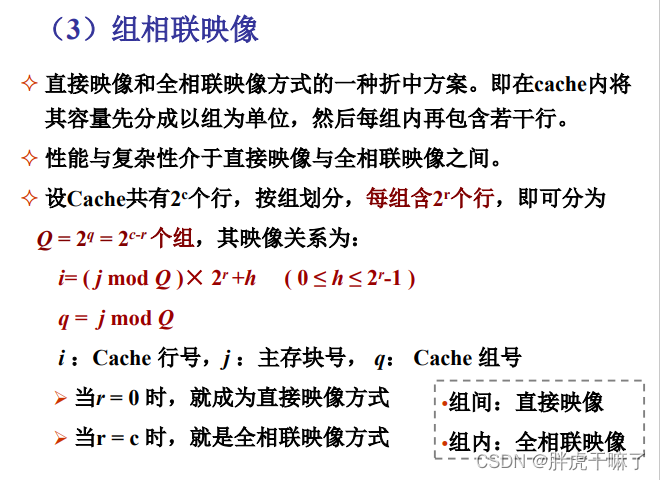

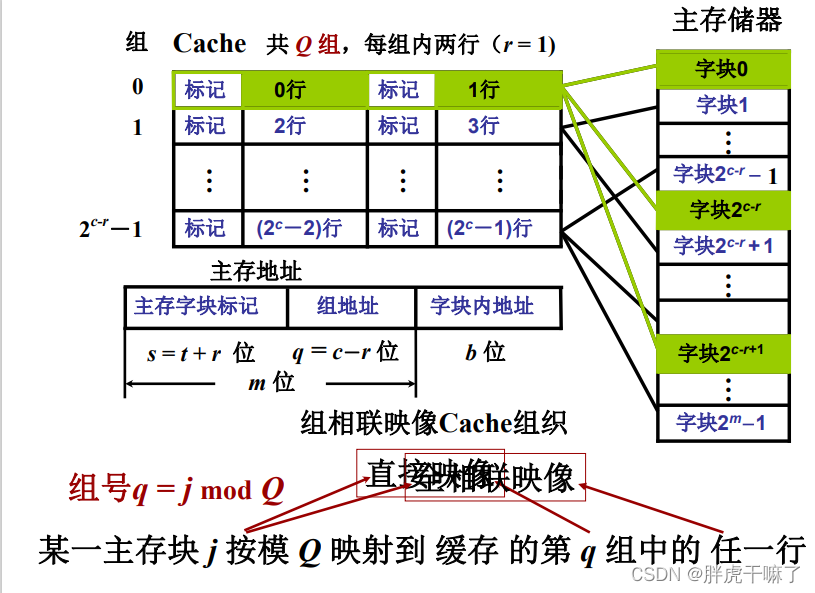

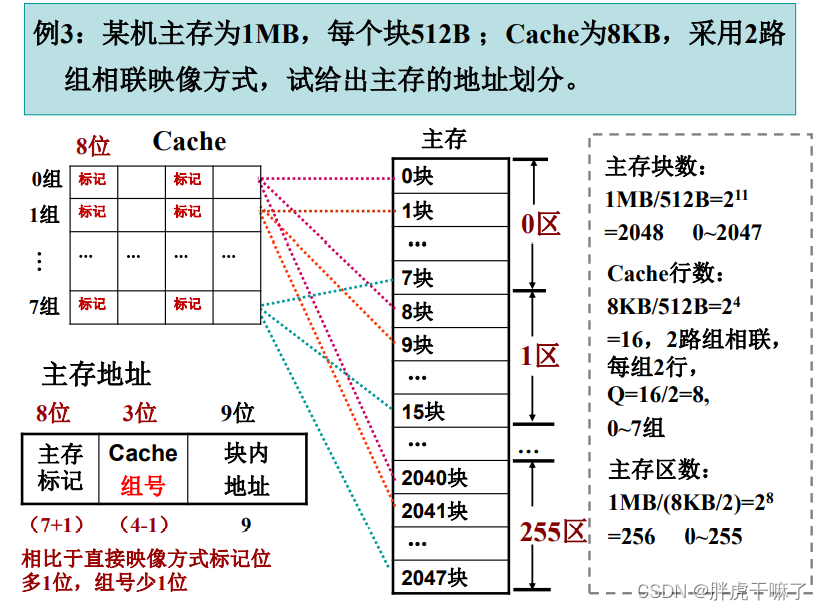

(3) Group associative image

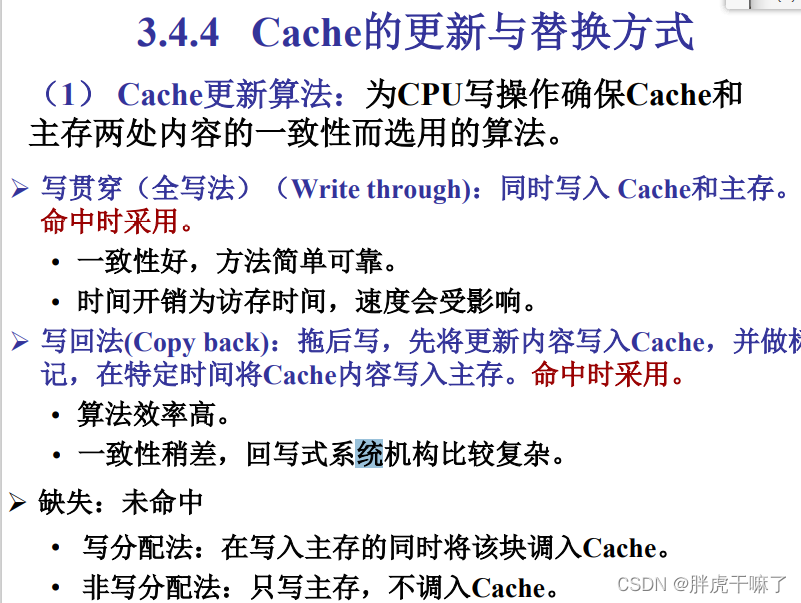

3.4.4 Cache update and replacement methods

(1) Cache update algorithm

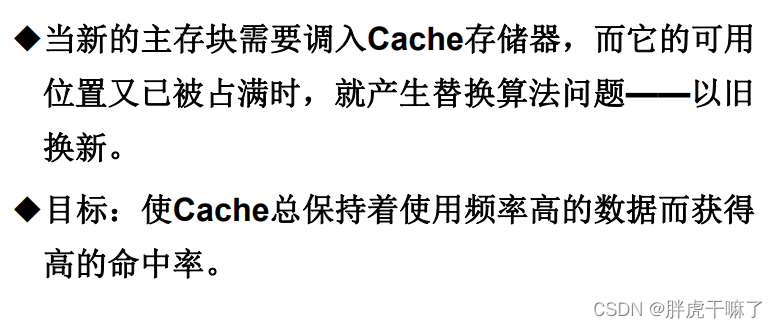

(2) Cache replacement algorithm

Commonly used replacement algorithms:

-

Random Replacement Algorithm (RAND)

does not consider the use situation, randomly selects a block from the candidate Cache line to replace, the performance is worse, but the cost is low. -

The first-in-first-out algorithm (FIFO)

sets a history bit in the address conversion table. When replacing, it always replaces the main memory block first transferred into the Cache, which is easy to implement and has low overhead. It cannot correctly reflect the access locality of the program, which may cause a large miss rate. -

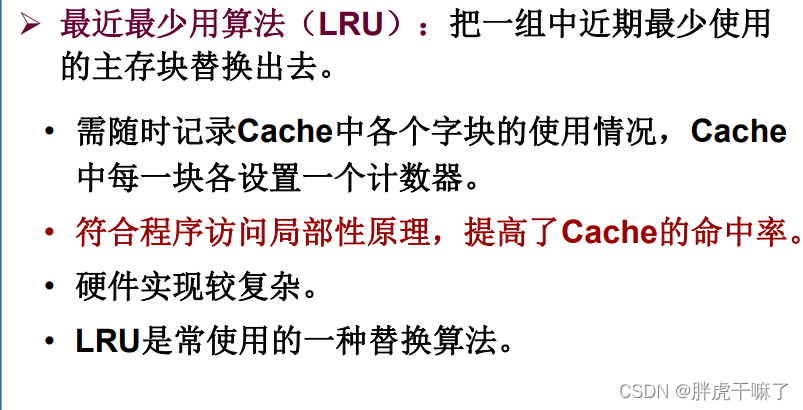

The least recently used algorithm (LRU)

replaces the least recently used main memory block in a group

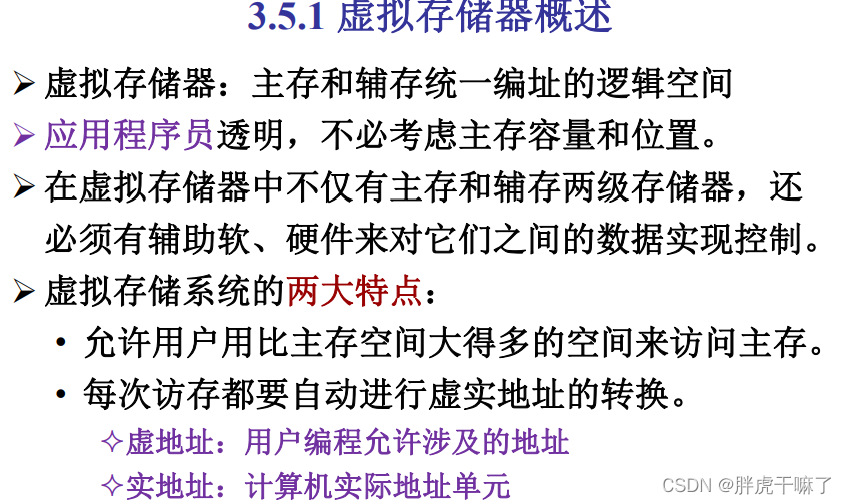

3.5 Virtual memory

Main content: Basic concepts, principles, and functions of virtual storage (TLB and Page)

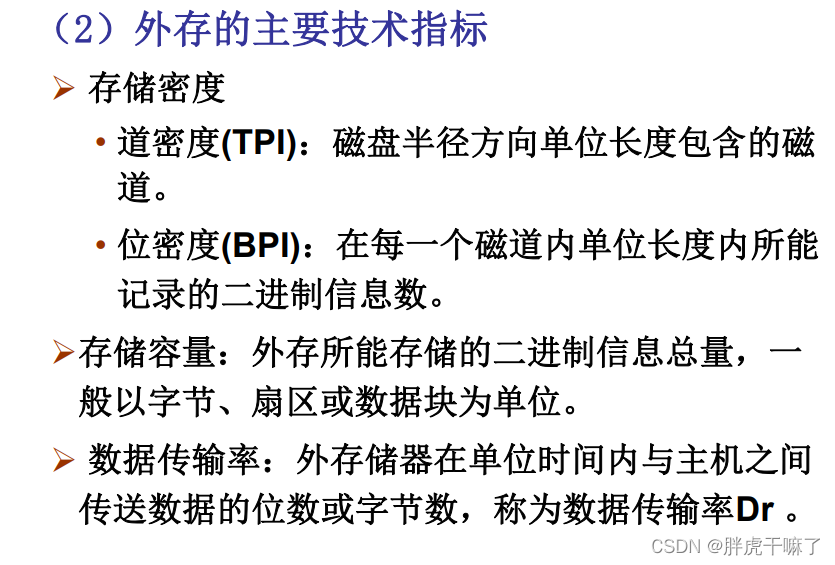

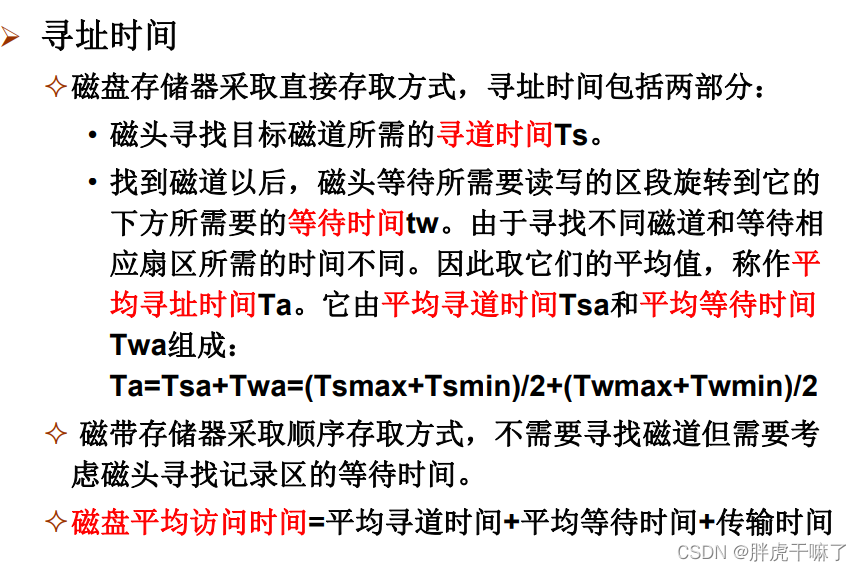

3.6 External storage (auxiliary storage): hard disk, CD

Main content: hard disk capacity, data transfer rate, seek time, average access time and other related calculations