Introduction to FPGA —— Nios II

Introduction

NIOS II is an embedded soft-core processor based on FPGA. In addition to adding the provided peripherals as needed, users can also customize user logic peripherals and user instructions to achieve various application requirements.

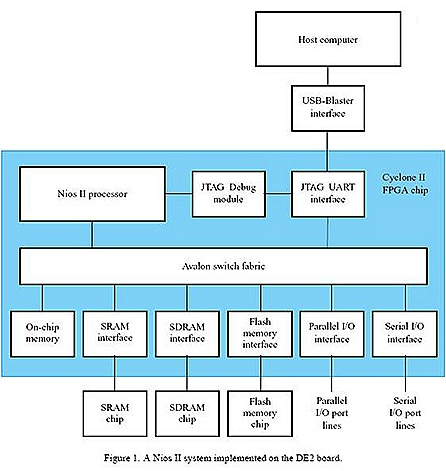

The Nios II processor can be used with many other components to form a complete system. These components include many standard peripherals as well as user-defined peripherals. The Altera DE2 development board contains several components that can be integrated in a Nios II system

The Nios II processor and the interfaces to other chips on the DE2 are implemented in the Cyclone II FPGA. These components are connected through an Avalon switch fabric. The memory blocks of Cyclone II devices provide on-chip memory for the Nios II processor. They can be connected to the processor directly or through the Avalon network. Access SRAM and SDRAM on DE2 through the corresponding interface. The I/O devices used by the system are instantiated as I/O interfaces. The USB cable interface between the host computer and the DE2 is provided by a special JTAG UART interface. This interface circuit and its corresponding software are called USB_Blaster. Another module called JTAG Debug is used to enable the host to control the Nios II processor. In this way, operations such as downloading programs into memory, starting and stopping execution, setting program breakpoints, and collecting real-time data can be performed.

Since every part of the Nios II system implemented in the FPGA is defined by a hardware description language, a skilled user can write and implement any part of the system. This is a tedious and time-consuming task. So, we use the SOPC Builder in the Quartus II software, we only need to select the required components and specify the parameters to realize the target system.

The development process of user-customized SOPC Builder components

-

specify hardware features

-

Specifies the API for the microprocessor to access and control the hardware

-

Define an AVALON interface: provide correct control mechanism, sufficient throughput performance

(4) Use VHDL or Verilog to write hardware design

(5) Separate test hardware design

(6) Write the C header file and define the register mapping

(7) Use the component editor to package hardware and software files into one component

(8) The instantiated component is a module of the SOPC system

(9) Register-level access to test components using the NIOSII processor

(10) Write the driver of the component

(11)反复改进元件的设计:硬件、软件、元件更新

(12)编译完整的包含一个或多个该元件的SOPC系统

(13)执行系统级的验证,若必要,进行反复设计

(14)完成元件设计,发布共享元件

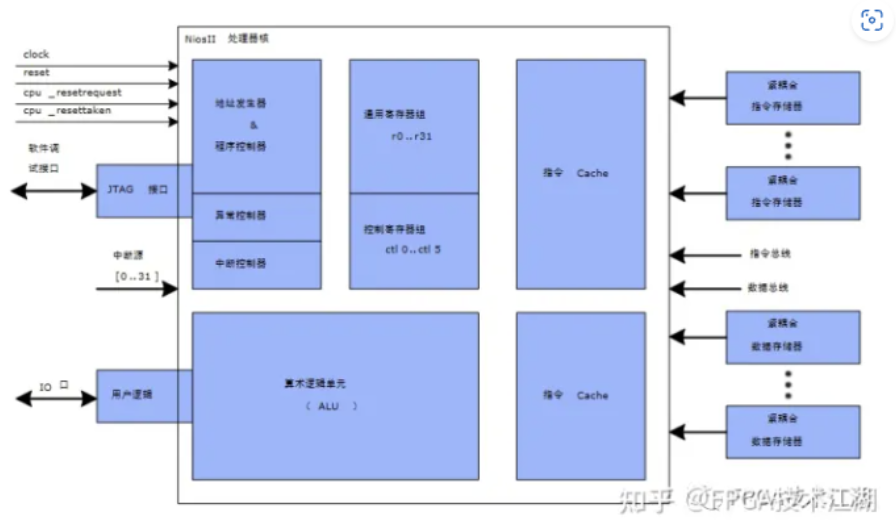

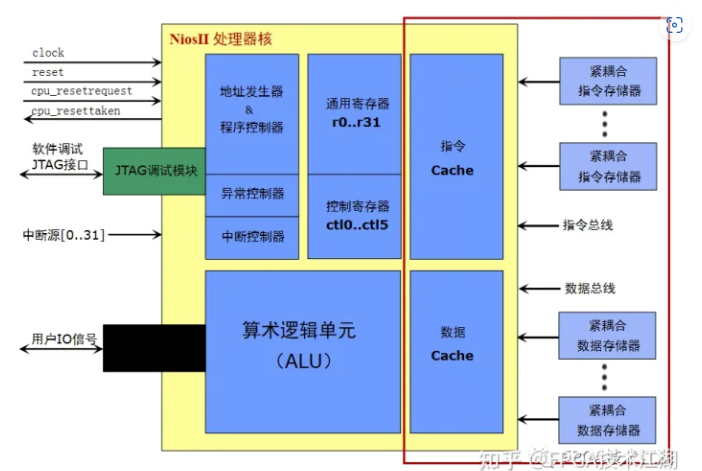

Nios II 处理器结构

Nios II 是一种软核(Soft-Core)处理器。

所谓软核,是指未被固化在硅片上,使用时需要借助EDA软件对其进行配置并下载到可编程芯片(比如 FPGA )中的IP核。软核最大的特点就是可由用户按需要进行配置。

1) NIOSⅡ 处理器采用流水线技术、单指令流的 32 位通用 RISC 处理器

2) 提供全 32 位的指令集、数据总线和地址总线

3) 提供 32 个通用寄存器

4) 提供 32 个外部中断源

5) 提供结果为 32 位的单指令 32X32 乘除法

6) 提供专用指令计算结果为 64 位和 128 位的乘法

7) 可以定制单精度浮点计算指令

8) 单指令桶形移位寄存器

9) 对各种片内外设的访问及与片外外设和存储器的接口

10) 硬件辅助的调试模块,在IDE环境下,可完成开始、停止、断点、单步执行、指令跟踪等基本调试和高级调试功能

11) 基于 GNU C/C++ 工具集和 Eclipse IDE 的软件开发环境

12) ALTERA 公司的 SignalTapⅡ 逻辑分析仪,实现对指令、数据、FPGA设计中的逻辑信号进行实 时分析

13) 所有 NISOⅡ 处理器均兼容的指令系统

14) 高达 218DMIPS 的性能

Nios II 处理器特性概览

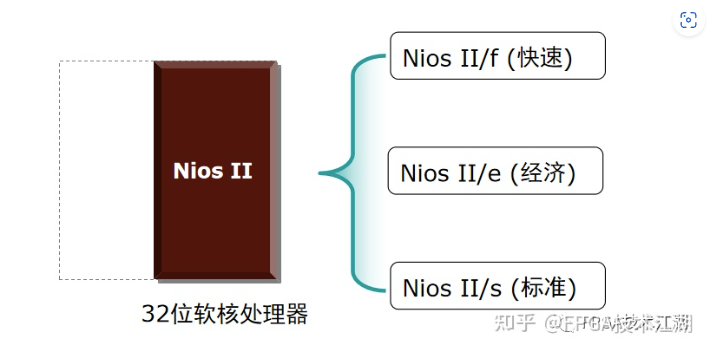

要实现目标系统,Nios II处理器有许多特性需要配置。3种不同的配置可实现处理器:

Nios II/f 是高性能的版本。它有很多配置,可用来优化处理器的性能。

Nios II/s 是标准版本,需要较少的资源,性能也有所降低。

Niso II/e 是经济版,使用最少的资源,可配置的特性也最少。

Nios II 处理器是精简指令架构(RISC)。其算术和逻辑运算的操作数在通用寄存器执行。

通过 Load 和 Store 指令在内存和寄存器之间传送数据。

Nios II 处理器的字长为 32 bits。所有的寄存器都是 32 bits。32-bit 的字节地址可用从小到大或从大到小的风格赋值。在配置时,用户可能会选择一种赋值风格。本文使用从小到大的风格。

Nios II 架构使用单独的指令和数据总线,通常叫做哈佛架构。

Nios II 处理器可能以以下3种模式操作:

-

管理模式 ——允许处理器执行所有的指令和功能。当处理器复位后,进入这种模式

-

用户模式——这种模式的意图是防止某些用于系统进程的指令的执行。在这种模式,某些特性不可用

-

调试模式——用于软件调试工具,比如设置断点和观测点

应用程序可在用户模式或管理模式运行。目前可用的Nios II处理器版本不支持用户模式

Nios II 的寄存器文件

Nios II 的通用寄存器

尽管硬件对寄存器的用法几乎没有规定,但是它们在实际使用过程中还是遵循一些约定俗成的惯例。如果想使用他人的子程序,编译器或操作系统,最好还是遵守这些惯例

我们通过下面的通用寄存器一览表来了解 Nios II 的 32 个通用寄存器:

r0或zero: 总是存放0值,对它读写无效。Nios II没有专门的清零指令,所以常用它来对寄存器清零

r1或at: 这个寄存器在汇编程序中常用作临时变量

r2,r3: 用来传递4个非浮点参数给一个子程序。r3存放返回值的高32位。如果这两个寄存器不够存放需要返回的值,编译器将通过堆栈来传递

r4~r7: 用来传递4个非浮点参数给一个子程序。r4传递第一个参数,r5传递第二个参数,以此类推。如果这四个寄存器不够传递参数,编译器将通过堆栈来传递

r8~r15: 习惯上,子程序可以使用其中的值而不用保存它们。但使用者必须记住,这些寄存器里面的值可能被一次子程序调用改变,所以调用有责任保护它们

r16~r23: 习惯上,子程序必须保证这些寄存器中的值在调用前后保持不变,即要么在子程序执行时不使用它们,要么使用前把它们保存在堆栈中并在退出时恢复。

r24或et: 在异常处理时使用。使用时,可以不恢复原来的值。该寄存器很少作用其它用途。

r25或bt: 在程序断点处理时使用。使用时,可以不恢复原来的值。该寄存器很少作其它用途。

r26或gp: 它指向静态数据区中的一个运行时临时决定的地址。这意味着在存取位于gp值上下32KB范围内的数据时,只需要一条以gp作为基指针的指令即可完成。

r27或sp: 堆栈指针。Nios II没有专门的出栈(POP)入栈(PUSH)指令,在子程序入口处,sp被调整指向栈底部,然后以sp为基址,用寄存器基址+偏移地址的方式来访问栈中的数据。

r28或fp: 帧指针,习惯上用于跟踪栈的变化和维护运行时环境。

r29或ea: 保存异常返回地址。

r30或ba: 保存断点返回地址。

r31或ra: 保存函数返回地址。

Nios II的控制寄存器

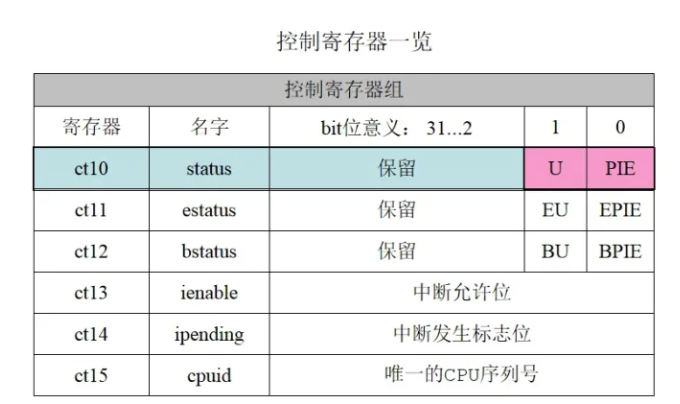

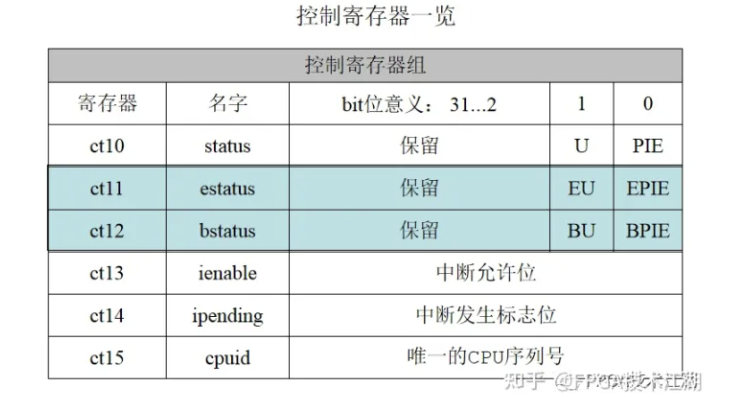

Nios II 的控制寄存器共有 6 个,它们的读/写访问只能在超级用户态( Supervisor Model )由专用的控制寄存器读/写指令( rdctl 和 wrctl )实现

通过控制寄存器一览表,来了解控制寄存器各位的意义:

status—状态寄存器:

-

只有第1位和第0位有意义。

-

第0位PIE—外设中断允许位:

-

1表示允许外设中断;

-

0表示禁止外设中断。

第1位U—反映计算机当前状态:

-

1表示处于用户态(User-mode);

-

0表示处于超级用户态(Supervisor Mode)。

estatus、bstatus—都是status寄存器的影子寄存器:

-

发生断点或者异常时:保存status寄存器的值;

-

断点或异常处理返回时:恢复status寄存器的值。

cpuid—此寄存器中装载着处理器的id号:

该id号在生成Nios II系统时产生。Id号在多处理器系统中可以作为分辨CPU的标识。

ipending—中断发生标志位:

每一位反映一个中断发生。例如:

第0位为1:表示第0号中断发生;

第0位为0:表示第0号中断未发生;

ienable—中断允许寄存器:

每一位控制一个中断通道。例如:

第0位为1:表示允许第0号中断发生;

第0位为0:表示禁止第0号中断发生;

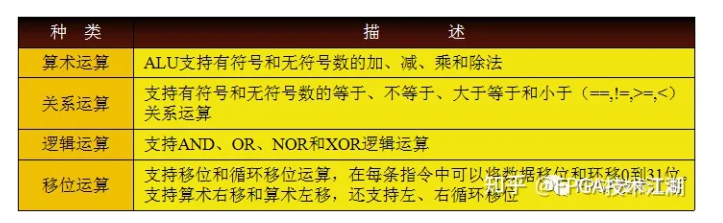

算数逻辑单元(ALU)

Nios II ALU支持的操作:

未实现指令:

NIOSⅡ处理器核未提供硬件乘除法器的实现。

当处理器遇到未实现指令时,处理器会产生一个异常,异常管理器 会调用相应程序用软件模拟未实现指令的操作。NIOSⅡ处理器对未 实现指令的处理对程序员是透明的。

用户定制指令:

NIOSⅡ处理器的ALU直接与用户定制指令逻辑相连,对用户定制指 令的访问等同于系统指令集的指令。

浮点指令:

NIOSⅡ支持符合IEEE STD754-1985规范的单精度浮点指令,浮点指 令以用户定制指令的方式实现。

复位信号

Nios II处理器支持两个复位信号:reset和cpu_resetrequest

reset:是一个强制处理器核立即进入复位状态的全局硬件复位信号。

cpu_resetrequest:是一个可以让CPU复位但不影响Nios II系统其它外设的局部复位信号。

CPU复位后,Nios II处理器将执行下列操作:

-

清除状态寄存器status,使之为0x0;是为了使处理器进入超级用户模式并禁止硬件中断。

-

指令Cache与程序存储器的关联被置为无效,处理器从固态程序存储器(比如Flash)中的reset地址处取得第一条指令;使当前Cache队列无效:是为了保证取指是从复位地址所在的非Cache存储区,而不是当前指令Cache。

-

从复位地址处开始执行程序,复位地址在系统生成时指定。

以下部件的状态在复位后是不确定的:

-

通用寄存器(除zero(r0):总是存放0值);

-

控制寄存器(除status(ct10),被置为0x0);

-

指令和数据存储器。

-

Cache(除与复位地址关联的指令Cache);

-

与CPU相连的各外设,各外设复位后的状态要具体参考各外设的手册;

-

用户指令逻辑在复位后的状态要参看用户指令逻辑的手册或说明。

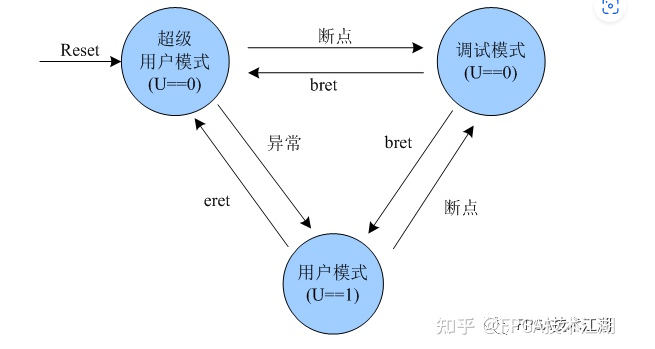

Nios II处理器运行模式

Nios II处理器有3种运行模式:

用户模式(User Mode);

超级用户模式(Supervisor Mode) ;

调试模式(Debug Mode) 。

用户模式:

是超级用户模式功能访问的一个子集,它不能访问控制寄存器和一些通用寄存器。

超级用户模式:

除了不能访问与调试有关的寄存器(bt、ba和bstatus)外,无其它访问限制;

调试模式:

拥有最大的访问权限,可以无限制地访问所有的功能模块。

通常系统程序代码运行在超级用户模式。在V6.0版本以前的Nios II 处理器都不支持用户模式,永远都运行在超级用户模式。

Nios II 处理器3种运行模式切换

异常和中断控制器

异常控制器:

Nios II 体系结构提供一个简单的非向量异常控制器来处理所有类型的异常。

中断控制器:

Nios II体系结构支持32个外部硬件中断,即irq0~irq31。每个中断对应一个独立的中断通道

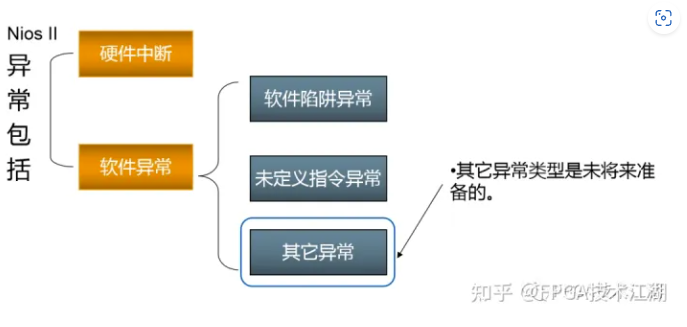

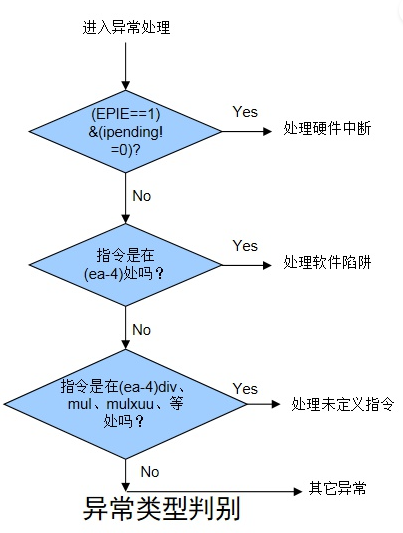

Nios II 的异常处理

异常类型:

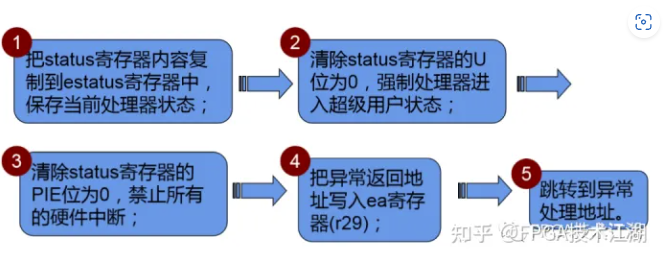

异常硬件处理流程:

当异常发生后,处理器会依次完成以下工作:

异常判别及优先级:

异常的嵌套:

当执行异常返回指令(eret)后,处理器会把estatus寄存器(ctl1)内容复制到status寄存器(ctl0),恢复异常前的处理器状态,然后把异常返回地址从ea寄存器(r29)写入程序计数器。

异常发生时,ea寄存器(r29)保存了异常发生处下一条指令所在的地址。当异常从软件陷阱异常 或未定义指令异常返回时,程序必须从软件陷阱指令trap或未定义指令后继续执行,因此ea寄存器(r29)就是正确的异常返回地址。

异常返回:

如果是硬件中断异常,程序必须从硬件中断异常发生处继续执行,因此必须将ea寄存器(r29)中的地址减去(ea-4)作为异常返回地址。

异常响应时间:

Nios II的非向量仲裁策略,导致了Nios II的异常处理延时会比较大,它是靠提高Nios II处理器的执行速度来弥补这一缺点的。见下表:

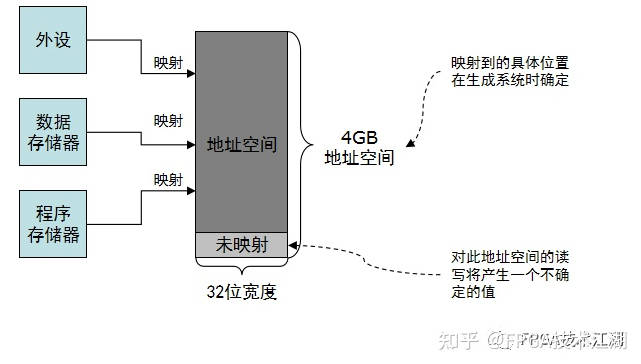

存储器及I/O结构

NIOSⅡ处理器的存储器和I/O结构:

存储器和外设访问

Nios II地址是32位的,允许对4GB地址空间进行访问,但现有的Nios II内核都将地址限制在31位,即2GB地址空间。处理器的数据总线为32位宽度。指令集提供字节,半字(16bit)或字(32位)的读写指令。Nios II结构采用小端模式,对于保存在存储器中的大于8位的数据,最高有效位在高地址

寻址方式

Nios II结构支持以下寻址方式有:

寄存器寻址:所有的操作数都是寄存器,结果保存在寄存器中

移位寻址:寄存器和带符号的16位立即数相加的结果作为地址

立即数寻址:操作数是指令中的常量

寄存器间接寻址:使用了移位寻址,只是移位值是常量0

绝对寻址:范围有限制的绝对寻址使用带有寄存器r0(它的值始终是0x00)的移位寻址来实现。

高速缓存访问

Nios II结构和指令集可以管理数据高速缓存和指令高速缓存。高速缓存管理使用高速缓存指令在软件中实现。指令集可对高速缓存实现初始化、刷新及旁路数据高速缓存的指令操作。

有些Nios II处理器内核支持一种称作31位高速缓存旁路的机制,它根据地址的最高有效位的值来旁路高速缓存。处理器实现的地址空间为2GB,地址的高位控制数据存储器访问的缓存操作。

写入到具有高速缓存的处理器内核的代码可以在没有高速缓存存储器的处理器内核上正确地执行,反过来则不行。在没有高速缓存的系统中,高速缓存管理指令不执行任何操作。

Nios II处理器性能

Nios II 处理器有以下三种类型:

注:关于各处理器的更详细内容请阅读Altera公司的《Nios II Processor Reference Handbook》的Nios II Core Implementation Details部分。

Nios II 处理器内核性能表如下: