SATA

Released in 2000, SATA offers several advantages over the earlier PATA interface, such as reduced cable size and cost (40 or 80 down to 7 wires), native hot-pluggability, higher signal Transfer rates enable faster data transfers and more efficient transfers through the (optional) I/O queuing protocol. Revision 1.0 of the specification was released in January 2003.

The Serial ATA industry compliance specification originates from the Serial ATA International Organization (SATA-IO). The SATA-IO group collaborates to create, review, approve and publish interoperability specifications, test cases and plug-and-play. As with many other industry compliance standards, SATA content ownership is transferred to other industry bodies: primarily INCITS T13 and the INCITS T10 Subcommittee (SCSI), the latter being the T10 subgroup responsible for Serial Attached SCSI (SAS).

The world's first SATA hard drive was the Seagate Barracuda SATA V, released in January 2003.

FPGA implements SATA protocol

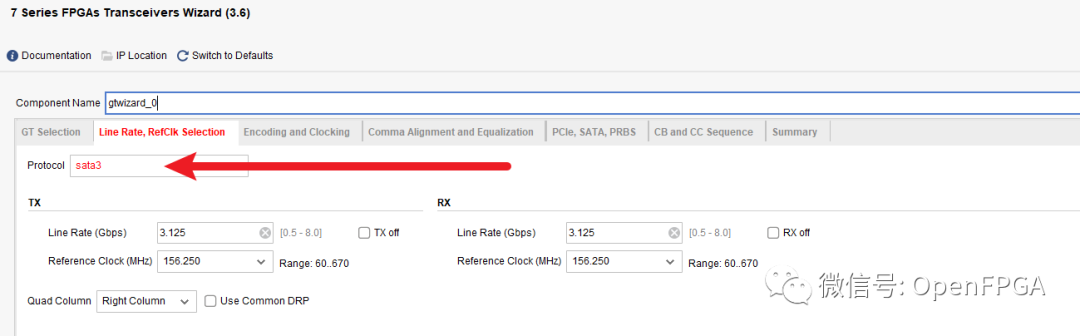

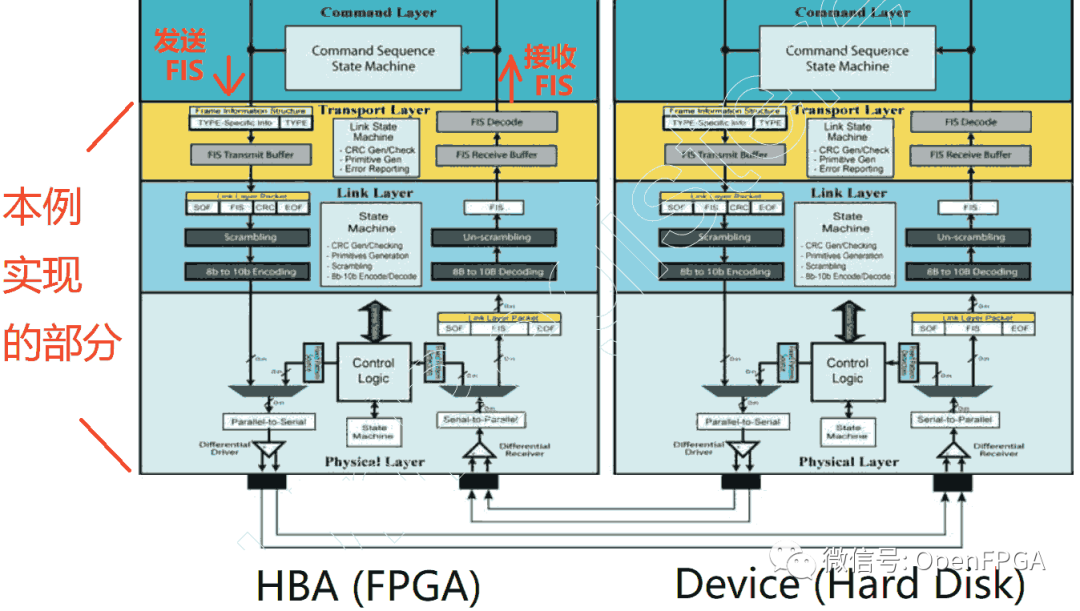

FPGA implements the SATA protocol mainly through SERDES to implement the physical layer, and subsequent other layers need to be written by yourself.

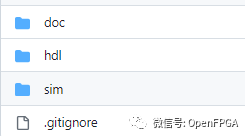

The general content that needs to be implemented for the entire SATA protocol is as follows:

See watermark for image source

See watermark for image source

The following introduces several open source projects that implement the SATA protocol.

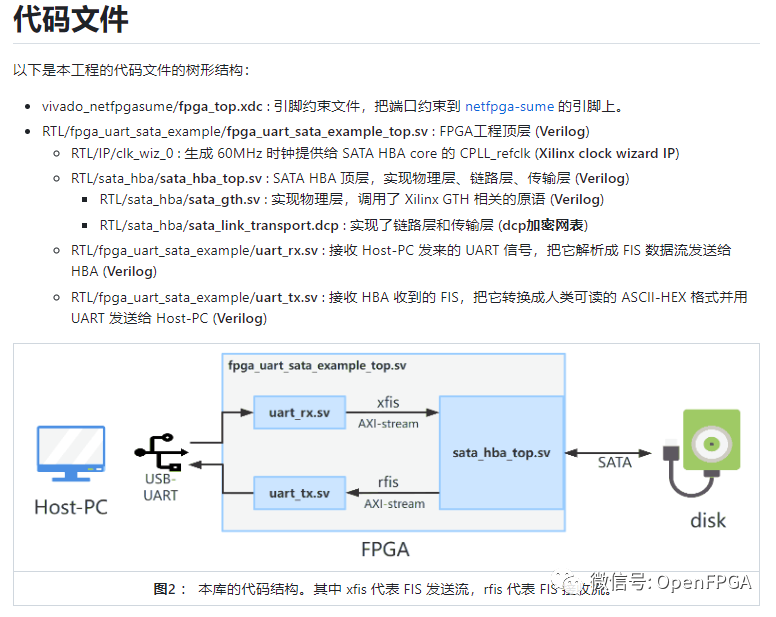

FPGA-SATA-HBA

❝https://github.com/WangXuan95/FPGA-SATA-HBA

❞

introduce

This project is introduced entirely in Chinese, and the protocol is also introduced in extraordinary detail, so I won’t go into details.

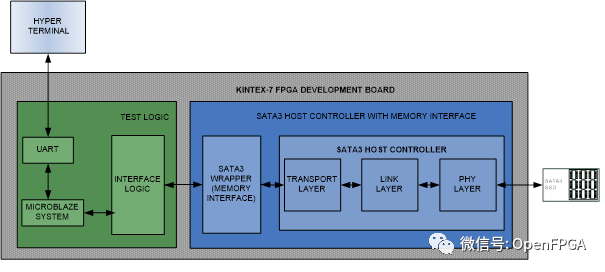

sata3_host_controller/sata_2_host_controller

❝https://github.com/wove2006/sata3_host_controller/tree/master

❞

❝https://github.com/CoreyChen922/sata_2_host_controller

❞

introduce

This is a SATA 3 host controller project. Using this feature, SATA3 SDD/HDD can be read from FPGA logic through a simple memory interface. The controller performance is as follows: Write: 275MBps Read: 519MBps (sequential read and write) (tested on SAMSUNG 250GB SATA3 SSD). FPGA model: Kintex7 xc7k325t (KC705 board).

nysa-sata

❝https://github.com/CospanDesign/nysa-sata

❞

introduce

Sata protocol stack written in Verilog.

For a detailed introduction, the author has a WIKI for viewing:

❝https://github.com/CospanDesign/nysa-sata/wiki

❞

Please note that although the author has open sourced the source code, the open source license is GPL.

sata_controller

❝https://github.com/wove2006/sata_controller

❞

The entire introduction is in Chinese, so I won’t go into details.

sata_ipcore

❝https://github.com/roman-pogorelov/sata_ipcore

❞

SATA IP implemented on Intel FPGA.

books

❝https://github.com/suisuisi/FPGATechnologyGroup/tree/main/SATA_FPGA

❞

Finally, let’s put down some basic knowledge about SATA.

Summarize

Because the SATA part is basically closely related to the bottom layer of FPGA, there are few separate projects to implement it. Several domestic big guys have written several very detailed tutorials. By following the tutorials, you can basically complete the protocol implementation.

Finally, we would like to thank all the big guys for their open source projects, which have benefited us a lot. If you have any interesting projects in the future, you can leave a message in the background or add a message on WeChat. That’s it for today. I am a very excited Sui Suansi, and I look forward to seeing you in the next article.