学过数电应该都知道有38译码器这个东西

就是通过3个输入端,控制8个输出端的状态。2.^3正好是8位。

下面附上代码:

//ujs-lili

module my3_8(a,b,c,out);

input a,b,c;

output [7:0]out;//表示位宽为8bit的输出信号

reg [7:0]out;//或者直接output reg [7:0]out;

always@(a,b,c) //这个跟vhdl中的process类似,a,b,c是敏感变量,只有有变化,就会执行always块中的内容

begin

case({a,b,c}) //注意case里边是{},这个和vhdl中的&相类似,原来a,b,c是bit,现在是合起来3bit

3'b000: out = 8'b0000_0001;

3'b001: out = 8'b0000_0010;

3'b010: out = 8'b0000_0100;

3'b011: out = 8'b0000_1000; //always中的数必须是reg(寄存器)定义的,如果没有reg out那句话,就会报错。

3'b100: out = 8'b0001_0000; //Procedural assignment to a non-register out is not permitted, left-hand side

3'b101: out = 8'b0010_0000;

3'b110: out = 8'b0100_0000;

3'b111: out = 8'b1000_0000;

endcase

end

endmodule

这个程序很简单,但是从中能学到几点:

1.这个程序一开始报错,主要是always中的变量一定要是reg型的。

2.用{ }可以把几个bit的变量合成一个

下面做一个ise的仿真:

//ujs-lili

`timescale 1ns / 1ps //1ns是单位,1ps是精度

module my3_8_tb;

// Inputs

reg a;

reg b;//激励信号

reg c;

// Outputs

wire [7:0] out; //输出信号。

// Instantiate the Unit Under Test (UUT)

my3_8 uut (

.a(a), //信号和端口的连接

.b(b),

.c(c),

.out(out)

);

initial begin

// Initialize Inputs

a = 0;b = 0;c = 0;

// Wait 100 ns for global reset to finish

#100;

a = 0;b = 0;c = 0;

#100;

a = 0;b = 0;c = 1;

#100;

a = 0;b = 1;c = 0;

#100;

a = 0;b = 1;c = 1;

#100;

a = 1;b = 0;c = 0;

#100;

a = 1;b = 0;c = 1;

#100;

a = 1;b = 1;c = 0;

#100;

a = 1;b = 1;c = 1;

#100;

$stop;

// Add stimulus here

end

endmodule

那么这个仿真自己输入的仅仅是initial begin那段:其他都是ise自己给的。

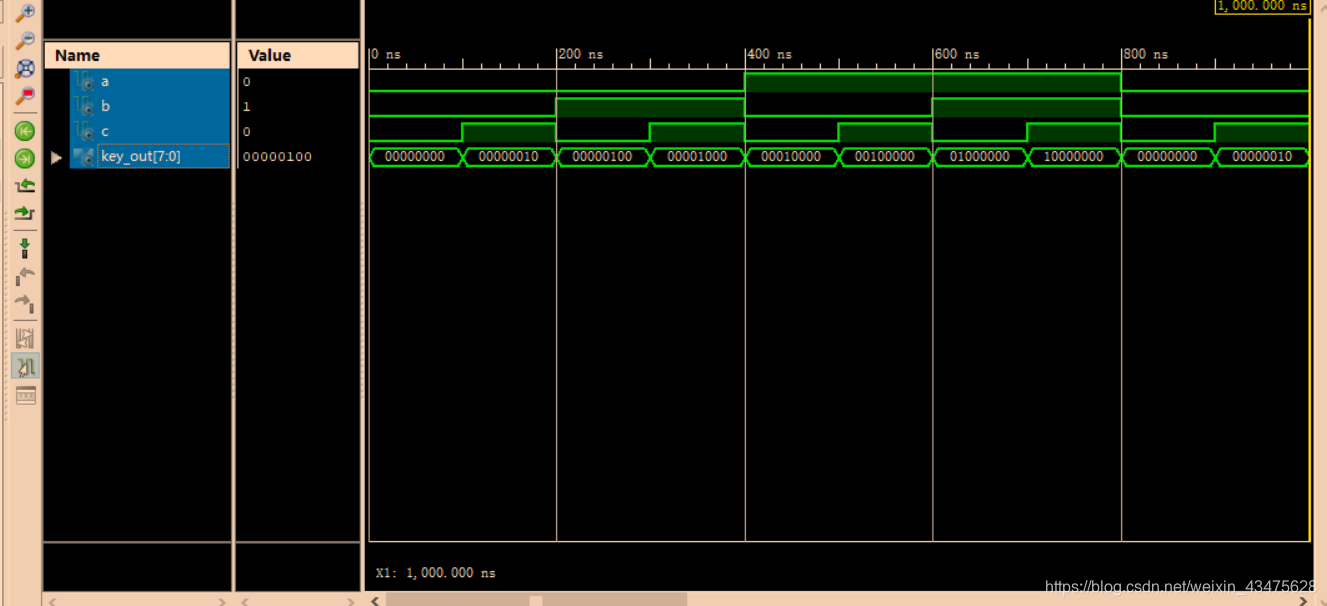

最终得到仿真波形:

--ujs-lili

entity my3_8 is

port(a,b,c:in std_logic;

key_out:out std_logic_vector(7 downto 0));

end my3_8;

architecture Behavioral of my3_8 is

begin

process(a,b,c)

variable d :std_logic_vector(2 downto 0);

begin

d := a&b&c;

case (d) is

when "000" => key_out <= "00000000" ;

when "001" => key_out <= "00000010" ;

when "010" => key_out <= "00000100" ;

when "011" => key_out <= "00001000" ;

when "100" => key_out <= "00010000" ;

when "101" => key_out <= "00100000" ;

when "110" => key_out <= "01000000" ;

when "111" => key_out <= "10000000" ;

when others => null;

end case ;

end process;

end Behavioral;

这个程序很简单,但是有过报错:

1.when others => null; 没有写,少掉了=>

2.d是一个变量,所有:=

3.end process后边的;

4.其实可以更简单,直接把a,b,c定义成d in std_logic_vecrtor(2 downto 0)

仿真程序:

--ujs-lili

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY my3_8_tb IS

END my3_8_tb;

ARCHITECTURE behavior OF my3_8_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT my3_8

PORT(

a : IN std_logic;

b : IN std_logic;

c : IN std_logic;

key_out : OUT std_logic_vector(7 downto 0)

);

END COMPONENT;

--Inputs

signal a : std_logic := '0';

signal b : std_logic := '0';

signal c : std_logic := '0';

--Outputs

signal key_out : std_logic_vector(7 downto 0);

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: my3_8 PORT MAP (

a => a,

b => b,

c => c,

key_out => key_out

);

process

begin

a <= '0';b <= '0';c <= '0';

wait for 100 ns;

a <= '0';b <= '0';c <= '1';

wait for 100 ns;

a <= '0';b <= '1';c <= '0';

wait for 100 ns;

a <= '0';b <= '1';c <= '1';

wait for 100 ns;

a <= '1';b <= '0';c <= '0';

wait for 100 ns;

a <= '1';b <= '0';c <= '1';

wait for 100 ns;

a <= '1';b <= '1';c <= '0';

wait for 100 ns;

a <= '1';b <= '1';c <= '1';

wait for 100 ns;

end process;

END;

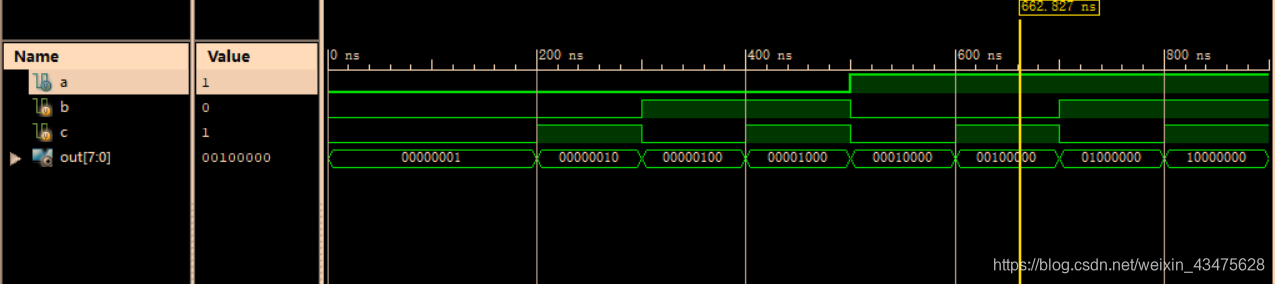

最后的结果和Verilog的一样: