这次来设计一个3线-8线译码器:

##3线-8线译码器的功能;

##如何用always语句、case语句进行逻辑功能的描述。

3线-8线译码器功能:(1)实现逻辑函数; (2)实现存储系统的地址译码; (3)带使能段的译码器可用作数据分配器或脉冲分配器。

##译码是编码的逆过程,3线-8线译码器可以将n位二进制代码可译成2n种电路状态。译码器框图如下所示。

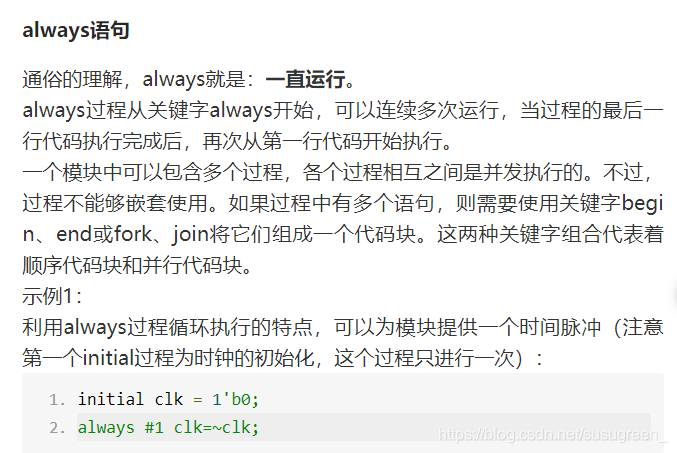

always语句的相关解释:

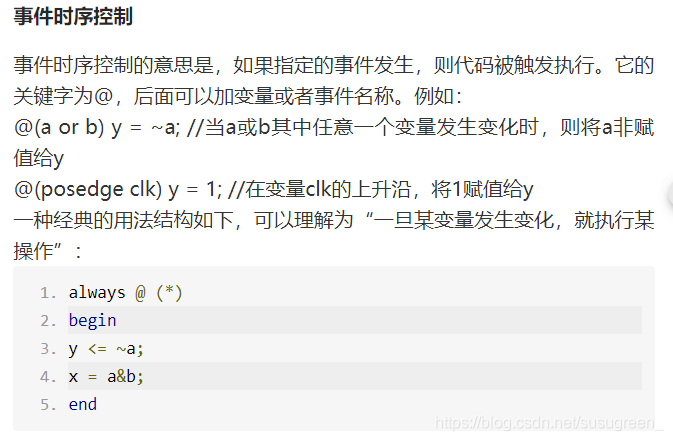

时序控制语句的相关解释:

case语句:

case语句是一个多路条件分支形式,其语法如下:

case(case_expr)

case_item_expr{ ,case_item_expr} : procedural_statement

. . .

. . .

[default: procedural_statement]

endcase

case语句首先对条件表达式case_expr求值,然后依次对各分支项求值并进行比较,第一个与条件表达式值相匹配的分支中的语句被执行。可以在1个分支中定义多个分支项;这些值不需要互斥。缺省分支覆盖所有没有被分支表达式覆盖的其他分支。

最后结束时千万不要忘记‘endcase’!!!

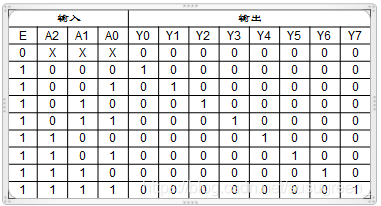

当使能端为0时,8位输出信号全为0;如果一位使能信号为1,则输出高电平有效的译码信号。该译码器真值表如下所示。

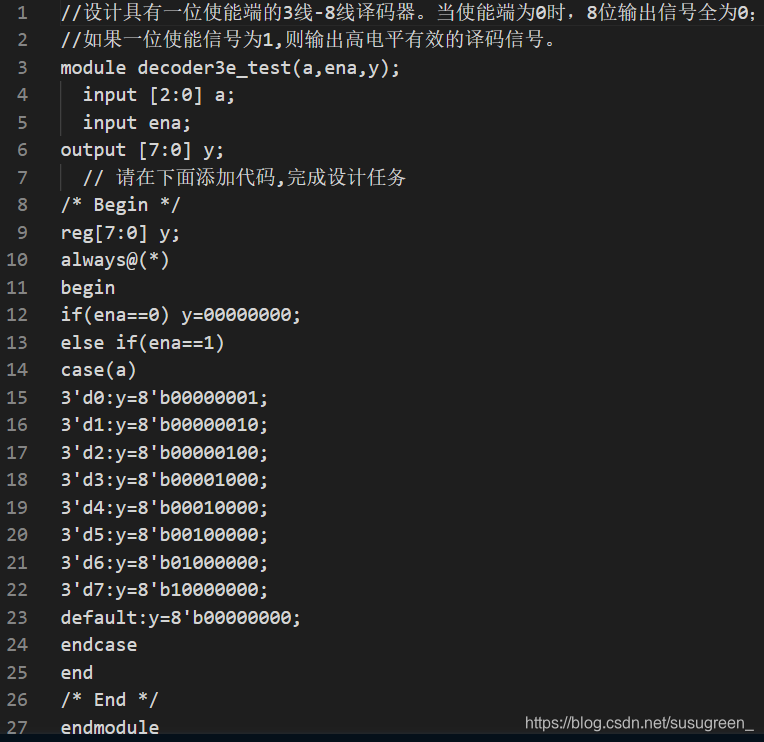

verilog HDL代码文件:

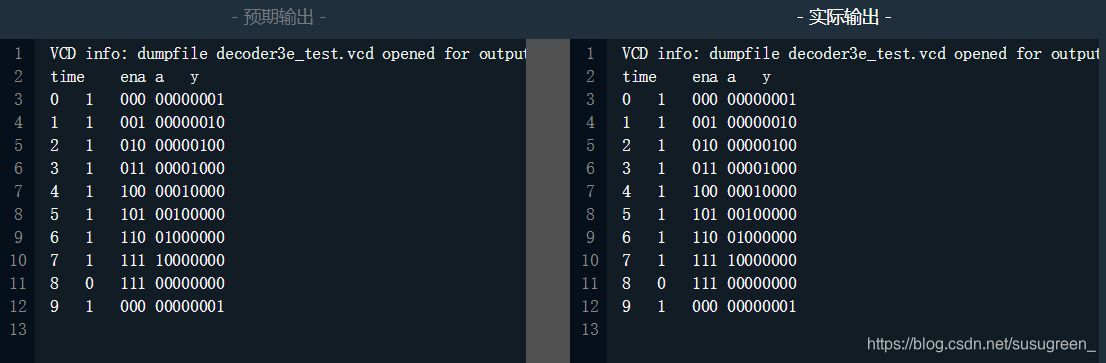

测试集:

以上是简单的关于verilog HDL对3线-8线译码器的设计。

扫描二维码关注公众号,回复:

11532182 查看本文章