VHDL 入门 02编码器 译码器 选择器 移位逻辑

目录

- 1. Combinational Logic Circuits & Building Blocks

- 2.1 Decoder_3_8

- 2.2 Decoder_2_4 with Enable

- 2.3 Decoder Expansion

- 3.1 Binary Encoder

- 3.2 Priority Encoder

- 4.1 Multiplexer/ Data Selector

- 4.2 Mux Expansion

- 5. Shifting

1. 组合逻辑电路与模块化编程思想Combinational Logic Circuits & Building Blocks

本篇主要列出常见模块代码,方便复习。

- 结构化编程Hierarchical Design

分治法 divide-and-conquer - 相关术语 Terminology

MSB -> Most significant bit

LSB -> Least significant bit

2.1 三线-八线译码器 Decoder_3_8

列出真值表,使用 when-else语句组建代码

entity decoder_3_8 is

port( A : in std_logic_vector(2 downto 0);

D : out std_logic_vector(7 downto 0));

end decoder_3_8;

architecture decoder_3_8_arch of decoder_3_8 is

begin

D<="00000001" when A = "000" else

"00000010" when A ="001" else

"00000100" when A = "010" else

"00001000" when A = "011" else

"00010000" when A = "100" else

"00100000" when A = "101" else

"01000000" when A = "110" else

"10000000";

end decoder_3_8_arch;

2.2 带有使能的2线-4线译码器 Decoder_2_4 with Enable

architecture dataflow_arch of decoder_2_4 is

begin

D<= "0001" when A="00" and nE = "0" else

"0010" when A="01" and nE = "0" else

"0100" when A="10" and nE = "0" else

"1000" when A ="11" and nE = "0" else

"0000";

end dataflow_arch;

2.3 译码器扩展 Decoder Expansion

这里使用两个2线-4线译码器扩展成为一个3线-8线译码器

--尝试编写VHDL 代码 目前未进行仿真

-- 有一些冗余的代码,需要进行修改

library ieee;

use ieee.std_logic_1164.all;

------decoder_2_4----------------------------

entity decoder_2_4 is

port( A: in std_logic_vector(1 downto 0);

nE: in std_logic;

D: out std_logic_vector(3 downto 0));

end decoder_2_4;

architecture decoder_2_4_arch of decoder_2_4 is

begin

D <="0001" when A="00" and nE = "0" else

"0010" when A="01" and nE = "0" else

"0100" when A="10" and nE = "0" else

"1000" when A ="11" and nE = "0" else

"0000";

end dataflow_arch;

------decoder_24_38--------------------------

entity decoder_24_38 is

port ( B: in std_logic_vector(2 downto 0);

P: out std_logic_vector(7 downto 0));

nEE: in std_logic;

end decoder_24_38;

architecture decoder24_38_arch of decoder24_38 is

component decoder_2_4 is

port( A: in std_logic_vector(1 downto 0);

nE: in std_logic;

D: out std_logic_vector(3 downto 0));

end component;

signal D1,D2: std_logic_vector(3 downto 0);

begin

decoder1: decoder_2_4 port map(A(0)=>B(2), A(1)=>"0", nE=>nEE, D(0)=>D1(0) ,D(1)=>D1(1),D(2)=>D1(2),D(3)=>D1(3) );

decoder2: decoder_2_4 port map(A(0)=>B(0), A(1)=>B(1), ne=>nEE,D(0)=>D2(0),D(1)=>D2(1),D(2)=>D2(2),D(3)=>D2(3) );

P(0)<= D1(0) and D2(0);

P(1)<= D1(0) and D2(1);

P(2)<= D1(0) and D2(2);

P(3)<= D1(0) and D2(3);

P(4)<= D1(1) and D2(0);

P(5)<= D1(1) and D2(1);

P(6)<= D1(1) and D2(2);

P(7)<= D1(1) and D2(3);

end decoder24_38_arch;

3.1 八线-三线编码器 Encoder

-----------encoder_8_3---------------

entity encoder_8_3 is

port( D: in std_logic_vector(7 downto 0);

A: out std_logic_vector(2 downto 0));

end encoder_8_3;

architecture arch of encoder_8_3 is

begin

A(0)<= D(1) or D(3) or D(5) or D(7);

A(1)<= D(2) or D(3) or D(6) or D(7);

A(2)<= D(4) or D(5) or D(6) or D(7);

end arch;

3.2 优先编码器 Priority Encoder

architecture arch of pri_encoder_4_2 is

begin

A<="11" when D(3)='1' else

"10" when D(2)='1' else

"01" when D(1)='1' else

"00" ;

V<= D(0) or D(1) or D(2) or D(3);

end arch;

4.1 数据选择器 Multiplexer/ Data Selector

- 采用 when-else 语句书写

--1 bit mux4-----------------------------------------------------

entity mux4 is

port( S: in std_logic_vector(1 downto 0);

D: in std_logic_vector(3 downto 0)

F out std_logic);

end mux4;

architecture mux4_arch of mux4 is

begin

F<= D(0) when S="00" else

D(1) when S="01" else

D(2) when S="10" else

D(3) when S="11" else

'0';

end mux4_arch;

- 采用 with-select-when 语句书写

----8bit mux4--------------------------------------------------

entity mux4_8 is

port ( D3, D2, D1, D0: in std_logic_vector(7 downto 0);

S : in std_logic_vector(1 downto 0);

Y : out std_logic_vector(7 downto 0));

end mux4_8;

architecture arch of mux4_8 is

begin

with S select

Y <= D3 when "11",

D2 when "10",

D1 when "01",

D0 when others;

end arch;

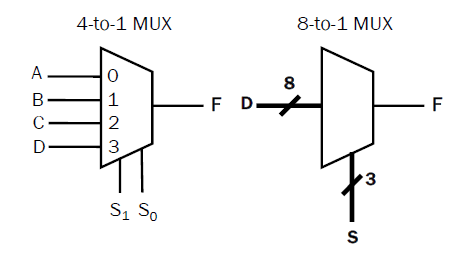

4.2 选择器扩展 Mux Expansion

使用5个mux4构成mux16

先是4个mux4并行,十六选四

再进行四选一

entity mux16 is

port (D: in std_logic_vector(15 downto 0);

S: in std_logic_vector(3 downto 0);

Y: out std_logic);

end mux16;

architecture arch of mux16 is

component mux4 is

port (D: in std_logic_vector(3 downto 0);

S: in std_logic_vector(1 downto 0);

Y: out std_logic);

end component;

signal X: std_logic_vector(3 downto 0);

begin

L1_M3: mux4 port map (D(15 downto 12), S(1 downto 0), X(3));

L1_M2: mux4 port map (D(11 downto 8), S(1 downto 0), X(2));

L1_M1: mux4 port map (D( 7 downto 4), S(1 downto 0), X(1));

L1_M0: mux4 port map (D( 3 downto 0), S(1 downto 0), X(0));

L2_M1: mux4 port map (X, S(3 downto 2), Y);

end arch;

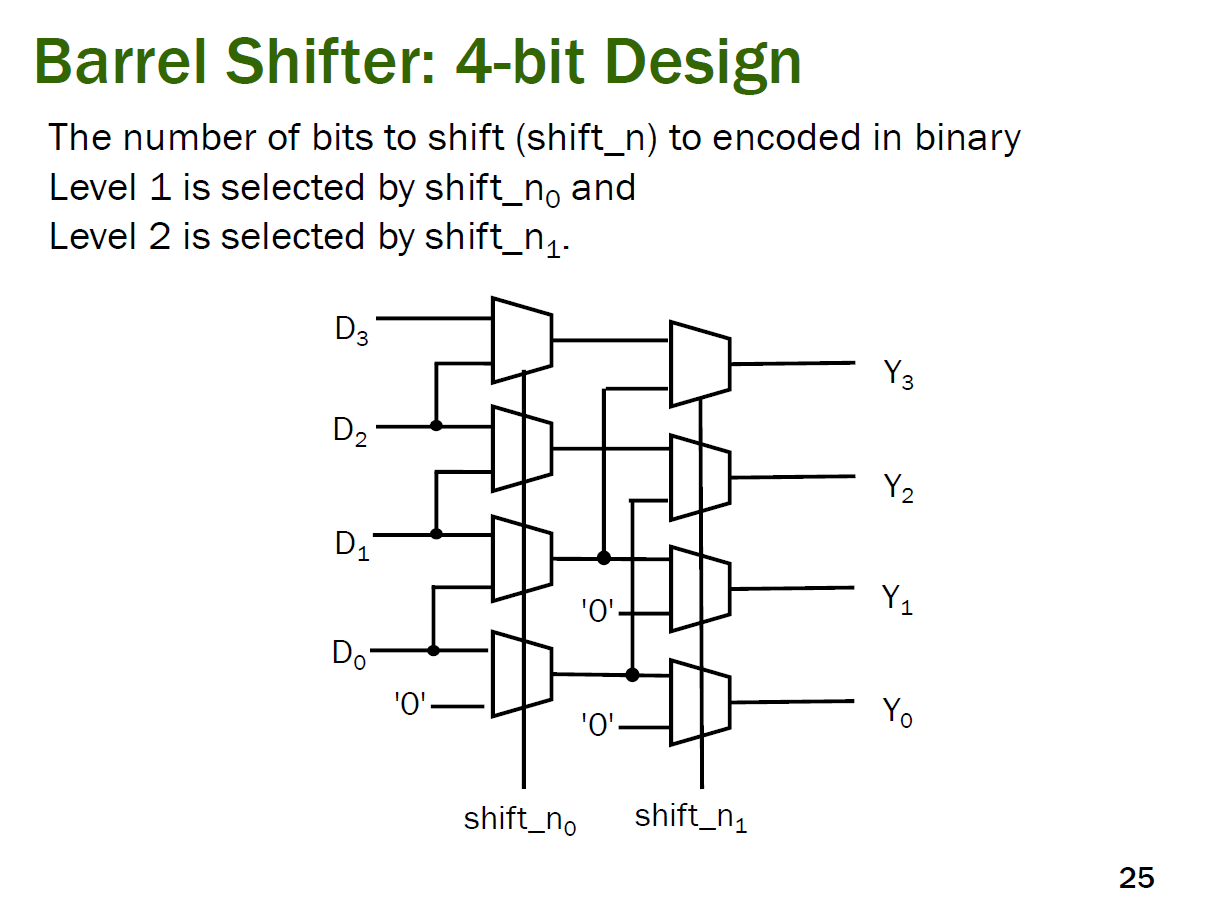

5. 移位器 Shifter

Barrier Shifter

entity barrel4 is

port ( D: in std_logic_vector(3 downto 0);

shift_n: in std_logic_vector(1 downto 0);

Y: out std_logic_vector(3 downto 0));

end barrel4;

architecture arch of barrel4 is

component mux2 is

port (A, B, S: in std_logic; -- Y <= A when S = '0' else B;

Y: out std_logic);

end component;

signal D1, D0, X1, X0: std_logic_vector(3 downto 0);

begin

MUX2_GEN: for i in 3 downto 0 generate

L1: mux2 port map (D0(i), D1(i), shift_n(0), X0(i));

L2: mux2 port map (X0(i), X1(i), shift_n(1), Y(i));

end generate MUX2_GEN;

D0 <= D;

D1 <= D0(2 downto 0) & '0'; -- shifted bits level 1

X1 <= X0(1 downto 0) & "00"; -- shifted bits level 2

end arch;