38译码器

| a | b | c | out |

|---|---|---|---|

| 0 | 0 | 0 | 0000 0001 |

| 0 | 0 | 1 | 0000 0010 |

| 0 | 1 | 0 | 0000 0100 |

| 0 | 1 | 1 | 0000 1000 |

| 1 | 0 | 0 | 0001 0000 |

| 1 | 0 | 1 | 0010 0000 |

| 1 | 1 | 0 | 0100 0000 |

| 1 | 1 | 1 | 1000 0000 |

新建工程(放在prj文件夹下) ——》工程名称(以英文开头) my3_8 ——》添加代码next ——》选择开发板对应器件 ——》工具选择 Modelsim-Altera 语言选择 Verilog HDL ——》工程创建完毕

~~

NEW——》Design FIles ——》Verilog HDL File ——》保存文件 路径rtl下 名字默认

逻辑设计

module my3_8(a,b,c,out); //定义模块名称(与文件一致) 定义端口列表

input a; //输入端口a(位宽1)

input b; //输入端口b(位宽1)

input c; //输入端口c(位宽1)

output [7:0]out; //输出端口out(位宽8) //你看上面的表格

always@(a,b,c)begin

//括号内 叫敏感列表 括号里 任意信号发生变化后都会执行always块内的内容

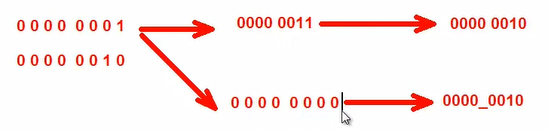

case({a,b,c}) // 花括号的意思就是将abc三个一位信号拼接 组成一个三位信号

//3'b三位二进制 8'b 为八位二进制

3'b000:

out=8'b0000_0001; //下划线为占位符无实际含义

3'b001:

out=8'b0000_0010;

3'b010:

out=8'b0000_0100;

3'b011:

out=8'b0000_1000;

3'b100:

out=8'b0001_0000;

3'b101:

out=8'b0010_0000;

3'b110:

out=8'b0100_0000;

3'b111:

out=8'b1000_0000;

//default://由于所有情况都已经写完了default已经没有东西可以写了

endcase //case需要与endcase像对应

end

endmodule

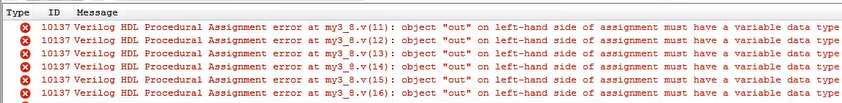

——》进行分析与综合

——》报错

~~无论在最后电路中生成的是线网型还是寄存器型 只要是在always块中我们对其进行过赋值操作的我们都需要将其定义成reg寄存器类型

output [7:0]out; 改为 output reg [7:0]out;

——》分析与综合 成功(逻辑设计完成)

——》

开始testbench

testbench是一张桌子 上面放着待测试模块 信号源 以及观测信号的示波器

新建 Verilog HDL File ——》保存 在 testbench下 ——》my3_8_tb

`timecale 1ns/1ns //步长1ns 精确度1ns

moudle my3_8_tb;

//3:定义激励信号与观测信号 激励信号需要是寄存器型的 观测信号是线网型的

reg a1;

reg b1;

reg c1;

wrie [7:0]out1

my3_8 u1( //1:复制粘贴待测试模块名 并加加上标号 这是模块例化

.a(a1),

.b(b1), //4:在括号内填入3中定义的激励信号与观测信号 进行连接

.c(c1),

.out(out1)

//2:端口名前面加上点 后面加上小括号 信号的例化

);

//定义 initial 块 产生激励信号

initial begin

a = 0; b = 0; c = 0;

#200;

a = 0; b = 0; c = 1;

#200;

a = 0; b = 1; c = 0;

#200;

a = 0; b = 1; c = 1;

#200;

a = 1; b = 0; c = 0;

#200;

a = 1; b = 0; c = 1;

#200;

a = 1; b = 1; c = 0;

#200;

a = 1; b = 1; c = 1;

#200;

$stop;

end

endmodule

——》分析与综合

——》连接两个文件

assiments——》setting——》进行设置(详细过程与第一篇笔记相同)

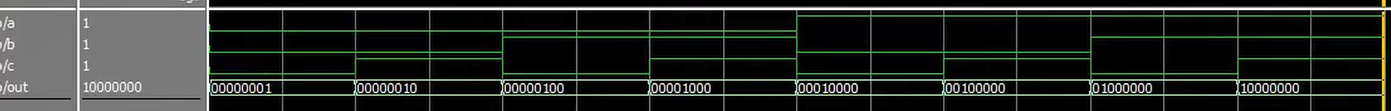

——》开始仿真

——》

与设计相一致 (前仿真完成)

——》开始全编译

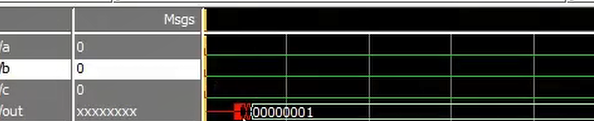

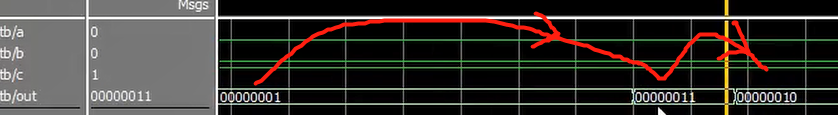

——》进行后仿真(门级仿真)——》选择环境——》开始

在刚上电的时候 输出out 出现了 短暂的未知状态

在两状态切换的过程中 出现了其他暂态

由于真实电路的门级间传输延迟!

PS:如果修改了代码想再次进行仿真 需要先关闭仿真工具

416译码器的道理也相同

~(a,b,c,d,out)