1.如何建立工程。

(1)new project

一堆…finish

(2)点到project上右击new source

可以用vhdl和verilog hdl

(3)写代码

module(里面放的是输入输出端口的定义)

之后 定义端口是输入还是输出

如:

input a,b;//这就是输入的端口

(4)端口定义完,开始定义功能

assign是连续赋值语句

assign x = a & b ; 之类

下面是写好的代码:

功能:

首先开关是接地的,开关一旦按下,电位为0;

详细:

二选一多路器:

两个输入,a,b

输入按键按下时,按键为低电平,led灯和a端口状态保持一致。

输入按键未按下时,按键为高led灯和b端口状态保持一致。

这次的学习笔记有参考小梅哥和xlinx fpga 数字电路设计

//ujs-lili

module xiaomeige1(a,b,key_in,led_out);//这个叫定义端口

input a;//输入端口a

input b;//输入端口b,也可以input a,b

input key_in;//按键输入

output led_out;//led控制端口

//先判断为0,就是a,否则就是b

assign led_out = (key_in == 0)? a : b;

endmodule

做完这个可以做仿真用ise自带的仿真软件:

(1)new source

test_fixture

注意名字不能相同,后边加上tb就可以了

代码如下:

//ujs-lili

`timescale 1ns / 1ps //1ns表示基准时间单位,1ps代表仿真精度

module xiaomeige1_tb;

//加载激励源

reg signal_a;

reg signal_b;//测试信号源

reg signal_c;

wire led;//输出线

//例化程序

xiaomeige1 xiaomeige1(

.a(signal_a), //端口接上测试信号源,注意这里是逗号

.b(signal_b),

.key_in(signal_c),

.led_out(led)//端口接上输出线,注意这里没有,或者;

);

//产生初始激励信号

initial begin

signal_a = 0; signal_b = 0; signal_c = 0;

#100; //用来延迟的,100*1ns

signal_a = 0; signal_b = 0; signal_c = 1;

#100;

signal_a = 0; signal_b = 1; signal_c = 0;

#100;

signal_a = 0; signal_b = 1; signal_c = 1;

#100;

signal_a = 1; signal_b = 0; signal_c = 0;

#100;

signal_a = 1; signal_b = 0; signal_c = 1;

#100;

signal_a = 1; signal_b = 1; signal_c = 0;

#100;

signal_a = 1; signal_b = 1; signal_c = 1;

$stop;

end

endmodule

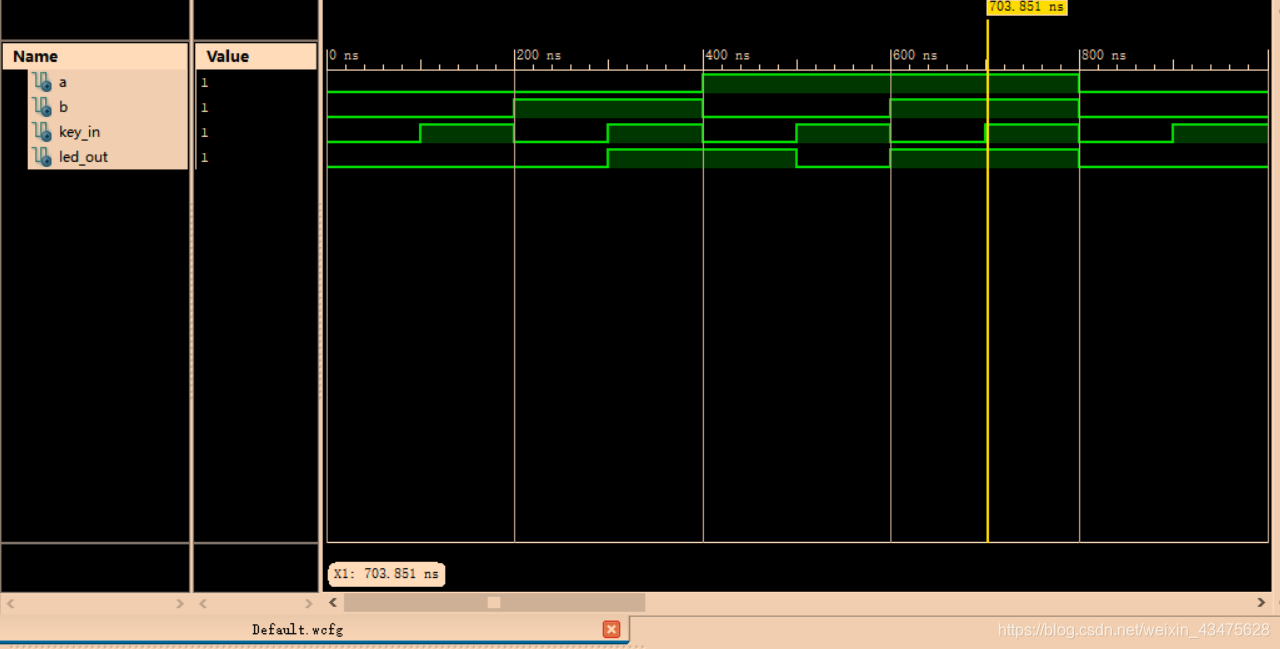

最后得到仿真的时序图:

那么这个程序也可以用vhdl来写:

//ujs-lili

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;--这个开头一定要写的

--定义端口实体

entity xiaomeige1 is

port(

a,b,key_in : in std_logic ;

led_out : out std_logic

);

end xiaomeige1;

architecture Behavioral of xiaomeige1 is

begin

process(a,b,key_in) --敏感信号

begin

if key_in = '0' then --就是有键入,应该和a一样

led_out <= a ;

elsif key_in = '1' then

led_out <= b ;

end if;

end process;

end Behavioral;

那这样代码就写完了,功能完全一样

下面用vhdl进行仿真:

代码如下:

//ujs-lili

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY xiaomeige1_tb IS

END xiaomeige1_tb;

ARCHITECTURE behavior OF xiaomeige1_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT xiaomeige1

PORT(

a : IN std_logic;

b : IN std_logic;

key_in : IN std_logic;

led_out : OUT std_logic

);

END COMPONENT;

--Inputs

signal a : std_logic := '0';

signal b : std_logic := '0';

signal key_in : std_logic := '0';

--Outputs

signal led_out : std_logic;

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

BEGIN

-- 其实就是连接端口和信号

uut: xiaomeige1 PORT MAP (

a => a,

b => b,

key_in => key_in,

led_out => led_out

);

--设置输入信号

inint:process begin

a <= '0'; b <= '0'; key_in <= '0'; --自己设置的8种输入状态

wait for 100ns;

a <= '0'; b <= '0'; key_in <= '1';

wait for 100ns;

a <= '0'; b <= '1'; key_in <= '0';

wait for 100ns;

a <= '0'; b <= '1'; key_in <= '1';

wait for 100ns;

a <= '1'; b <= '0'; key_in <= '0';

wait for 100ns;

a <= '1'; b <= '0'; key_in <= '1';

wait for 100ns;

a <= '1'; b <= '1'; key_in <= '0';

wait for 100ns;

a <= '1'; b <= '1'; key_in <= '1';

wait for 100ns;

end process; --注意这里的;

END ;

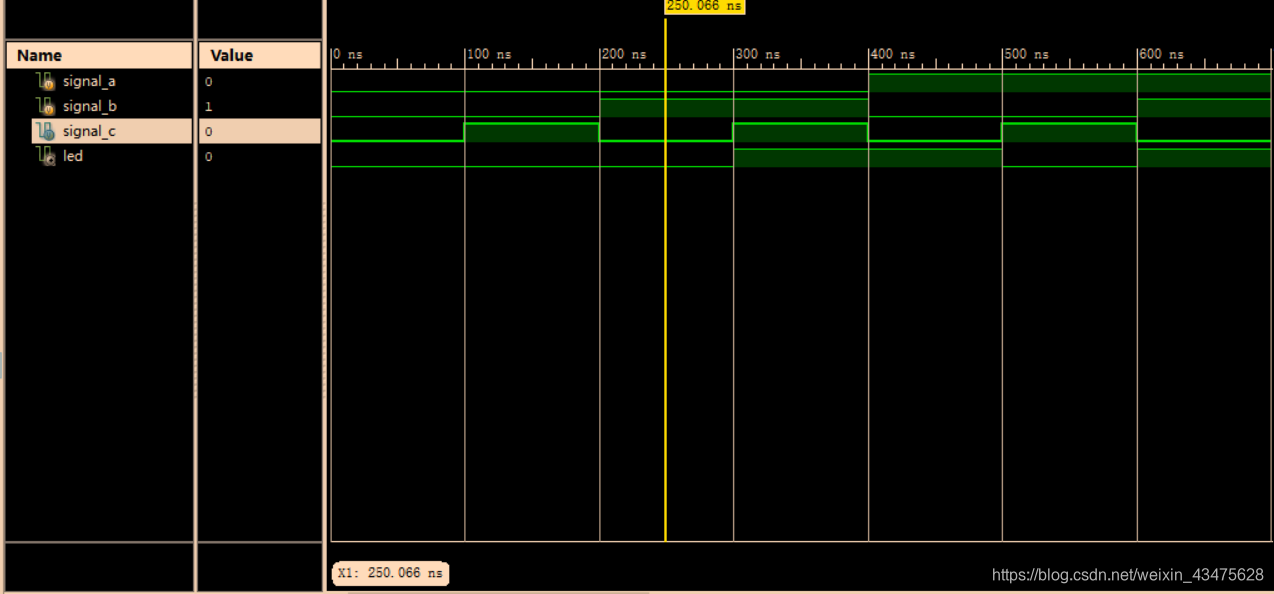

看一下仿真结果: