Verilog HDL 设计显示译码器

逻辑原理:

7 段数码是纯组合电路,通常的小规模专用 IC,如 74 或 4000 系列的器件只能作十进制 BCD 码译码,然而数字系统中的数据处理和运算都是 2 进制的,所以输出表达都是 16 进制的,为了满足 16 进制数的译码显示。

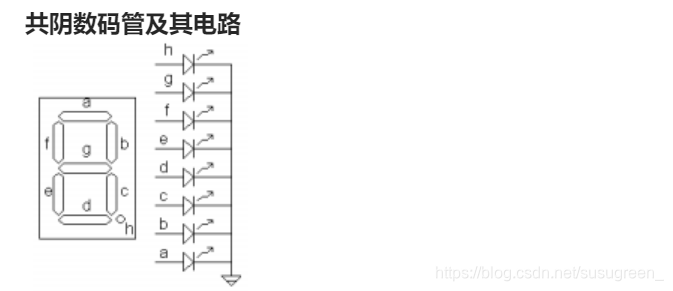

7 段译码器的输出信号 LED7S 的 7 位分别接如下图所示数码管的 7 个段,高位在左,低位在右。例如当 LED7S输出为“1101101”时,数码管的 7 个段: g,f,e,d,c,b,a 分别接 1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。注意,这里没有考虑表示小数点的发光管。

7 段数码显示译码器设计采用 case 语句对数码管的七个段分别进行赋值 0 或 1,实现数字的显示。

共阴数码管:将多只LED的阴极连在一起即为共阴式,而将多只LED的阳极连在一起即为共阳式。

以共阴式为例,如把阴极接地,在相应段的阳极接上正电源,该段即会发光。当然,LED的电流通常较小,一般均需在回路中接上限流电阻。假如我们将"b"和"c"段接上正电源,其它端接地或悬空,那么"b"和"c"段发光,此时,数码管显示将显示数字“1”。而将"a"、“b”、“d”、"e"和"g"段都接上正电源,其它引脚悬空,此时数码管将显示“2”。其它字符的显示原理类同。

以上引自http://www.elecfans.com/yuanqijian/jiekou/2009031430620.html

verilog HDL语言实现:

module decl7s_test(a,led7s);

input [3:0] a;

output [6:0] led7s;

reg [6:0] led7s;

always @(a)

begin

case(a)

4’b0000:led7s=7’b0111111;

4’b0001:led7s=7’b0000110;

4’b0010:led7s=7’b1011011;

4’b0011:led7s=7’b1001111;

4’b0100:led7s=7’b1100110;

4’b0101:led7s=7’b1101101;

4’b0110:led7s=7’b1111101;

4’b0111:led7s=7’b0000111;

4’b1000:led7s=7’b1111111;

4’b1001:led7s=7’b1101111;

4’b1010:led7s=7’b1110111;

4’b1011:led7s=7’b1111100;

4’b1100:led7s=7’b0111001;

4’b1101:led7s=7’b1011110;

4’b1110:led7s=7’b1111001;

4’b1111:led7s=7’b1110001;

endcase

end

endmodule

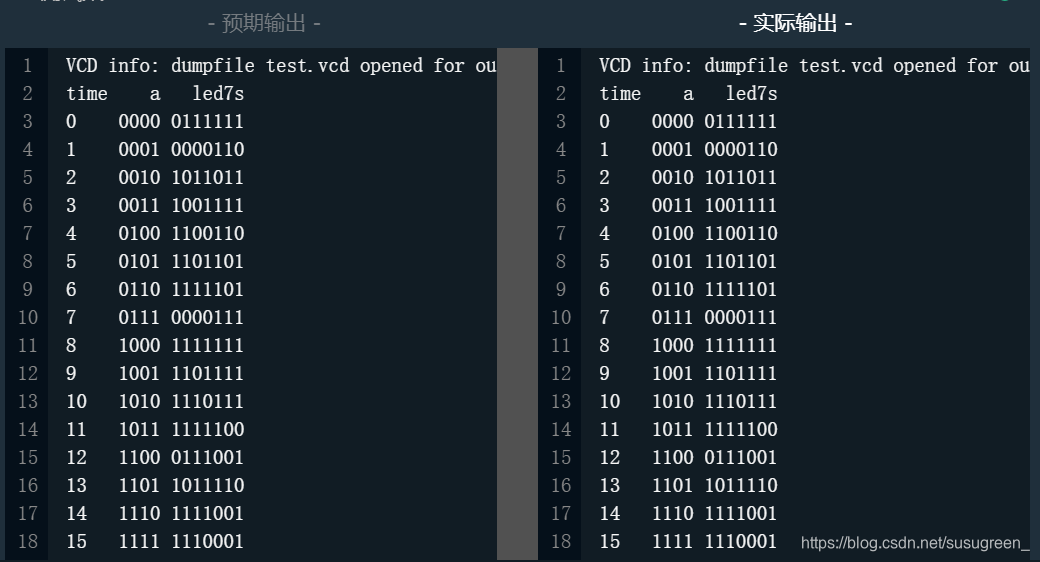

测试集:

上述就是关于verilog HDL对显示译码器中共阴数码管的实现。