写在前面:本博文是华南理工大学电子与信息学院《数字电子技术》Chapter3CMOS门电路的总结与笔记

文章目录

1. CMOS反相器电路结构和工作原理

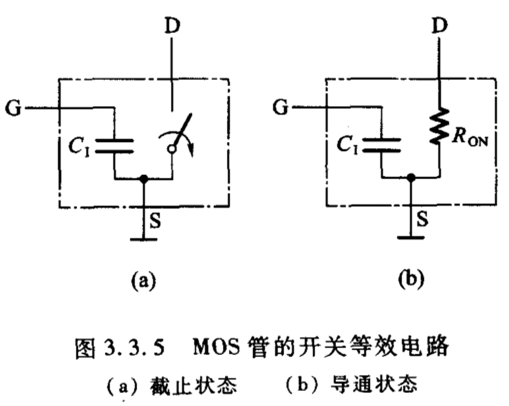

在数电中,我们使用MOS管主要是用它的开关特性

来看看MOS管的开关等效电路(以N沟道增强型MOS管为例)

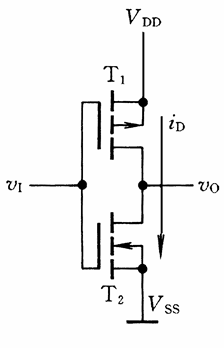

下面我们来看看CMOS反相器的构造:

CMOS反相器主要是由上方的P沟道增强型MOS管和下方的N沟道增强型MOS管构成

在这里记录一个在后面博文中的分析都可以用得上的分析方法:

- 对于P沟道MOS管而言,当g极和s极的电压为低电平时,该管视为导通

- 对于N沟道MOS管而言,当g极和s极的电压为高电平时,该管视为导通

那么下面我们来分析一下这个结构到底怎么就能够被称为反相器了:

首先,

为输入,

为输出,当

为低电平时,下方的增强型N沟道MOS管截止(我们视MOS管截止的等效电阻

非常大,上方的MOS管导通(我们视MOS管的导通电阻

<<

),因此,

的电压就等于下方MOS管截止电阻的电压:

即在输入电压为低电平时,输出电压为高电平

如果反过来,输入电压

为高电平,那么上方MOS管§截止,下方MOS管(N)导通,那么

的电压即为:

即在输入电压为高电平时,输出电压为低电平

| 输入 | 输出 |

|---|---|

| 0(低电平) | 1(高电平) |

| 1(高电平) | 0(低电平) |

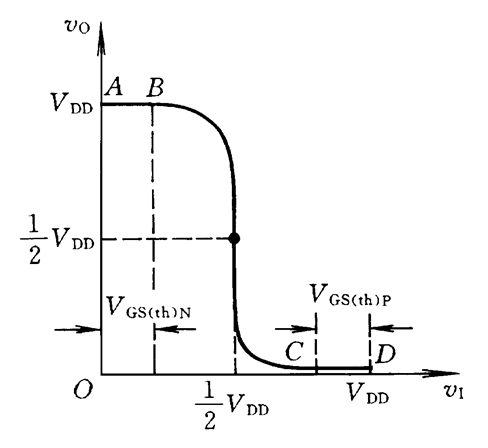

1.1 CMOS反相器电压传输特性和电流传输特性

- AB段:输入为低电平,即 < ,T2截止,T1导通,输出为高电平

- BC段: ,T1,T2同时导通,且当 时,

- CD段:输入为高电平,T2导通,T1截止,输出为低电平

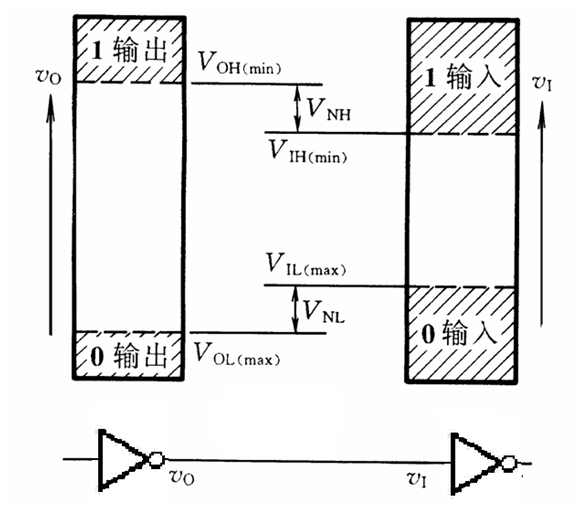

1.2 输入端噪声容限

其实在多级的门电路中,前一级门电路的输出电压就是后一级的输入电压,我们看1.1节的那个电压传输特性图,当输入的低电平电压高于一定的范围时,输出的高电平还不会立刻变化,就还是高电平;当输入的高电平低于一定的范围时,输出的低电平也不会立刻变化,还是维持低电平。那么也就是说门电路对输入的高低电平的范围有一定的“容忍程度”,也叫做噪声容限

输出为高电平时的噪声容限为:

输出为低电平时的噪声容限为:

1.3 CMOS反相器静态输入特性和输出特性

在应用反相器时要加上保护电路:

2.其他类型的CMOS门电路

2.1 各种逻辑功能的CMOS门电路

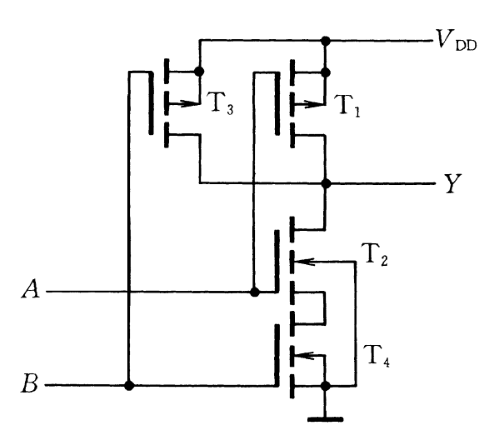

2.1.1 CMOS与非门

上图所示是CMOS与非门电路,我们来分析一下:

通过电路结构可知:

之间只要有一个导通,那么它们所在的支路就导通;而

之间必须要全部导通,它们所在支路才能导通

- 当:A = 0;B = 0时: 导通, 截止,则Y输出高电平1

- 当:A = 1;B = 0时: 导通, 截止,则Y输出高电平1

- 当:A = 0;B = 1时: 导通, 截止,则Y输出高电平1

- 当:A = 1;B = 1时: 导通, 截止,则Y输出低电平0

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

以上是与非门的形式,可以有多个输入,只要保持上图这种样式就行

但是,这样的与非门有三个问题:

首先,我们来计算一下当A,B为不同输入时电路的输出电阻:

当A = 0, B = 0时,T1, T3导通,

当A = 0, B = 1时,T1,T4导通,

当A = 1, B = 0时,T2,T3导通,

当A = 1, B = 1时,T2,T4导通,

通过 上面的分析可见,输入状态的不同居然会导致电路的输出电阻有这么大的差异!

接着,我们发现输入端的数目越多,输出为低电平时串联的导通电阻越多,那么就会导致低电平 越高;输出为高电平时,并联的导通电阻也越多,输出高电平 也提高

最后一个问题:

输入端工作状态的不同对电压传输特性也有一定的影响

2.1.2 CMOS或非门

我们再来看看或非门:

- A = 0,B = 0: 导通, 截止,输出高电平1

- A = 0,B = 1: 导通, 截止,输出低电平0

- A = 1,B = 0时, 导通, 截止,输出低电平0

- A = 1,B = 1时, 导通, 截止,输出低电平0

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

而或非门也存在上述三种的三种问题

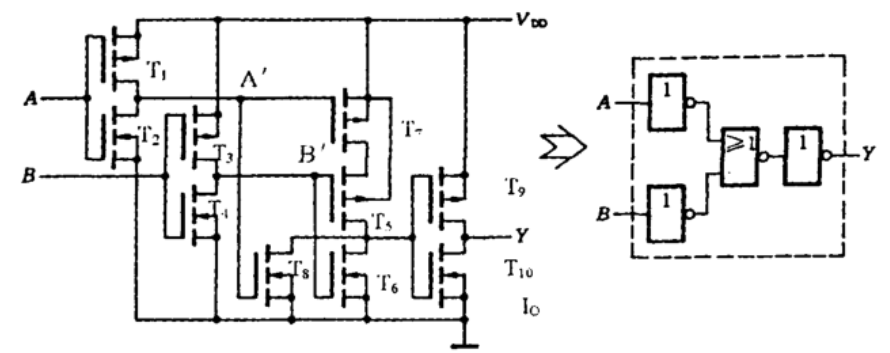

2.1.3 CMOS与非门和或非门三个问题的解决方法及原理

为了解决上述的三种问题,我们给与非门或或非门的输出输出端加上一个反相器:

下图是加了缓冲器后构成的与非门:

然后,我们来分析一下这样做有什么好处:

首先,当我们的的Y’ = 0时,T9导通,T10截止,输出的Y = 1,电路的输出电阻为

输出电压为:

当Y’ = 1时,T10导通,T9截止,输出电阻为:

输出电压

我们发现在加了缓冲器之后,输出电阻就不收输入端数目以及状态的影响了,不管输入端有几个,也不管输入端的状态是什么,输出电阻都为

另外,当Y = 1时,高电平电压也是不变的;Y=0时,低电平也是不变的

我们知道,原电路的三个缺点是由输出端反相器解决的,那么输入端的反相器有什么用?

答案是:用于将或非门变成与非门

Y = (A*B)’

Y = (A+B)’

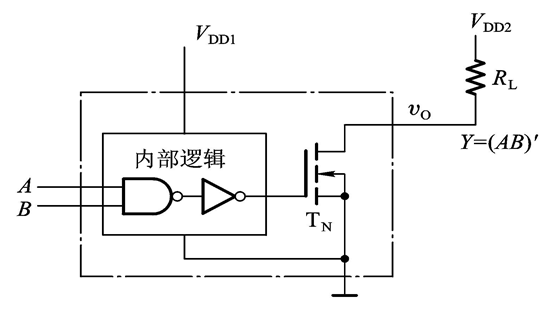

2.2 漏级开路输出门电路(OD门)

首先,我们令 (上拉电阻是必须要的)

中间的内部逻辑部分相当于与门;当A, B只有一个为低电平时,

截止,输出高电平

因此,OD门的逻辑可以描述成:

同时,大家有没有注意到:当我们由于

的取值可以不同于

,因此,我们可以轻松地将输入的高低电平:

转化为输出的高低电平:

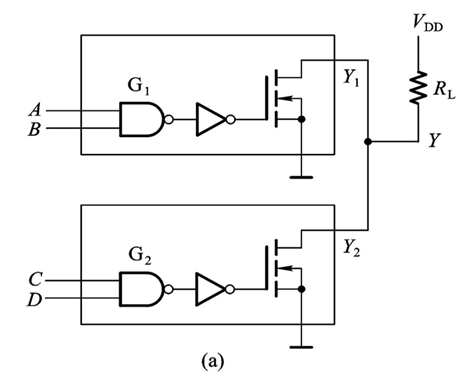

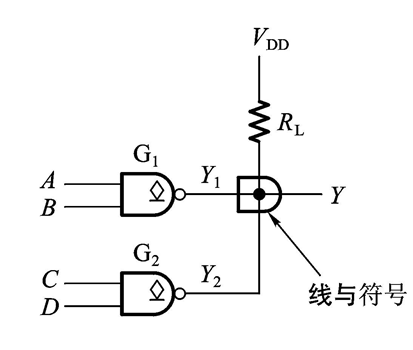

2.2.1 OD门重要应用:实现线与功能

普通的CMOS门电路不能将输出端并联,但是OD门之间可以将输出端并联

我们可以这样分析:Y端的电压既可以是Y1端的电压,也可以是Y2端的电压,取决于那个端电阻小(这样从 出发的电流就会往Y1或Y2支路电阻小的那边流过)

那么,当Y1 = 0,Y2 = 1时,即上方管子导通,下方管子截止,那么从 出发的电流就会流过上方管子(因为 ),因此,输出端Y = Y1 = 0

因此,我们发现:只要Y1或Y2有一个为0,那么输出Y也就等于0

只有当Y1,Y2都为1时(即上下两个管子都截止时)Y才等于1

那么该电路实现的逻辑为:Y = (AB + CD)'

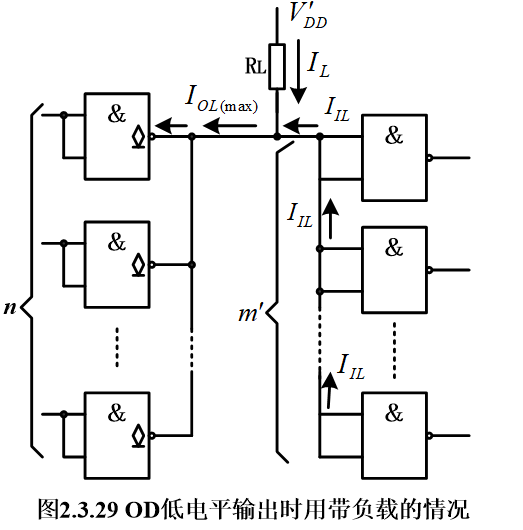

2.2.2 上拉电阻范围的计算

首先,当输出为高电平时:MOS管截止时的漏电流和输入负载们的高电平输入电流同时流入 ,为了保证输出的高电平大于一定值,我们的 不能设置得太大,下面来看看具体的情况:

我们设输出端并联的OD门有n个,输出端高电平输入电流的数目为m,则应有:

即:

归纳:当输出为高电平时,我们方程的书写是以输出高电平的最低电压所驱动的,也就是说我们写这个方程,为的是要求输出端输出的高电平电压大于某一值

当输出为低电平,而且并联的OD门中只有一个门的输出MOS管导通时,如下图所示:

负载电流将全部流入这个管,为了使负载电流不超过MOS管所允许的最大值,我们有:

归纳:当输出为低电平,而且并联的OD门中只有一个门的输出MOS管导通时;方程是由通过MOS管的最大负载电流驱动的,换句话说,就是列方程的目的是要使得流过一支MOS管的电流不超过它所能承受的最大电流

2.2.3 总结:OD门的特点以及应用

特点:

- 通过 和 的不同的取值,来改变输出高电平的大小

- OD门可以承受很大的电压和电流

应用:

- 多个OD门并联实现与或非功能

- 实现电平转换

2.3 CMOS传输门

下面,我们来看看一种挺有意思的逻辑结构:CMOS传输门

我们来分析一下:

- 当C = 0,即C’ = 1时,T1截止,T2也截止,输入与输出之间呈高阻态,传输门截止

- 当C = 1,即C’ = 0时,当

在0~

之间变化时,T1,T2至少有一个是导通的,因此,传输门导通

注意:当传输门导通之后,输入的什么信号,输出的就是什么信号,不变

而且,CMOS传输门是对称的,所以其漏级和源极可以互易使用,属于双向起器件

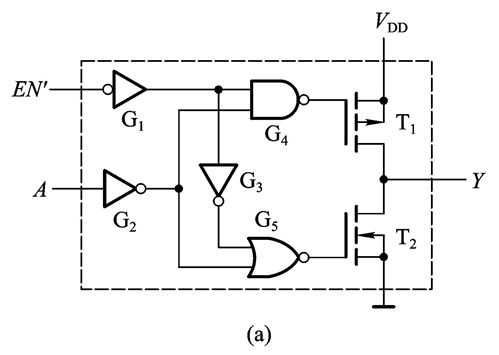

2.4 三态输出的CMOS门电路

我们先来看看图片:

上图是三态输出反相器的电路结构,他总是接在集成电路的输出端,所以也被称为输出缓冲器

至于,这个反相器的判断,在经过上面的学习后应该是没有什么难度了

我们注意一下这个三台控制端EN’

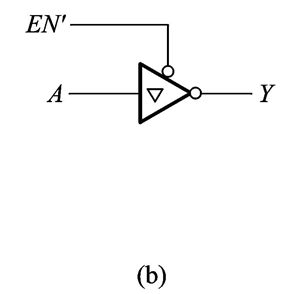

上图是三态输出反相器的符号,我们看到EN‘处有一个小圆圈,那是因为此时EN’表示低电平有效信号,即只有在EN’端为低电平时,电路才能处于正常工作状态

如果没有小圆圈即为高电平有效信号

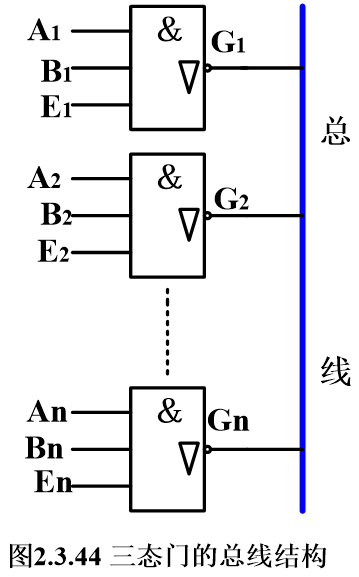

而利用三态输出反相器还能干一些有意思的事情:

- 总线结构

这里的符号的意思是EN’为高电平有效信号,那么我们可以控制每一个输出端的EN’轮流为1,这样不同输入端的信号就能分时传入总线了

- 双向传输

当EN = 1时,G1通,信息从输入端传到总线,EN = 0时,G2通,信息从总线传回门电路

【博主重新复习Chapter 3时的一些再总结】

【1】首先就是上拉电阻范围的计算里面一些注意事项:当我们使用的是CMOS门电路时,负载门的电流数量都是看门电路端口的总数;但是,如果使用的是TTL门电路,在输出为高电平的情况下,负载门的电流数量还是都是看端口的数目;但是当输出为低电平的时候,就分情况了:当使用的是或非门时,电流数量是看或非门的端口数;当使用的是与非门时,电流数量看的就只是与非门的个数了!!

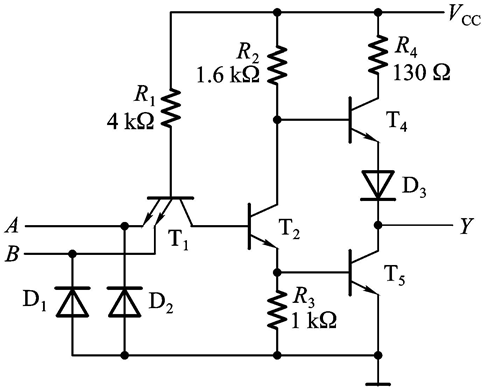

【2】TTL与非门的输入级由多发射极三极管和电阻组成

【3】对MOS门电路多余端不可以悬空,多余端可以接电源的低电平

【4】对于传输门,有小圆圈的那一端使用的是P沟道MOS管,低电平导通

【5】对于三态输出门电路,EN‘处有一个小圆圈,表示此时是低电平有效信号,如果输入为高电平,电路输出高阻态

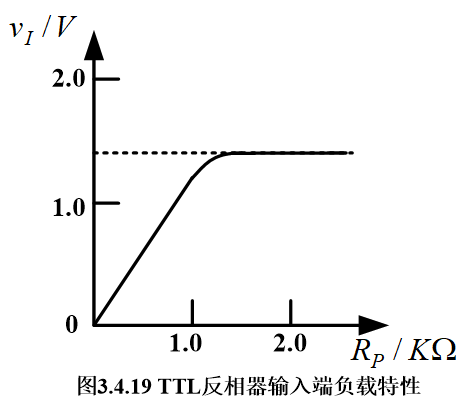

【6】电阻特性(重要!):对于TTL门电路,输入端悬空相当于接高电平,如果输入端和电阻相连之和接地,要看情况,如果是大电阻,那么就相当于接高电平;如果是小电阻相当于低电平,具体电阻大小看下图:

但是CMOS门电路是没有这种特性的,CMOS门电路的输入端接地就相当于接了低电平了

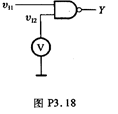

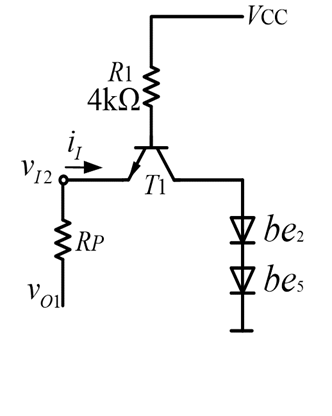

【7】错题收集:下面记录一道有意思的题目:

说明在下列情况下,用万用表测下图中

端得到的电压各位多少?

(1)

悬空

(2)

接低电平(0.2V)

(3)

接高电平(3.2V)

(4)

经51Ω电阻接地

(5)

经10kΩ电阻接地

图中与非门为74系列TTL门电路,万用表使用5V量程,内阻为50kΩ/V

这里首先涉及到了一个知识点:TTL的与非门两个输入之间是会相互影响的,而CMOS的却不会

而且,这种多发射极三极管来说,只要有一个输入是低电平,那么三极管就导通,为此,我们先贴上TTL与非门的电路图:

当A,B均为高电平时, 都导通,那么A, B的电位就会被钳位,而又由于 相当于经过一个20kΩ的电阻接地,相当于输入高电平,那么我们只需要关心 就好了:

好的,下面我们分析(1):悬空相当于接高电平,那么即两个输入端均为高电平,

均导通,

被钳位在1.4V

(2)当

接了0.2V低电平时,

均截止,那么

就等于0.2V

(3)

接高电平时和(1)一样,显示为1.4V

(4)经51Ω接地,相当于输入低电平,显示0.2V

(5)经1kΩ电阻接地相当于输入高电平,显示1.4V