以下所有历程都是用Quartus II工具编写的verilog程序,主要是用来描述数字逻辑中的电路,可以实际拿来使用,都是我经过测试的!

1、非门

2、三线—八线译码器

3、四选一数据选择器

4、四位二进制数据比较器

5、四位数据比较器

6、数码管七段码译码器

7、D触发器

8、八位移位寄存器

9、可控移位寄存器

10、四位二进制模十计数器

11、三位八进制计数器

12、八位二进制赋值语句

13、状态机实现正方形四段笔按顺序点亮

14、频率计

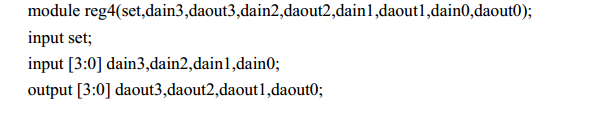

15、四位二进制锁存器

16、带使能端、清零端输入和进位输出端的十进制计数器

17、分频器、分频得到 1KHz 信号

18、数码管动态扫描显示