四值逻辑系统

逻辑运算符

与:&& a && b

或:|| a || b

非:! ! a

位运算符

与:& a & b

或:| a | b

非:~ ~a

异或:^ a ^ b

常用的可综合关键字

| module | endmodule | input | wire | case | posedge | or |

| if | else | output | reg | default | negedge | always |

| begin | end | inout | parameter | endcase | assign | |

输入只能被定义成wire型;

在assign里赋值的是wire型变量;

在always里赋值的是reg型变量;

代码:

module xuanzeqi(a,b,o1);

input a,b ;

output reg o1 ;

always @(*)begin

if(a) o1 = b;

else o1 = 1'b0;

end

endmodule电路:

锁存器、选择器和D触发器

择器

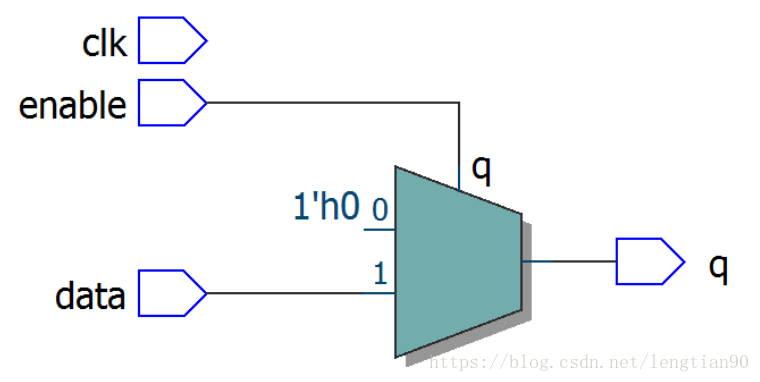

代码:

module suocunqi(data,q,enable);

input data,enable ;

output reg q ;

always @(*)begin

if(enable) q = data;

else q = 1'b0;

end

endmodule当enable = 1时,将data输入到q;当enable = 0时,将1'b0输入到q;满足选择器定义,生成选择器。

电路:

D触发器

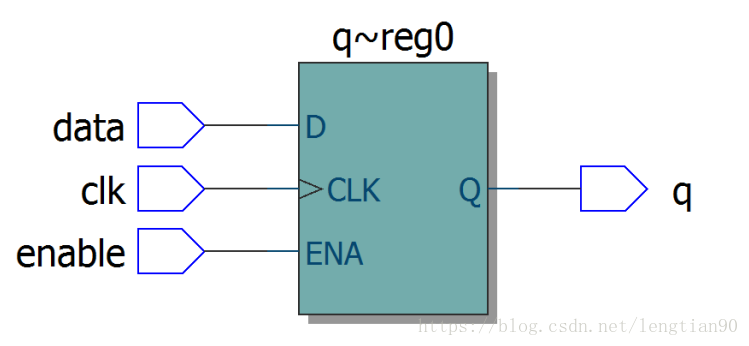

代码:

module suocunqi(clk,data,q,enable);

input clk,data,enable ;

output reg q ;

always @(posedge clk)begin

if(enable) q <= data;

// else q <= q;

end

endmodule无论是否有else语句,上升沿来临且enable = 1,将data输入到q;其他时候,q保持不变,符合带使能位的D触发器定义,生成D触发器。

电路:

组合逻辑反馈环路

摩尔(Moore)状态机:输出只与状态有关而与输入无关;

米里(Mealy)状态机:输出与状态和输入都有关系;