案例:计数器

功能:让LED每500ms状态翻转一次

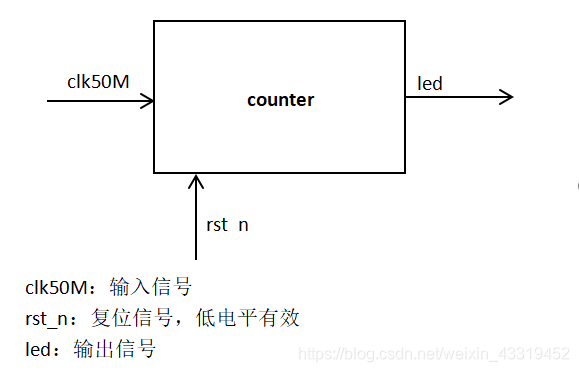

1.设计定义–>分析,将问题转化控制电路

分析:FPGA系统时钟50MHz,对应周期20ns,计数次数=50ms/20ns=25_000_000

rst_n低电平复位,高电平计数,计数记到25_000_000,计数清零,led状态翻转。

计数器模块设计

2.综合

计数器模块.v

module counter(clk50M,rst_n,led);

/*

功能:让LED每500ms状态翻转一次

分析:FPGA系统时钟50MHz,对应周期20ns,计数次数=50ms/20ns=25_000_000

rst_n低电平复位,高电平计数,计数记到25_000_000,计数清零,led状态翻转

*/

input clk50M;//输入信号

input rst_n;//复位信号,低电平有效

output led;//输出信号

reg led;

reg [24:0]cnt;

always @(posedge clk50M or negedge rst_n)

begin

if(rst_n == 1'b0)

begin

cnt<=25'd0;

led<=1'b1;

end

else

begin

cnt<=cnt+1;

if(cnt == 25'd25_000_000)

begin

cnt<=25'd0;

led=~led;

end

end

end

endmodule

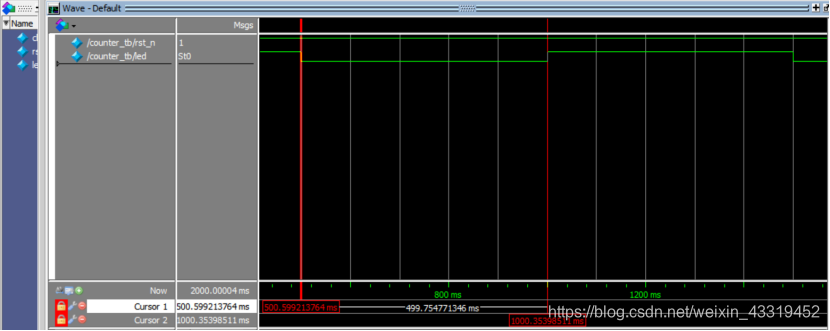

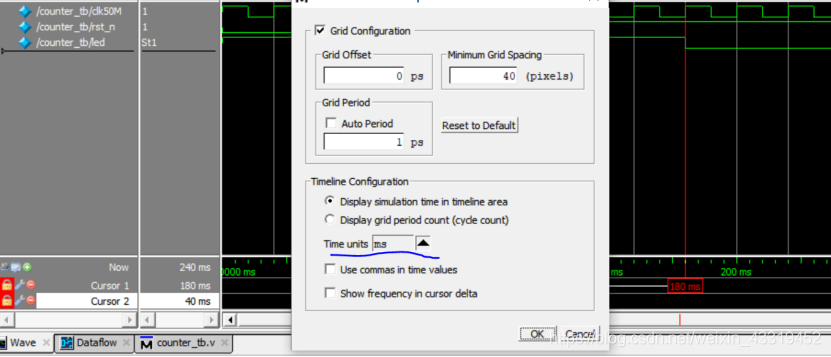

计数器模块仿真

`timescale 1ns/1ns

`define clock_period 20 //频率50MHz,周期20ns,

module counter_tb;

reg clk50M,rst_n;//输入信号

wire led;//输出信号

counter counter1(//端口关联激励信号

.clk50M(clk50M),

.rst_n(rst_n),

.led(led)

);

initial

begin

rst_n=0;clk50M=1;

#(`clock_period*2) rst_n=1;

#2000_000_000 $stop;

end

always//时钟周期20ns,每10ns翻转一次

#(`clock_period/2) clk50M=~clk50M;

endmodule

3.布局布线

4.时序仿真与功能仿真

5.编程下载和在线测试