##提醒自己

本篇博客摘自《FPGA设计技巧与案例开发详解》,博客中的规范会不断地改进,将作为笔者今后Verilog HDL代码编写规范

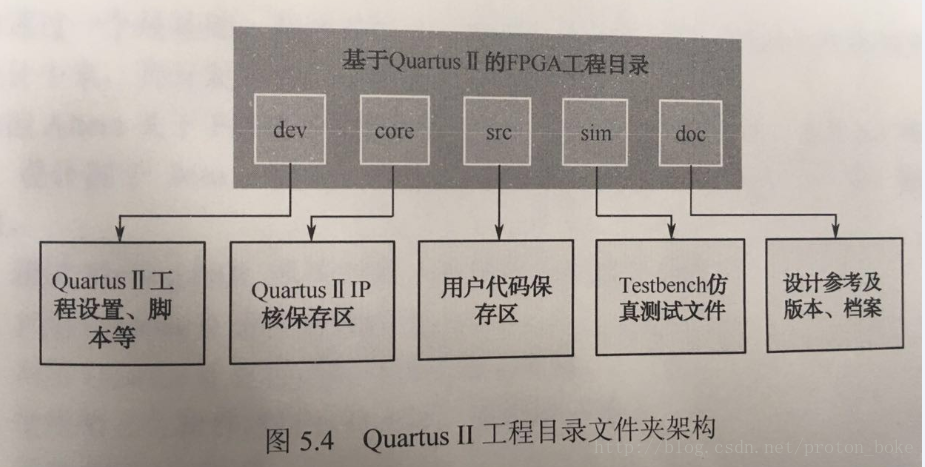

##Quartus ΙΙ工程目录文件夹的定制:

每一个Quartus ΙΙ的工程被分为5个部分:

- 一般dev自工程建立后就不用再管

- 而core需要用户在设计时注意将Quartus ΙΙ IP核保存在里面

- src是用户最关心的地方,每一个新建移植的Verilog HDL源代码都被放在里面

- sim主要存放modelsim仿真测试工程

- 而core需要用户在设计时注意将Quartus ΙΙ IP核保存在里面

- doc主要是关于设计的档案,参考等信息,也有版本修改、升级以及团队合作需要完善的内容

##Verilog HDL文件头编写规范:

无论是一个Teamwork,还是一个工程师的设计,在HDL的编写中难免会遇到版本修改、更新问题,这就需要一个规范的文件头

- 设计者

- 模块功能

- 设计时间、版本记录

##Module列表编写规范:

- 无论是否进行仿真,module前必须写’timescale 1ns/1ns这一条语句的作用为testbench要用到的仿真时间单位和精度的设定,虽然这在Quartus ΙΙ中没有直接用到。Testbench规定必须在仿真文件中指定时间精度,否则默认为1ps。笔者一般在新建Verilog HDL 或Testbench的文件时,直接添加’timescale 1ns/1ns,这个时间长度比较常用,且能满足大部分情况的要求

- 全局时钟及复位写在最前面,分别命名为CLK及RST(多个时钟可以用CLK_50,CLK_24区分)

- 相关的信号根据时钟、复位、使能、控制端的顺序规划在一起,同时必须有注释

- 列表中的输入输出信号采用大写,中间变量采用小写

- 所有的输入输出、信号命名等,都必须严格对齐

- 所有信号注释必须严格对齐

- 为了解决不同编辑器的兼容,TAB用4个空格来代替

- 禁止使用中文注释

##always模块编写规范:

每一个always模块,都必须自成体系

- 每一个always,都必须有功能介绍

- 相关的寄存器定义,必须卸载当前always模块前

- 相关的宏定义,也必须写在当前always模块前

- 所有的if,else都必须对齐

- else必须写完整

- 信号位宽必须写完整

- 每一个逻辑符号前后各空一格

- 单/总线连出(delay_1s),写在always模块后

##Moudle的例化编写规范:

**对于Moudle的例化,相当于C语言中的调用函数,更需要注意信号列表的格式 **

- 对每一个Moudle在例化前必须有moudle的功能说明

- module的例化名采用u_xx的格式

- 信号列表及wire都必须完全对齐

- 相关信号必须写在一起,并且有注释

##Testbench激励文件的编写:

**注:Testbench不同于Verilog HDL的地方时没有输入输出类的信号定义,每一个激励都是在当前文件中生成的。而Testbench中的module信号类表是当前文件需要输出的信号 **

- Tesrbench文件头的添加

- 添加时钟、复位发生器电路

- 例化目标仿真电路

- 激励信号的初始化

- modelsim仿真的进程设计,系统复位→系统初始化→系统激励