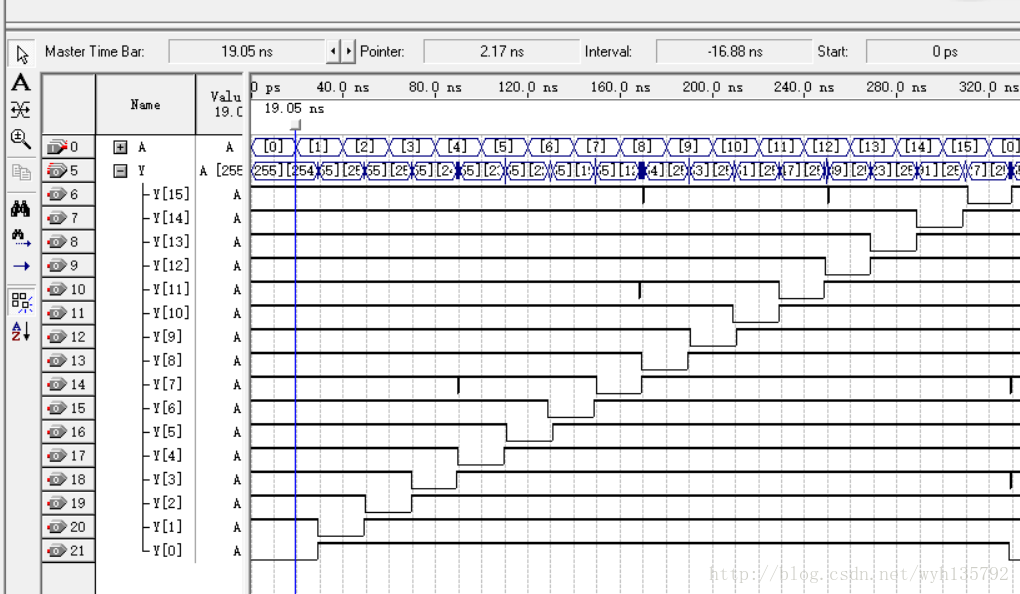

实验一:用Verilog实现4-16线译码器

module YIMAQI (Y,A);

input[3:0] A;

wire[3:0] A;

output[15:0] Y;

reg[15:0] Y;

reg s;

always@ (A)

begin

case(A)

4'b0000:Y<=16'b1111111111111110;

4'b0001:Y<=16'b1111111111111101;

4'b0010:Y<=16'b1111111111111011;

4'b0011:Y<=16'b1111111111110111;

4'b0100:Y<=16'b1111111111101111;

4'b0101:Y<=16'b1111111111011111;

4'b0110:Y<=16'b1111111110111111;

4'b0111:Y<=16'b1111111101111111;

4'b1000:Y<=16'b1111111011111111;

4'b1001:Y<=16'b1111110111111111;

4'b1010:Y<=16'b1111101111111111;

4'b1011:Y<=16'b1111011111111111;

4'b1100:Y<=16'b1110111111111111;

4'b1101:Y<=16'b1101111111111111;

4'b1110:Y<=16'b1011111111111111;

4'b1111:Y<=16'b0111111111111111;

endcase

end

endmodule仿真结果如下:

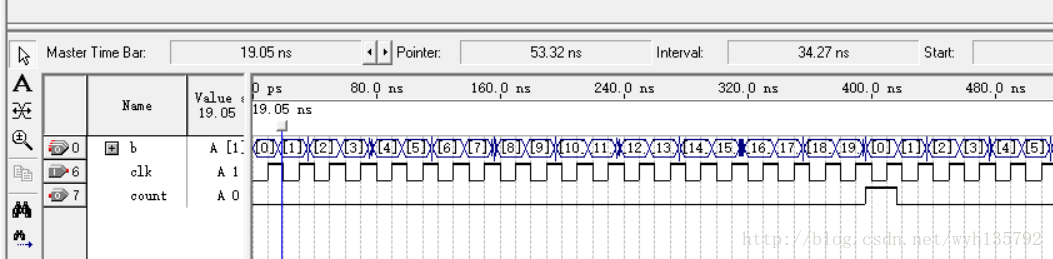

实验二:用Verilog实现12进制计数器

module JINZHI(clk,count,b);

input clk;

output count;

reg count;

output[3:0] b;

reg[3:0] b;

reg [3:0] a;

always@(posedge clk)

begin

if(a==11)

begin

a=0;

count=1;

end

else

begin

count=0;

a=a+1;

end

b=a;

end

endmodule仿真图如下:

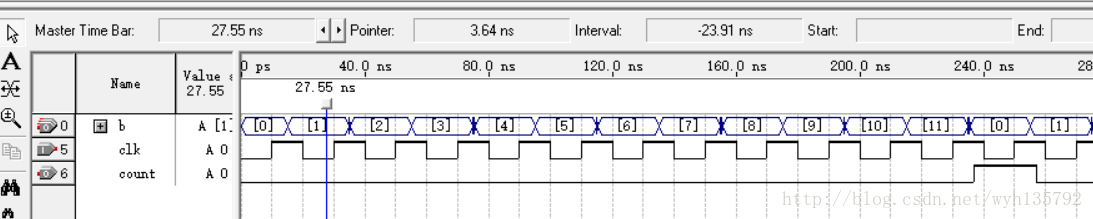

实验三:用Verilog实现20进制计数器

module JINZHI2(clk,count,b);

input clk;

output count;

reg count;

output[4:0] b;

reg[4:0] b;

reg [5:0] a;

always@(posedge clk)

begin

if(a==19)

begin

a=0;

count=1;

end

else

begin

count=0;

a=a+1;

end

b=a;

end

endmodule仿真图如下:

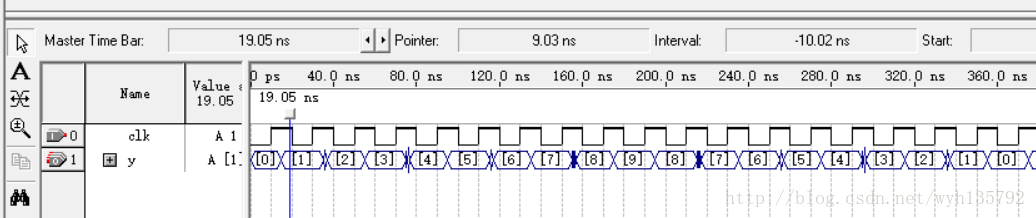

补充:用Verilog设计0-9循环计数器

module VE(clk,y);

input clk;

output [3:0] y;

reg[3:0] y;

reg[3:0] count;

reg[3:0] count1;

always@(posedge clk)

begin

if(count1==0)

count=count+1;

if(count==10)

begin

count1=count;

count=count-1;

end

if(count1==10)

count=count-1;

if(count==0)

count1=0;

y=count;

end

endmodule

仿真图如下: