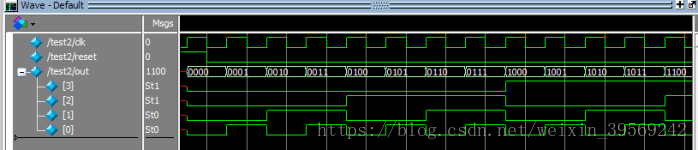

- 完成课本例题4.12,进行综合和仿真(包括功能仿真和时序仿真),查看仿真结果,将Verilog代码和仿真波形图整理入实验报告。

功能文件:

module shiyan1(out,reset,clk);

input reset,clk;

output reg[3:0] out;

always @(posedge clk)

begin

if(reset)

out<=0;

else

out<=out+1;

end

endmodule

测试文件

`timescale 1ns/1ns

module test2();

reg clk,reset;

wire[3:0] out;

parameter DELY=100;

shiyan1 U1(out,reset,clk);

always #(DELY/2) clk=~clk;

initial

begin clk =0;reset=0;

#DELY reset=1;

#DELY reset=0;

#(DELY*20) $finish;

end

initial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);

endmodule

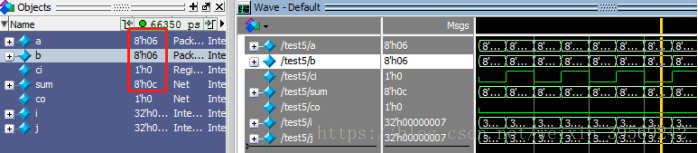

- 课后习题4.1,用Verilog设计一个8位加法器,进行功能仿真,查看综合和仿真结果,将Verilog代码和仿真波形图整理入实验报告。

功能代码:

module a(a,b,ci,sum,co);

input [7:0] a,b;

input ci;

output [7:0] sum;

output co;

reg sum,co;

assign {co,sum}=a+b+ci;

Endmodule

测试代码:

`timescale 1ns/1ns

module test5();

reg[7:0] a,b;

reg ci;

wire[7:0] sum;

wire co;

integer i,j;

a U4(a,b,ci,sum,co);

always #10 ci=~ci;

initial begin a=0;b=0;ci=0;

for(i=1;i<16;i=i+1)

#10 a=i;

end

initial

begin for(j=1;j<16;j=j+1)

#10 b=j;

end

initial

begin

#160 $finish;

end

Endmodule