Verilog HDL 有限状态机的设计

【转自教科书】

有限状态机根据输出逻辑的不同可以分为Mealy状态机和Moore状态机,两者设计方法基本一致,唯一不同的是输出结果是否取决于输入信号。

Mealy 状态机:输出结果不仅取决于当前状态,还与输入信号有关;

Moore 状态机:输出结果只取决于系统当前状态。

有限状态机可分为三个主要变量:现状态、次状态和输出结果。

有限状态机的设计,根据使用的Always过程块的不同而分为:

【一段式】上述三个状态都放在一个always过程快中描述。而这种方法包含所有的逻辑设计,使得整体设计变得复杂增加设计难度。【两段式】把现状态用一个always过程块描述,次状态和输出结果用另一个always过程块描述。

【三段式】分别把三个变量用三个always过程块分开描述。

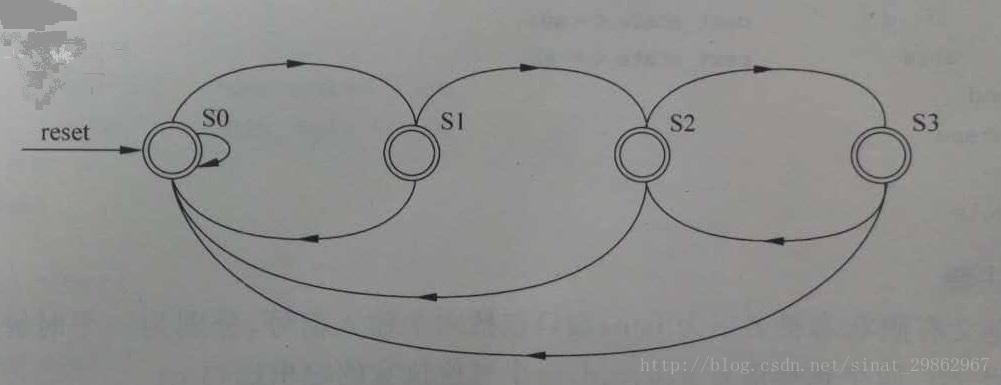

现对下图进行两段式和三段式状态机设计:

两段式设计:

module state_ji(clk,rst,q,a,b,c,d,state,nextstate);

input clk,rst,a,b,c,d;

output q,state,nextstate;

reg[2:0] q;

reg[1:0] state,nextstate;

parameter s0=2'b00, s1=2'b01, s2=2'b10, s3=2'b11;

always@(posedge clk)

begin

if(rst) state <= s0;

else state <= nextstate;

end

/*********************************************/

//两段式状态机:把现状态写进一个always模块,

// 次状态和输出值写进一个always模块

always@(state or a or b or c or d)

begin

case(state )

s0:begin

q <= 3'b001;

if(a) nextstate <= s1;

else nextstate <= s0;

end

s1:begin

q <= 3'b010;

if(b) nextstate <= s2;

else nextstate <= s0;

end

s2:begin

q <= 3'b100;

if(c) nextstate <= s3;

else nextstate <= s0;

end

s3:begin

q <= 3'b111;

if(d) nextstate <= s0;

else nextstate <= s2;

end

endcase

end

endmodule

三段式设计:

module state_ji(clk,rst,q,a,b,c,d,state,nextstate);

input clk,rst,a,b,c,d;

output q,state,nextstate;

reg[2:0] q;

reg[1:0] state,nextstate;

parameter s0=2'b00, s1=2'b01, s2=2'b10, s3=2'b11;

//三段式状态机:把现状态、次状态、输出值分别写进三个always模块

always@(posedge clk)

begin

if(rst) state <= s0;

else state <= nextstate;

end

always@(state or a or b or c or d)

begin

case(state )

s0:begin

if(a) nextstate <= s1;

else nextstate <= s0;

end

s1:begin

if(b) nextstate <= s2;

else nextstate <= s0;

end

s2:begin

if(c) nextstate <= s3;

else nextstate <= s0;

end

s3:begin

if(d) nextstate <= s0;

else nextstate <= s2;

end

endcase

end

always@(state)

begin

case(state)

s0: q = 3'b001;

s1: q = 3'b010;

s2: q = 3'b100;

s3: q = 3'b111;

endcase

end

******************************************************************/

endmodule